| Похожие рефераты | Скачать .docx |

Реферат: Логические элементы

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

АНГАРСКАЯ ГОСУДАРСТВЕННАЯ ТЕХНИЧЕСКАЯ АКАДЕМИЯ

ФАКУЛЬТЕТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ

КАФЕДРА ПРОМЫШЛЕННОЙ ЭЛЕКТРОНИКИ И ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ ТЕХНИКИ

РЕФЕРАТ

по курсу: Импульсная техника

тема: Логические элементы

Выполнил

Студент гр. ПЭ-98 -1

ФИРСОВ Д.В.

Приняла:

КУРЧЕНКО О.А.

Должность: ст преподаватель

Подпись:____________

Оценка:

Ангарск 2001 г.

Содержание

Введение.. 2

Параметры логических интегральных микросхем... 3

Диодно-транзисторная логика.. 3

Транзисторно-транзисторные логические элементы... 4

Базовые логические элементы эмиторно-связной логики.. 8

Принцип действия и функциональные возможности БЛЭ ЭСЛ. 10

СХЕМОТЕХНИКА БЛЭ КМОП-ТИПА.. 11

БЛЭ Интегрально-инжекционной логики.. 13

Список используемой литературы... 15

Введение

В большинстве современных ЭВМ и цифровых устройствах различного назначения обработка информации происходит с помощью двоичного кода, когда информационные сигналы могут принимать только два значения: 1 и 0. Операции по обработке двоичной информации выполняют логические элементы.

Используя набор логических элементов, выполняющие элементарные логические операции И, ИЛИ, НЕ, можно реализовать в двоичном коде любую сложную логическую функцию.

Параметры логических интегральных микросхем

1 Входное U1 вх и выходное U1 вых напряжение логической единицы – значение высокого уровня напряжения на входе и выходе микросхемы;

2 Входное U0 вх и выходное U0 вых напряжение логического нуля – значение низкого уровня напряжения на входе и выходе микросхемы;

3 Входной I1 вх и выходной I1 вых токи логической единицы, входной I0 вх и выходной I0 вых токи логического нуля;

4 Логический период сигнала ![]() , пороговое напряжение Uпор вх

– напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

, пороговое напряжение Uпор вх

– напряжение на входе, при котором состояние микросхемы изменяется на противоположное;

5 Входное сопротивление логической ИМС – отношение приращения входного напряжения к приращению входного тока (различают R0 вх и R1 вх ), выходное сопротивление – отношение приращения выходного напряжения к приращения выходного тока (различают R0 вых и R1 вых );

6 Статическая помехоустойчивость – максимально допустимое напряжение статической помехи по высокому U1 пом и низкому U0 пом уровням входного напряжения, при котором еще не происходят изменения уровня выходного напряжения микросхемы;

7 Средне потребляемая мощность Pпотр ср = (P0 потр + Р1 потр )/2 , где P0 потр и Р1 потр – мощности, потребляемые микросхемой в состоянии соответственно логического нуля и единицы на выходе;

8 Коэффициент объединения по входу Коб , показывающий, какое число аналогичных логических ИМС можно подключить к входу данной схемы, и определяющий максимальное число входов логической ИМС;

Коэффициент разветвления по входу Кразв , показывающий какое количество аналогичных нагрузочных микросхем можно подключить к выходу данной ИМС, и характеризующий нагрузочную способность логической ИМС.

Диодно-транзисторная логика

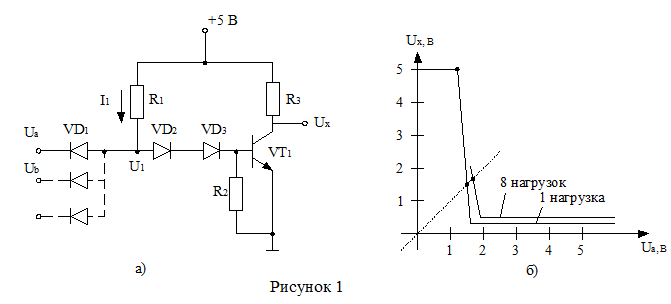

Одним из первых семейств цифровой логики мы рассмотрим диодно-транзисторную логику. Основная схема ДТЛ приведена в соответствии с рисунком 1а. Если отбросит часть схемы, изображенную пунктиром, схема превращается в инвертор, и по ней можно построить передаточную характеристику Ux

от Ua

. Если напряжение на входе А равно 0, то диод VD1

смещен в прямом направлении и напряжение U1

равно +0,6 В. Эта величина недостаточна для открывания диодов VD2

и VD3

и перехода база-эмиттер транзистора VТ1

. Поэтому ток i1

течет через диод VD1

, источник напряжения Ua

и на землю. Транзистор VТ1

закрыт, при этом Ux

= +5 В. Если Ua

увеличивается, то U1

также растет до тех пор, пор пока не достигнет 1,2 В. При этом U1

= 1,8 В. В этот момент VD2

, VD2

, VТ1

открываются и ток i1

течет через транзистор VТ1

и переводит его в насыщение. Дальнейшее увеличение напряжение Ua

запирает диод VD1

. но не может повлиять на величину U1

или состояние транзистора VТ1

. Это относительно резкое изменение величины напряжение Ux

от +0,5 В до величены на насыщенном транзисторе Uкэ нас

приведено, в соответствии с рисунком 1б. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны

Одним из первых семейств цифровой логики мы рассмотрим диодно-транзисторную логику. Основная схема ДТЛ приведена в соответствии с рисунком 1а. Если отбросит часть схемы, изображенную пунктиром, схема превращается в инвертор, и по ней можно построить передаточную характеристику Ux

от Ua

. Если напряжение на входе А равно 0, то диод VD1

смещен в прямом направлении и напряжение U1

равно +0,6 В. Эта величина недостаточна для открывания диодов VD2

и VD3

и перехода база-эмиттер транзистора VТ1

. Поэтому ток i1

течет через диод VD1

, источник напряжения Ua

и на землю. Транзистор VТ1

закрыт, при этом Ux

= +5 В. Если Ua

увеличивается, то U1

также растет до тех пор, пор пока не достигнет 1,2 В. При этом U1

= 1,8 В. В этот момент VD2

, VD2

, VТ1

открываются и ток i1

течет через транзистор VТ1

и переводит его в насыщение. Дальнейшее увеличение напряжение Ua

запирает диод VD1

. но не может повлиять на величину U1

или состояние транзистора VТ1

. Это относительно резкое изменение величины напряжение Ux

от +0,5 В до величены на насыщенном транзисторе Uкэ нас

приведено, в соответствии с рисунком 1б. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны

0≤U0 ≤1.2 B

1.5≤U1 ≤5 В

Практически U0 обычно меньше 0,4 В, а U1 очень близко к 5 В, что обеспечивает хороший шумовой запас по постоянному току.

Если на вход подано напряжение, соответствующее логической 1, то диод VD1 смещен в обратном направлении и, следовательно, потребляет минимальную мощность с выхода предыдущей схемы. Однако если на входе поддерживается напряжение логического 0, то ток i1 должен течь из входной клеммы элемента через насыщенный транзистор на землю. Это соответствует одной единичной нагрузке. Если к одному выходу подсоединено n входов, то насыщенный транзистор должен пропускать ток, в n раз больше чем i1 . Если n увеличивается, то будет расти и напряжение Ua , что эквивалентно увеличению напряжения выходного транзистора. Этот эффект приведен в соответствии с рисунком 1б, где передаточная характеристика изображена для случая одной выходной единичной нагрузки и для случая восьми единичных нагрузок (максимально допустимое количество для базового элемента ДТЛ).

Если к схеме, в соответствии с рисунком 1а, добавить второй диод для получения входа Ub , то напряжение Ux будет соответствовать логической 1, если хотя бы один из входов будет в состоянии логического нуля. Логический нуль на выходе можно получить только в том случае, если на обоих входах присутствует напряжение логической единице, т.е. логическая операция выполняемая данной схемой имеет вид:

Х = ![]()

Что соответствует операции НЕ-И. Добавлением дополнительных диодов для расширения объема входа число входов в базовом элементе ДТЛ НЕ-И может доведено до 20.

Если выходы двух (и более) ДТЛ элементов НЕ-И соединены вместе, результирующая схема осуществляет операцию И на выходов элементов НЕ-И. Из схемы видно, что если хотя бы на одном из двух выходов присутствует напряжение логического нуля, то общий выход находится в состоянии логического нуля. Если оба выхода элемента НЕ-И в состоянии логической 1, то на выходе – тоже логическая единица. Такое соединение называется проводным И. Выходная нагрузочная способность такой схемы должна быть уменьшена на одну единичную нагрузку для каждого дополнительного выхода проводном соединении, так как следует учитывать возможность шунтирования общего выхода коллекторными сопротивлениями транзисторов, выходные напряжения которых соответствуют логической единицы.

Задержка передачи для типичного элемента ДТЛ составляет 30 нс. Это сравнительно большая величена, во многих случаях оказывается вполне приемлемой.

Семейство диодно-транзисторной логики содержит элементы И, ИЛИ, НЕ-И, НЕ-ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ. Это семейство удобно для конструктора, так как имеет большой набор различных элементов. Большинство схем содержит несколько незадействованных входных клемм, которые рекомендуется соединять с положительным полюсом источника питания или заземлять. Это увеличивает помехозащищенность и уменьшает время задержки передачи.

Транзисторно-транзисторные логические элементы

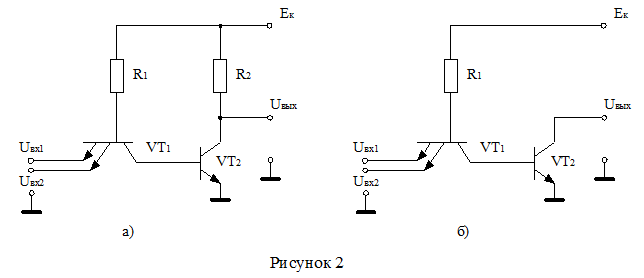

Простейший базовый элемент ТТЛ, в соответствии с рисунком 2а, за счет использования многоэмиттерного транзистора, объединяющего свойства диода и транзисторного усилителя, позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы.

Базовый элемент ТТЛ также выполняет логическую операцию И-НЕ. При низком уровне сигнала (логический 0) хотя бы на одном из выходов многоэмиттерного транзистора VT1 последний находится в состоянии насыщения, а VT2 закрыт. На выходе схемы существует высокий уровень напряжения (логическая единица). При высоком уровне сигнала на всех входах VT1 работает в активном инверсном режиме, а VT2 находится в состоянии насыщения. Описанный здесь базовые элемент ТТЛ, несмотря на прощеную технологию изготовления, не нашел широкого применения из-за низкой помехоустойчивости, малой нагрузочной способностью и малого быстродействия при работе на емкостную нагрузку. Его целесообразно использовать лишь при разработке микросхем с открытым коллектором, в соответствии с рисунком 2б, для включения внешних элементов индикации, когда не требуется высокая помехоустойчивость и большая нагрузочная способность.

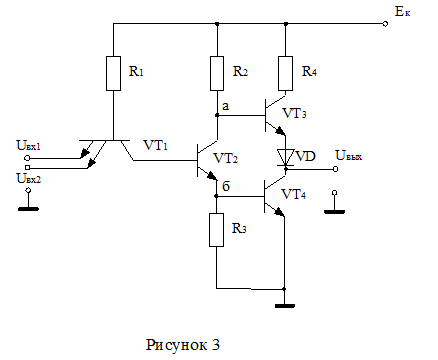

Улучшенными параметрами по сравнения с предыдущей схемой обладает базовый элемент ТТЛ, в соответствии с рисунком 3. Однако объединение выходов в схеме не допустимо.

Улучшенными параметрами по сравнения с предыдущей схемой обладает базовый элемент ТТЛ, в соответствии с рисунком 3. Однако объединение выходов в схеме не допустимо.

В статических режимах работы схемы, в соответствии с рисунком 3, VT4 повторяет состояние VT2 . При запирании VT2 база транзистора VT4 через резистор R3 подключается к “земле”, чем и обеспечивается закрытое состояние VT4 .

Если VT2 насыщен, то через базуVT4 протекает ток:

Iб4 = Iэ2 – IR 3 = [(Eк - Uкэн2 – Uбэ4 )/a2 ·R2 ] – (Uбэ4 /R3 )

Для транзисторов, выполненных по интегральной технологии, обычно принимают Uкэн = 0,2 В, Uбэ = 0,8 В.

Для обеспечения режима насыщения VT4 при закрытых транзисторе VT3 и диоде VD необходимо выполнить условие:

Iб4 ·В4 ≥ Iкн = n·I0 вх нагр

Где: n – число нагрузочных ТТЛ-схем, подключенных к выходу рассматриваемой схемы;

I0 вх нагр – входной ток нагрузочной ТТЛ-схемы.

Положив в данное выражение знак равенства, можно определить нагрузочную способность данной схемы, т.е. максимальное число нагрузочных схем, при котором транзистор VT4 еще работает в режиме насыщения:

nmaz = Iб4 ·В4 / I0 вх нагр

Состояние VT3 в статических режимах работы схемы, в соответствии с рисунком 3, всегда противоположно состояниюVT4 , а следовательно, VT2 . При насыщенном VT4 транзистор VT3 закрыт. Диод VD повышает порог отпирания VT3 , обеспечивая его закрытое состояние при насыщенном транзисторе VT4 . Действительно:

Uбэ3 = Uкэн2 + Uбэ4 – Uкэн4 – Uд ≈ Uбэ4 - Uд < Uпор3

Так как типичны значения: Uбэ4 = 0,8 В; Uд = 0,7В; Uпор = 0,6В.

Помехоустойчивость ТТЛ-схем по высокому и низкому уровням входного напряжения различны, т.е. U0 пом ≠ U1 пом .

ТТЛ-схема более чувствительна к помехе U0 пом , которая накладывается на сигнал U0 вх и вызывает ложное переключение схемы (U0 пом < U1 пом ). Схема, в соответствии с рисунком 3, считается подключенной, если под действием помехи U0 пом открываются транзисторы VT2 и VT4 , для отпирания которых требуется двойное пороговое напряжение Uпор2 +Uпор4 ≈ 2·Uпор . Тогда условие сохранения первоначального состояния схемы при действии помехи можно записать как:

U0 вх + U0 пом + Uкэн1 ≤ 2Uпор

Откуда найдем:

U0 пом ≤ 2Uпор - U0 вх - Uкэн1

Приняв U0 вх = 0,2 В; Uпор = 0,6 В; Uкэн = 0,2 В, получим U0 пом ≤ 0,6 В

При определении U1 пом схема считаются переключенной, если открывается закрытый переход база – эмиттер многоэмиттерного транзистора VT1 . В режиме логическое единицы на входе потенциал базы транзистора VT1 относительно “земли” равен сумме напряжений на открытых переходах база-коллектор VT1 и база-эмиттер VT2 и VT4 , т.е. Uб1 = Uбк1 + Uбэ2 + Uбэ4 = 2,14 В. Тогда напряжение на закрытом переходе база-эмиттер VT1 : Uбэ1 = Uб1 – U1 вх . Принимая U1 вх = 3,6 В, будем иметь Uбэ1 = -1,2 В.

Напряжение помехи, при котором транзистор VT1 можно считать открытым, U1 пом = Uбэ1 – Uпор = -1,2 –0,6 = -1,8 В.

Помехоустойчивость ТТЛ-схемы со сложным инвертором по логическому нулю выше, а по логической единице, чем ТТЛ-схемы, в соответствии с рисунком 2а.

Быстродействие ТТЛ-схем определяется в основном переходными процессами при переключении транзисторов, а также зарядом паразитной нагрузочной емкости Сн , которая представляет собой суммарную емкость нагрузочных ТТЛ-схем. В схеме, в соответствии с рисунком 2а, заряд емкости Сн происходит с большой постоянной времени через коллекторный резистор R2 , что ухудшает быстродействие схемы.

В ТТЛ-схеме со сложным инвертором постоянная заряда нагрузочной емкости существенно уменьшается, так как емкость Сн заряжается через выходное сопротивление Rвых 3 << R2 транзистора VT3 , работающего в схеме эмиттерного повторителя. За счет этого ТТЛ-схема со сложным инвертором имеет большее быстродействие по сравнению с ТТЛ-схемой, в соответствии с рисунком 2а.

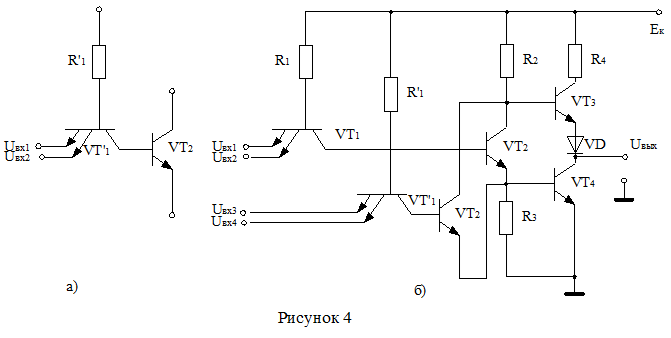

Схема базового элемента со сложным инвертором лежит в основе разработок большинства серий интегральных микросхем ТТЛ. Для расширения функциональных возможностей элемента промышленностью выпускают так называемые расширители по ИЛИ, в соответствии с рисунком 4а, которые представляют собой часть структуры ТТЛ и подключаются к точкам а и б элемента, в соответствии с рисунком 2. Полученная при этом логическая схема, в соответствии с рисунком 4б, реализует функцию И-ИЛИ-НЕ. На выходе схемы устанавливается логический нуль, если на всех выходах VT1 поступают сигналы, соответствующие логической единице. При всех остальных комбинациях сигналов на выходах схемы выходное напряжение соответствует логической единице.

Повысить быстродействие ТТЛ-схем можно, применив в схеме базового элемента, в соответствии с рисунком 3, вместо обычных транзисторов транзисторы Шотки, работающие в активном режиме. Тем самым сокращается время переключения транзисторов схемы за счет исключения времени рассасывания носителей заряда в базе транзистора при их запирании. Логические ИМС, выполненные на базе транзисторов Шотки, называются микросхемами ТТЛШ.

Недостатком ТТЛ-схем является сильная генерация токовых помех по цепи питания, обусловленных броском тока через сложный инвертор при переключении схемы из состояния логического нуля в единицу. После запирания VT2 транзистор VT3 откроется раньше, чем закроется насыщенный транзистор VT4 , так как для выхода VT4 из режима насыщения потребуется некоторое время для рассасывания неосновных носителей в базе. В результате в течении некоторого промежутка времени оба транзистора VT3 и VT4 открыты и по цепи, состоящей из элементов Ек , VT3 , VD и VT4 , протекает ток, значение которого определяется эмитторным током VT3 , находящегося в активном режиме:

Iпом max = Iэ3 = Iб3 · В + Iб3 = Iб3 (В+1)

Так как базовый ток транзистор равен:

![]()

То:

Iпом

max

=

Iпом

max

= ![]()

Для устранения влияния токовых помех, генерируемых данной микросхемой, на работу соседних микросхем рекомендуется включать высокочастотные блокировочные конденсаторы между шиной питания и землей.

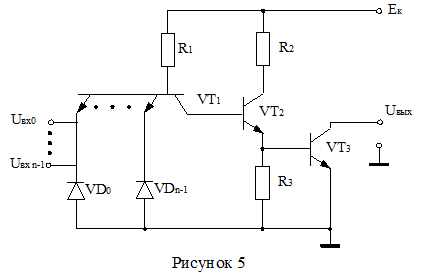

Элемент И – НЕ с открытым коллектором предназначен для согласования логических схем с внешними исполнительными и индикаторными устройствами, например светодиодными индикаторами, лампочки накаливания, обмотки реле и т.д. Его отличие от ранее рассмотренного заключается в выполнении выходного усилителя мощности по однотактной схеме без собственного резистора. Принципиальная электрическая схема такого элемента приведена в соответствии с рисунком 5.

В данном элементе также отсутствует цепь нелинейной коррекции. Это связано с тем, что элемент ставится на выходе логического устройства и к нему в меньшей степени предъявляются требования квантования сигнала. Обычно выходной транзистор VT3 схемы выполняется с большими допустимыми значениями коллекторного тока и напряжением, чем обычный элемент.

В отличии от стандартных, элементы ТТЛ с открытым коллектором допускают параллельное включение выходных выводов. При этом относительно выходных сигналов каждого элемента реализуется логическая операция И: Uвых = Uвых 1 Uвых 2 ... Uвых n

Это позволяет решить две задачи:

1. Упростить схему проектируемого устройства за счет исключения дополнительных элементов, реализующих операцию И;

2. Обеспечить работу нескольких выходов на общую шину, т.е. реализовать режим работы с разделением информации по времени.

Базовые логические элементы эмиторно-связной логики

Причиной появления БЛЭ ЭСЛ явилось желание повысить быстродействие цифровых устройств. Это желание привело к использованию в них совершенно отличного от ТТЛ схемотехнического решения. Как было показано выше, основными причинами инерционности ключей, выполненных на биполярных транзисторах, являются время рассасывания неосновных носителей из его базовой области и постоянная времени перезарядки выходной емкости. Если время рассасывания транзистора при работе последнего в активной области может быть полностью исключено, то от влияния постоянной времени перезаряда выходной емкости транзистора полностью избавиться не представляется возможным. Это влияние можно лишь уменьшить путем увеличения коллекторного тока транзистора, как это было сделано в БЛЭ ТТЛ серии 513. При неизменном постоянном токе перезарядка выходной емкости транзистора, длительность его перехода из состояния, классифицируемого как логического 0, в состояние, классифицируемого как логической 1 и обратно может быть уменьшено только за счет уменьшения логического перепада. Такое решение позволяет повысить быстродействие. Однако дается оно за счет снижения помехоустойчивости БЛЭ, что требует создания схем при прочих равных условиях менее подверженных действию помех. Этот принцип и использован при построении БЛЭ ЭСЛ.

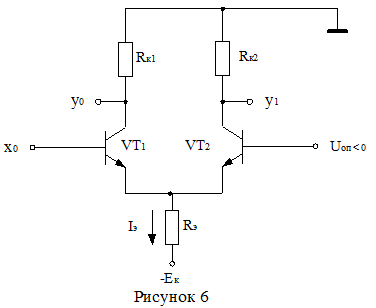

Основой БЛЭ ЭСЛ является токовый ключ, выполненный на двух транзисторах, в соответствии с рисунком 6. На базу одного из них, например VT2 , подано некоторое постоянное опорное напряжение Uоп . Изменение напряжения подаваемого на вход х0 ниже или выше Uоп приводит к перераспределению постоянного тока Iэ , заданного токостабилизирующим резистором Rэ , между транзисторами VT1 и VT2 . При этом транзисторы не попадают в режим насыщения и, следовательно, в ключе принципиально отсутствует интервал рассасывания их неосновных носителей. Таким образом, особенностью БЛЭ ЭСЛ является постоянство потребляемого тока независимо от выходного сигнала ключа.

Эта особенность выгодно отличает БЛЭ ЭСЛ от БЛЭ ТТЛ, в котором момент переключения ток, потребляемый элементом, резко возрастет, создавая внутренние помехи, ухудшающие помехозащищенность цифрового устройства.

Не трудно заметить, что общей шиной является шина +Uп

, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме токового ключа так же, как и в схемах ТТЛ, реализован принцип положительной логики, при котором большему выходному напряжению соответствует сигнал логической 1, а меньшему – сигнал логического 0.

Не трудно заметить, что общей шиной является шина +Uп

, в результате чего потенциалы точек схемы отрицательны относительно общей шины. Однако в схеме токового ключа так же, как и в схемах ТТЛ, реализован принцип положительной логики, при котором большему выходному напряжению соответствует сигнал логической 1, а меньшему – сигнал логического 0.

Быстродействие такого ключа весьма велико, так как, во-первых, транзисторы принципиально не заходят в область насыщения, и, во-вторых, мал логический перепад напряжений между значениями логического нуля и логической единицы. Последнее реализовано выбором малых сопротивлений резисторов Rк1 и Rк2 схемы, что крайне полезно с точки зрения уменьшения постоянной времени перезаряда выходной емкости транзистора.

С токового ключа снимаются одновременно два сигнала – прямой и инверсный, связанные с сигналом х0 на входе схемы соотношениями:

y1 = x0

y0

= ![]()

Следует отметить, что схемотехнически токовый ключ, в соответствии с рисунком 6, повторяет схему дифференциального усилителя постоянного тока.

Выходное напряжение, снимаемое с выходов y1 и у0 всегда больше Uоп , так как транзисторы VT1 и VT2 всегда работают в ненасыщенном режиме. Поэтому непосредственное последовательное включение нескольких таких ключей невозможно. Для этого необходим согласующий каскад. В качестве такого согласующего каскада используются схемы эммитерных повторителей включенных между выходами токового ключа и выходами элемента.

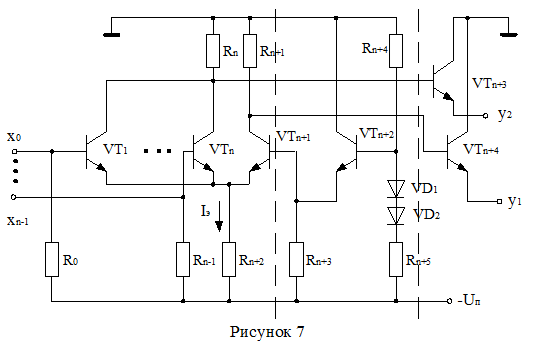

Полная схема БЛЭ, выполненного на основе токового ключа, приведена в соответствии с рисунком 7. Базовый элемент получен путем замены входного транзистора VT1 токового ключа группой параллельно включе6нных транзисторов VT1 – VTn .

Функционально схему БЛЭ можно разбить на три узла:

1. Токовый ключ на транзисторах VT1 – VTn +1 и резисторе Rn +2 ;

2. Источник эталонного напряжения, включающий параметрический стабилизатор на элементах Rn +4 , VD1 , VD2 , Rn +5 и эммиторный повторитель на VTn +2 и Rn +3 ;

3. Выходные эммиторные повторители на транзисторах VTn +3 и VTn +4 .

Цепь нагрузок транзисторов VTn +3 и VTn +4 вынесена из ИС БЛЭ, что способствует снижению рассеиваемой в ней мощности и расширению функциональных возможностей.

Диоды VD1 , VD2 в задающей цепи источника эталонного напряжения служат для термокомпенсации напряжения Uоп .

Принцип действия и функциональные возможности БЛЭ ЭСЛ.

Предположим, что на все входы схемы, в соответствии с рисунком 7, х0 , ..., хn-1 подано напряжение, близкое к –Uп . Тогда транзисторы VT1 - VTn будут заперты. Весь ток резистора Rn +2 протекает через транзистор VTn +1 , к выводу базы которого приложено напряжение Uоп . Этот транзистор поддерживается в активном режиме работы за счет действия глубокой последовательной отрицательной обратной связи по току. Если не учитывать обратные токи коллекторных переходов транзисторов VT1 - VTn , через резистор Rn протекает только базовый ток транзистора VTn +3 выходного эммиторного повторителя. Следовательно, напряжение на выходе близко к нулевому

Uy 2 = -Iб VTn+3 · Rn – Uбэ VTn+3

Численно напряжение Uy 2 примерно равно –0,9 В.

Через резистор Rn +1 кроме базового тока транзистора VTn +4 протекает ток Iк VTn+1 , примерно равный Iэ . Эти токи создают на резисторе Rn +1 падение напряжения, равное:

URn +1 = (Iк n+1 + Iб n+4 )Rn +1 = [(Iэ ·h21э )/(h21э + 1)+ Iб n+4 ] ≈ Iэ · Rn +1

Это напряжение преобразуется выходным эммиторным повторителем на транзисторе VTn +4 в выходное напряжение Uy 1 , определяемое выражением:

Uy 1 ≈ -Uбэ VTn+4 – IЭ · Rn +1

Численно напряжение Uy 1 примерно равно –1,7 В.

Если хотя бы на один из входов схемы х0 , ..., хn-1 подано напряжение, превышающее по уровню Uоп (-1,3 В), соответствующий транзистор VT перейдет в активный режим работы. Его ток будет равен току Iэ , что приведет к смене уровней выходного напряжения:

Uy 2 ≈ -Uбэ VTn+3 – IЭ · Rn

Uy 1 = -Iб VTn+4 · Rn +1 – Uбэ VTn+4

Из сказанного следует, что рассмотренная схема реализует по входу y2 операцию ИЛИ-НЕ, а по выходу у1 – операцию ИЛИ

у1 = (х0 + х1 + ... + хn-1 )

у1

= ![]()

Резисторы R0 – Rn -1 , включенные между базами транзисторов VT1 – VTn и выходом –Un , обеспечивает запертое состояние этих транзисторов при отсутствии входного сигнала. Это позволяет не беспокоиться о подключении неиспользуемых входов ИС выводом источника питания.

Особенностью схемотехнического построения элементов ЭСЛ является использования для подключения общей шины собственно такого переключателя и выходных эммиторных повторителей различных выводов ИС. Потребляемый ток, протекающий в этих цепях, имеет качественно различный характер. Как было отмечено ранее, в принципе работы токового ключа заложено потребление принципиально постоянного тока, так как его работа связана с перераспределением тока эммиторного резистор Rэ . Эммитерные же повторители потребляют импульсный ток. К тому же для улучшения частотных свойств сопротивления резисторов, подключаемых к выводам U1 и U2 ИС, выбираются весьма малыми (Rвнешн = 75 ... 100 Ом). Поэтому совместное питание этих цепей из-за малой величены логического перепада может приводить к ложному срабатыванию соседних элементов, т.е. появлению сбоев при обработке информации (внутренних помех). Разделение цепей питания позволяет устранить этот недостаток.

Раздельное питание токовых ключей и выходных эммиторных повторителей позволяет дополнительно решать задачу снижения мощности, рассеиваемой в реальной аппаратуре. Так как выходное напряжение элемента лежит диапазоне –0,9 ... – 1,7 В, то для питания внешних резисторов может быть использовано напряжение, не превышающее 2 В. Такое решение при малых сопротивлениях Rвнешн позволяет значительно уменьшить бесполезные потери мощности.

Рассмотренные функциональные возможности БЛЭ ЭСЛ простыми схемотехническими приемами могут быть существенно расширены. Для этого, как правило, используется два приема:

1. Совместное включение выходов нескольких элементов на общую нагрузку;

2. Многоярусное включение переключателей тока.

Первый прием использует свойство эммиторных повторителей поддерживать высокий уровень выходного напряжения, если хотя бы один из параллельно соединенных транзисторов включен.

Второй прием базируется на последовательном (многоярусном) включении токовых переключателей, что позволяет реализовать более сложные логические функции.

СХЕМОТЕХНИКА БЛЭ КМОП-ТИПА

Увеличение быстродействия ИС МДП требует увеличения токов перезаряда емкостей нагрузки. Однако это, как было показано ранее, ограничивается ростом потребляемой мощности и увеличением нестабильности выходных логических уровней. Преодолеть указанное противоречие можно либо технологическим путем, создавая транзисторы с меньшей входной емкостью, либо схемотехническим путем, применяя схему ключа на транзисторах с каналами различного типа (комплементарные транзисторы). Эти ключи, с одной стороны, позволяют значительно увеличить токи перезаряда емкости нагрузки, а с другой,— максимально уменьшить мощность, рассеиваемую в элементе. Напомним, что ключ на комплементарных транзисторах при правильном выборе параметров входящих в него элементов в статическом режиме работы практически не потребляет мощность от источника питания.

Потребляемая элементом мощность в статическом режиме тождественно равна мощности, отдаваемой им в нагрузку. А так как нагрузкой элемента являются входные цепи аналогичных элементов, носящие чисто емкостный характер, то мощность, отбираемая от источника питания, расходуется только в динамическом режиме на перезаряд этой емкости, т. е. имеет минимально возможное значение.

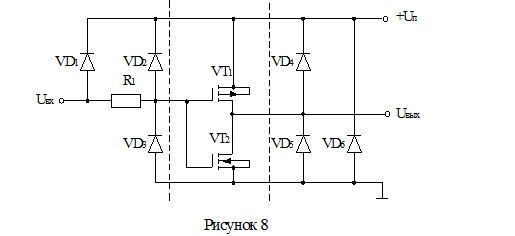

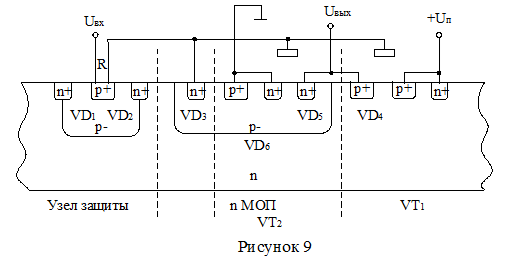

В соответствии с рисунком 8, приведена принципиальная электрическая схема и в соответствии с рисунком 9, срез топологии транзисторного ключа, используемого в ИС КМОП.

Она может быть разбита на три части: входной диодно-резисторный ограничитель напряжения; собственно ключ на КМОП-транзнсторах; выходная диодная цепь.

Входное сопротивление транзисторов, используемых в схеме ключа, достигает значений до 1012 Ом. При толщине изоляции между затвором и полупроводником порядка 50 ... 70 мкм его собственное пробивное напряжение составляет порядка 150 ...200В. Это предполагает введение в элемент специальной схемы защиты от статического электричества, которое может попасть на его вход в процессе хранения или монтажа. Роль этой схемы выполняет входной диодно-резистивный ограничитель на элементах VD1 , VD2 , VD3 и R1 . Данная схема ограничивает напряжение на входе транзисторного ключа в диапазоне от —0,7 В до На +0,7 В.

Элементы выходной диодной цени (VD4 , VD5 , VD6 ) образованы соответствующими областями самого транзисторного ключа и с точки зрения его работы не являются обязательными. Наличие этих диодов накладывает дополнительные ограничения на использование элемента. Всегда должно выполняться неравенство

│Uвх - Uвых │< Uп

В противном случае диоды входного ограничителя и выходной цепи могут открываться, закорачивая цепь питания элемента. Последнее может быть причиной его пробоя. Поэтому напряжение питания на КМОП-схсмы должно всегда подаваться до включения и сниматься после отключения входного информационного сигнала.

В противном случае диоды входного ограничителя и выходной цепи могут открываться, закорачивая цепь питания элемента. Последнее может быть причиной его пробоя. Поэтому напряжение питания на КМОП-схсмы должно всегда подаваться до включения и сниматься после отключения входного информационного сигнала.

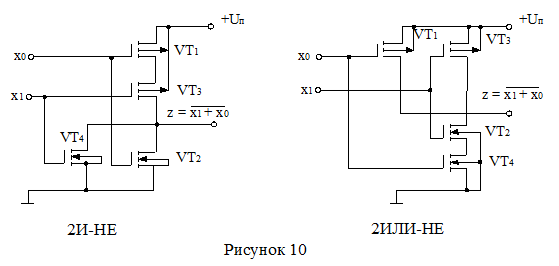

Схемотехнически БЛЭ КМОП-типа повторяют схемы элементов nМОП- и рМОП-типов. Отличие состоит в том, что всегда используются пары транзисторов. При этом если для реализации заданной логической функции транзисторы с каналом л-типа включаются последовательно, то парные им транзисторы р-типа включаются параллельно и наоборот. В качестве примера, в соответствии с рисунком 10, приведены принципиальные электрические схемы, реализующие логические операции 2И—НЕ и 2ИЛИ—НЕ. Для упрощения на приведенных схемах не показаны элементы входных и выходных цепей ключа.

Схемотехнически БЛЭ КМОП-типа повторяют схемы элементов nМОП- и рМОП-типов. Отличие состоит в том, что всегда используются пары транзисторов. При этом если для реализации заданной логической функции транзисторы с каналом л-типа включаются последовательно, то парные им транзисторы р-типа включаются параллельно и наоборот. В качестве примера, в соответствии с рисунком 10, приведены принципиальные электрические схемы, реализующие логические операции 2И—НЕ и 2ИЛИ—НЕ. Для упрощения на приведенных схемах не показаны элементы входных и выходных цепей ключа.

К особенностям схем БЛЭ следует также отнести отсутствие дополнительного нагрузочного транзистора. Его роль выполняет один из транзисторов ключа.

Анализ схем позволяет сделать важный практический вывод о том, что аналогично БЛЭ ТТЛ для БЛЭ КЛЮП параллельное включение нескольких их выходов запрещено.

В соответствии с таблицей 1, приведены наиболее важные параметры БЛЭ кмоп.

Следует также отметить, что КМОП-элементы обладают высокой помехоустойчивостью до 40% напряжения питания.

Таблица 1

| U1 вых min В |

U0 вых miх В |

tзр ср нс |

Fmax мГц |

Iпотр мкА |

Uп В |

Краз |

Свх пФ |

| 8 |

0,3 |

30 (Сн = 15 пФ) 100 (Сн = 100 пФ) |

БЛЭ Интегрально-инжекционной логики

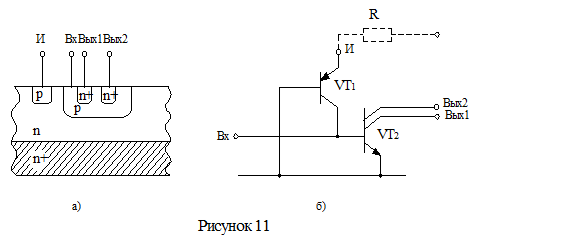

Для повышения технологичности изготовления желательно при разработке ИС применять схемотехнические решения, использующие только однотипные элементы, например транзисторы. Этот путь, как было показано ранее, реализован в ИС МДП, что наряду с другими достоинствами является причиной их широкого распространения. Однако, как уже отмечалось, ключ на биполярных транзисторах на сегодняшний день обладает лучшими как ключевыми, так и частотными свойствами. Это является предпосылкой к постоянному поиску новых схемотехнических решений для реализации биполярных ИС. Такой поиск привел к почти одновременной разработке фирмами Philips и IBM элемента интегральной инжекционной логики (И2 Л). Срез топологии и соответствующая ему принципиальная электрическая схема БЛЭ И2 Л приведены в соответствии с рисунком 11, а, б.

Особенностью элементов И2 Л является:

1. Отсутствие резисторов, что резко упрощает технологию производства МС;

2. Использование токового принципа питания, при котором в ИС задается не напряжение, а ток, который непосредственно инжектируется в область полупроводника, образующего структуру одного из транзисторов;

3. Пространственное совмещение в кристалле полупроводника областей, функционально принадлежащих различным транзисторам. При этом структура располагается как по горизонтали (планарно), так и по вертикали. Такое решение позволяет отказаться от применения специальных решений для отделения областей, принадлежащих различным элементам, как это необходимо делать в элементах ТТЛ и ЭСЛ.

4. Малое значение логического перепада, что позволяет максимально увеличить быстродействие элемента.

В приведенной схеме, в соответствии с рисунком 11, б, многоколлекторный транзистор VT2 выполняет функцию инвертирования входного сигнала, а транзистор VT1 — генератора (инжектора) базового тока транзистора VT2. К особенностям элемента следует отнести и постоянство тока инжектора во всех режимах работы элемента. Ток инжектора задается резистором R, который, как правило, выполняется общим на группу элементов.

В соответствии с рисунком 11,а видно, что транзистор VT1 образован планарной структурой, а многоколлекторный транзистор VT2 — вертикальной структурой. Причем, так как площадь каждого коллектора транзистора VT2 меньше площади его эмиттера, этот транзистор, по сути, работает в инверсном режиме, что способствует уменьшению его напряжения насыщения. Все сказанное позволило разместить весь элемент И2 Л на площади, занимаемой в схеме ТТЛ одним многоэмиттерным транзистором.

Важной особенностью элемента И2 Л является возможность, варьируя ток инжектора в широких пределах, изменить его быстродействие. Реально ток инжектора может изменяться от 1 нА до 1 мА, т. е. на 6 порядков. А поскольку при заданной схемотехнике энергия переключения элемента—величина непостоянная, в таких же пределах может изменяться и быстродействие элемента. Важно, что для этого не требуется никаких схемотехнических изменении в элементе.

Принцип действия схемы И2 Л заключается в следующем. Допустим, внешний сигнал на входе элемента (база транзистора VT2) отсутствует, что соответствует сигналу логической 1. В этом случае ток инжектора, втекая в базу транзистора VT2, насыщает его. На его коллекторах, а следовательно, и на выходных выводах элемента присутствует напряжение низкого уровня, равное напряжению насыщения транзистора VT2. Реально это 0,1 В ... 0,2 13.

Если база транзистора VT2 непосредственно или через насыщенный транзистор подключена к общей шине, то выполняется условие Uвх < Uбэ0 и транзистор VТ2 заперт, так как ток инжектора замыкается на общую нишу, минуя его эмиттерный переход. В этом случае напряжение на его коллекторах определяется внешними цепями. При последовательном включении нескольких инверторов это напряжение равно напряжению эмиттерного перехода последующего транзистора. Таким образом, для БЛЭ И2 Л справедливы следующие соотношения:

U0 = 0.1…0.2 B U1 = 0.6…0.7 В

Из приведенных соотношении следует, что логический перепад для БЛЭ И2 Л составляет 0,4 ...0.6 В.

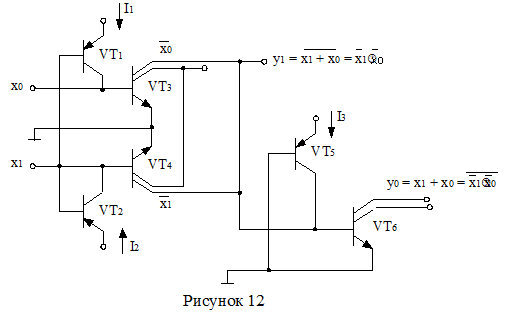

С использованием приведенной схемы могут быть реализованы основные логические операции И—НЕ и ИЛИ—НЕ. В соответствии с рисунком 12, показана логическая схема, построенная на трех инверторах И2 Л.

Особенностью элементов И2 Л является возможность параллельного включения нескольких их выходов. Из приведенной схемы следует, что при параллельном включении нескольких выходов в общей точке относительно входных переменных реализуется логическая операция ИЛИ—НЕ. Относительно же выходных сигналов элементов реализуется логическая операция И. Таким образом, если не требуется гальваническое разделение между входными и выходными сигналами, то логическая операция И выполняется без каких-либо дополнительных схемотехнических затрат простым объединением соответствующих выходов БЛЭ. После инвертирования результата выполненной операции ИЛИ—НЕ дополнительным элементом относительно исходных входных переменных реализуется логическая операция ИЛИ, а относительно выходных сигналов первых элементов — операция И—НЕ.

Таким образом, БЛЭ И2 Л позволяет максимально унифицировать структуру ИС, снизив площадь ее кристалла, и либо уменьшить ее потребление, либо повысить быстродействие.

Типовое время задержки распространения БЛЭ И2 Л при токе инжектора 0,1 мкА составляет 10нс. При этом энергия переключения для этого элемента па несколько порядков меньше, чем для элемента ТТЛ.

Ввиду небольшой помехоустойчивости, обусловленной малым логическим перепадом, БЛЭ И2 Л используются исключительно в составе БИС и СБИС и как отдельные ИС малой степени интеграции не выпускаются. При этом входные и выходные цепи ИС, выполненных по технологии И2 Л, делаются совместимыми по логическим уровням с сигналами ТТЛ.

Список используемой литературы

1. Гусев В. Г., Гусев Ю. Н. “Электроника” Москва 1991г

2. Игумнов Д. В., Королев Г. В., Громов И. С. “Основы микроэлектроники” Москва 1991г

3. Нефедов В. И. “Основы радиоэлектроники” Москва 2000г

4. Опадчий “Аналоговая и цифровая электроника” Москва 1999г

5. Сентурия С., Уэдлок Б. “Электронные схемы и их применения” Москва 1977г

Похожие рефераты:

Компенсация реактивной мощности в системах электроснабжения с преобразовательными установками

Микропроцессорная системы отображения информации

Описание работы электрической схемы охранного устройства с автодозвоном по телефонной линии

Автоматизированная система защиты и контроля доступа в помещения

Логические элементы и их электронные аналоги

Микропроцессорная система охранной сигнализации автомобиля

Электротехника и основы электроники

Разработка арифметико-логического устройства

Синхронные машины. Машины постоянного тока