| Скачать .docx |

Реферат: Арифметическое устройство комбинационный метод

Министерство образования и науки Украины

Черниговский Государственный Технологический Университет

Кафедра информационных компьютерных систем

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

Курсовой проект по дисциплине “Компьютерная схемотехника”

Исполнитель

студент гр. КС-073 Овдиенко В.А.

Руководитель

преподаватель Николаенко А.М.

Чернигов 2010

РЕФЕРАТ

Курсовой проект, 27 с., 11 рис., 3 приложений.

Объектом разработки являлось арифметическое устройство, выполняющего функцию умножения комбинационным методом.

Целью разработки являлось получение устройства позволяющего умножать введенные данные с последующим выводом полученных результатов. Данное устройство состоит из клавиатуры, по которой будет вводиться информация (максимальное вводимое число в десятичном коде 7), устройства умножения и устройства вывода информации, представленного набором жидко-кристалических индикаторов с фазовым принципом управления.

Устройство обеспечивает перевод входных данных в двоичный код, для осуществления операций, а затем перевод результата назад в десятичный.

В ходе разработки были получены:

- схема электрическая структурная;

- схема электрическая принципиальная.

Робота может быть использована для разработки более сложных устройств основанных на умножении или применятся в методических целях.

Дальнейшее развитие работы возможно в сторону увеличения числа операндов и их разрядности, снижения потребляемой мощности, приспособление к более удобным источникам питания.

Работа имеет практическую ценность. Расчет экономической эффективности не производился.

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, ИНДИКАТОР, ДЕШИФРАТОР, РЕГИСТР, ШИФРАТОР, КЛАВИАТУРА

РЕФЕРАТ

Курсовий проект, 27 с., 11 рис., 3 додатків.

Об'єктом розробки був арифметичний прилад що виконує функцію множення комбінаційним методом.

Метоюрозробки є отримання пристрою який дозволяє перемножуватиданні зподальшим виводом отриманих результатів. Даний пристрій складається зклавіатури, по якій будуть вводиться дані (максимальне число яке можна ввести в десятковому коді 7), пристрою для множення та пристрою для виводу інформації, представленого набором рідкокристалічних індикаторів з фазовим принципом керування.

Пристрій забезпечує перевід вхідних даних у бінарний код, для виконання операцій, а потім перевід результату назад в десятковий.

В ході розробки були отримані:

- схема електричнаструктурна;

- схема електричнапринципова.

Робота може бути використана для розробки більш складних пристроїв основаних на множенні чи бути використана в методичних цілях.

Подальший розвиток роботи можливий у напрямку збільшення числа операндів та їх розрядності, пониження споживчої потужності, приведення до більш зручних джерел живлення.

Робота має практичну цінність. Розрахунок економічної ефективності не проводився.

АРИФМЕТИЧНИЙ ПРИСТРІЙ, ІНДИКАТОР, ДЕШИФРАТОР, РЕГІСТР, ШИФРАТОР, КЛАВІАТУРА

THE ABSTRACT

Course project, 27 p., 11 fig., 3 appendixes.

By the object of development were arithmetic-logic unit, fulfilling function multiplications combination method.

The purpose of development was obtaining the device of that making it possible to multiply coded data with the subsequent conclusion of the obtained results. This device consists of the keyboard, on which will be introduced the information (maximum introduced number in decimal code 7), devices of increase and out of information device, will be entered on, presented by the set of thin film transistor liquid crystal indicators with phase principle of control.

Device ensures the transfer of input information into the binary code, for the realization of operations, and then the transfer of result back into the decimal.

In the course the developments were obtained:

- diagram is electrical structural;

- diagram is electrical fundamental.

Work it can be used for developing the more complex devices of those based on the multiplication or they will be used for systematic purposes.

Further development of work is possible into the side of an increase in the number of operands and their word length, reduction in the required power, the adaptation to the more convenient power sources.

Work has practical value. The calculation of economic effectiveness was not produced.

ARITHMETIC UNIT, INDICATOR, DECIPHERER, REGISTER, SHYFRATOR, KBD

Содержание

ВВЕДЕНИЕ………………………………………..…………………………………………………………………………..……………...…7

1 АНАЛИЗ ИЗВЕСТНЫХ МЕТОДОВ РЕШЕНИЯ

ПОСТАВЛЕННОЙ ЗАДАЧИ………………………………………………………..…….……………..…………..………8

1.1 Анализ устройств ввода информации…………………...………….……………………………………….....8

1.2 Анализ известных методов умножения…………………..…………………………………….…...….…….9

1.2.1 Комбинационные умножители …………………...………………………………………………...….…9

1.2.2 Метод многократного сложения…..………………………………………………..…..…………...…10

1.2.3 Метод сложения и сдвига…….………………………………………………………………..…….……….11

1.3 Анализ устройств вывода информации………..………...................................................…………………13

1.4 Принцип работы разрабатываемого устройства ……………………………………………....…14

2 РАЗРАБОТКА СХЕМЫ ЭЛЕКТРИЧЕСКОЙ СТРУКТУРНОЙ УСТРОЙСТВА…………………….........................………………………………………………………………………………...…..16

2.1Блок ввода данных..…………………………………….…………………………………………………………..…….….16

2.2 Блок выполнения операции умножения……………………………………………………….............….17

2.3 Блок вывода на семисегментный индикатор………………………………………..…………..……..18

3 РАЗРАБОТКА СХЕМЫ ЭЛЕКТРИЧЕСКОЙ ПРИНЦИПИАЛЬНОЙ УСТРОЙСТВА……..………………………………………………………………………………………………………...…………..21

3.1 Блок ввода даннях………………………………………………………………………………………………………...……21

3.2 Блок динамической индикации……………………………………………………………….…….…………..….23

3.3 Блок дешифрации и умноження…………………………………………………………………..….…………....24

4 РАСЧЕТНАЯ ЧАСТЬ…………………………...………………………………………………………..………..……………….26

4.1 Выбор помехоподавляющих конденсаторов……………………………………..…….……..……......26

4.2 Расчет элементов для подавления дребезга клавиатуры ………………………….………...27

4.3 Расчет элементов мультивибратора………………………………………………………….…………..……28

5 ОСНОВНЫЕ СВОЙСТВА ИСПОЛЬЗОВАННЫХ МИКРОСХЕМ…………..…..31

5.1 Приоритетный шифратор КМ555ИВ1……………………………………………………………….………31

5.2 Универсальный сдвигающий регистр К155ИР13………..………………………..…………..……31

5.3 Полный сумматор К555ИМ6…………………………………………………………………..………................…..32

5.4 Преобразователь двоичного кода в двоично-десятичный К155ПР76……….……32

5.5 Дешифратор КР514ИД1…………………………………………………………………………………..…....................33

ЗАКЛЮЧЕНИЕ…………………………………………………………………………………………………………................…….….34

СПИСОК ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ…………………………………………...…………….....…..35

Приложение А. Схема электрическая структурная…………...................…37

Приложение В. Схема электрическая

принципиальная АРИФМЕТИЧЕСКОГО УСТРОЙСТВА………………………………39

ВВедение

В данной курсовой работе поставлена задача разработки цифрового устройства «Умножитель» с клавиатурой и индикацией.

Умножитель – цифровое арифметическое устройство, предназначенное для перемножения двух заданных чисел и выдачи результата.Умножение может выполняться аппаратным и программным способами. В текущей работе будет рассмотрен только первый способ.

Данное устройство построено на основе широко используемых в производстве элементов ТТЛ и КМДП серий. Данное устройство является простейшим среди подобных арифметических устройств. Умножитель чаще всего встречается в виде отдельного блока реализующего заданную функцию в составе более сложных устройств. Примером может служить калькулятор.Если дополнить умножитель операциями деления, сложения и вычитания, расширить разрядность, то получим простейший калькулятор для операций над целыми числами.

На данный момент существует множество устройств, реализующих подобные простейшие функции, по этому актуальность данной работы снижается. Однако эта работа дает возможность приобрести навыки расчета и проектирования цифровых устройств.

Поскольку в настоящее время элементная база цифровых устройств довольно широка, то существует множество способов построения подобных устройств, и поэтому правильный выбор элементной базы и способа реализации данного устройства, является одной из главных задач данного проекта.

При создании цифровых умножителей используются различные методы: комбинационный, многократного сложения, сложения и сдвига.

Каждый из указанных методов характеризуется определёнными аппаратными затратами и быстродействием. Выбор метода реализации устройства диктуется часто не только оптимальным сочетанием указанных характеристик, но и стоимостью, сроками разработки.В данном случае умножитель был построен с использованиемкомбинационного метода, в результате чего устройство обладает высоким быстродействием.

1 АНАЛИЗ ИЗВЕСТНЫХ МЕТОДОВ РЕШИНИЯ АРИФМЕТИЧЕСКОГО УСТРОЙСТВА УМНОЖЕНИЯ

В соответствии с техническим заданием, в ходе выполнения курсового проекта, нужно разработать арифметическое устройство, которое должно выполнять операцию умножения комбинационным методом.

Арифметическое устройство – это устройство, предназначенное для выполнения арифметических и логических преобразований над числами, участвующими в операции. Умножители предназначены для умножения двоичных чисел. Умножение двоичных чисел можно выполнять аппаратным и программным способом. Существует три метода умножения аппаратным способом: комбинационный метод, метод многократного сложения и метод сложения и сдвига. Текущая задача предусматривает использование комбинационного метода.

1.1 Комбинационный умножитель

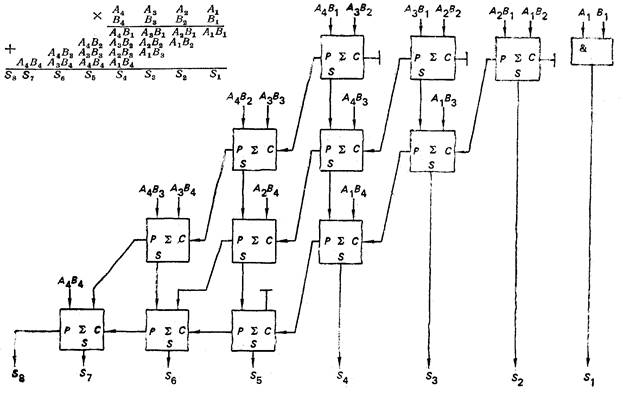

Комбинационные умножители реализуют процесс умножения с помощью отношения показанного на рисунке 1.1 .

Рисунок 1.1 - Схема, реализующая комбинационный метод на основе полных комбинационных сумматоров

Как видно из примера, частные произведения однозначно определяются множимым и очередным битом множителя. Частное ![]() -е произведение либо равно множителю, если

-е произведение либо равно множителю, если![]() , либо равно нулю, если

, либо равно нулю, если ![]() . Каждое последующее частное произведение сдвинуто на один разряд по отношению к предыдущему. Окончательное произведение получается последовательным суммированием частных произведений. Функциональная схема, реализующая данный алгоритм на основе полных комбинационных сумматоров, показана на рисунке 1.1 Операнды полных сумматоров

. Каждое последующее частное произведение сдвинуто на один разряд по отношению к предыдущему. Окончательное произведение получается последовательным суммированием частных произведений. Функциональная схема, реализующая данный алгоритм на основе полных комбинационных сумматоров, показана на рисунке 1.1 Операнды полных сумматоров ![]() получают с помощью 2-входовых схем И аналогично

получают с помощью 2-входовых схем И аналогично ![]() .

.

Основное достоинство комбинационного умножителя - высокое быстродействие, которое не связано с тактовой синхронизацией элементов, а определяется лишь задержками сигналов в логических элементах. Высокое быстродействие достигается ценой значительных аппаратных затрат: для перемножения m - разрядного множимого и n - разрядного множителя требуется m´n логических элементов 2И и n´(m-1) полных одноразрядных сумматоров.

1.2 Умножитель использующий метод многократного сложения

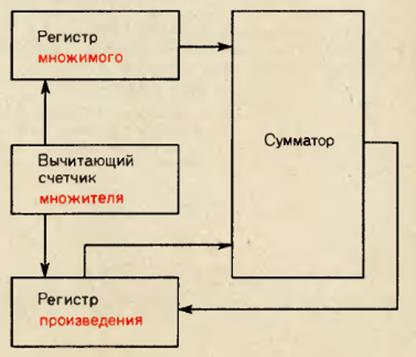

Произведение двух чисел, как известно, можно заменить суммирование множимого n раз, где n-значение множителя. Структурная схема устройства, которое реализует такой способ умножения, показана на рисунке 1.2

Рисунок 1.2 – Структурная схема умножителя с использованием способа многократного сложения

Процесс умножения происходит следующим образом. Перед началом умножения в регистр множимого заносится множимое, множитель - в вычитающий счётчик, в регистр произведения заносится 0. После уменьшения записанного в счётчик числа на 1, (т.е. после первого этапа счёта), в регистре оказывается частичное произведение (после первого этапа - множимое). После второго этапа в регистре произведения появится число, равное удвоенному произведению множимого, после третьего этапа - утроенному произведению множимого и т.д. После n-го этапа счёта в регистре произведения появится требуемое число. Процесс вычисления заканчивается после обнуления содержимого вычитающего счётчика.

Умножители, реализующие метод многократного сложения, характеризуются минимальными аппаратными затратами, но процесс умножения больших чисел занимает очень много времени.

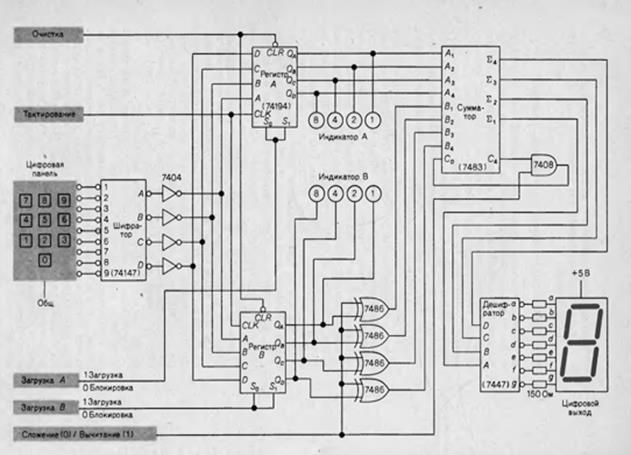

1.3 Параллельное устройство сложения-вычитания

Рисунок 1.3 - Схема 4-х разряднойпараллельной системы сложения-вычитания

Последовательность операций, выполняемых при работе с этим параллельным устройством сложения/вычитания, выглядит следующим образом. Сначала подается активный уровень сигнала на вход CLR для очистки обоих регистров (А и В), т. е. для их установки в состояние 0000. Затем выбирается режим работы (сложение или вычитание) путем установки соответствующего логического уровня на управляющем входе (будем считать, что установлен логический 0 для сложения). Далее по отдельности загружаются регистры А и В. Для управления загрузкой используются входы «Загрузка А» и «Загрузка Б». Для загрузки регистра А на входе «Загрузка А» устанавливается 1, а на входе «Загрузка Б»-0. Нажимается клавиша с нужной цифрой на клавиатуре с одновременной подачей одного тактового импульса на вход CLK. Двоичное число, которое загружено в регистр А, появляется на индикаторе А. Для загрузки регистра В на входе «Загрузка Б» устанавливается 1, а на входе «Загрузка А»-0. Нажимается клавиша со второй цифрой с одновременной подачей одного тактового импульса; второе двоичное число должно появиться в регистре В (вы увидите его на индикаторе В). Четырехразрядный сумматор 7483 мгновенно складывает оба числа, и сумма сразу появляется на выходном цифровом индикаторе.

Вычитатель вычитает содержимое регистра В из двоичного числа, находящегося в регистре А. Процедура вычитания с использованием схемы, что и для сложения. Единственное отличие заключается в установке 1 (вместо 0) на входе управления режимом работы (выбирается режим вычитания). В этом случае логические элементы И и исключающее ИЛИ обеспечивают вычитание вводимых в регистры чисел способом дополнения до 1 и циклического переноса. На выходном цифровом индикаторе появляется разность содержимого регистров А и В.

В рассматриваемой системе шифратор 74147 используется для преобразования десятичного выхода клавиатуры в двоичные числа; микросхема 7404 инвертирует сигналы на выходах этого шифратора. После инверторов двоичное число поступает на входы параллельной загрузки обоих регистров А и В. Индикаторы А и В показывают, какие двоичные числа находятся в данный момент в регистрах А и В соответственно; зафиксированные в регистрах двоичные числа А4 А3 А2 А1 и В4 В3 В2 В1 поступают на входы 4-разрядного сумматора 7483. Сумматор складывает эти числа, и сумма появляется в двоичной форме на выходах сумматора. Сумма преобразуется из двоичной формы в семисегментный код с помощью дешифратора 7447. Десятичная сумма появляется на цифровом выходном индикаторе.

К преимуществам данного арифметического устройства можно отнести его малая величина задержки, связанная с каждым переносом, наличия цифровой панели, высокое быстродействие, которое обеспечивается в первую очередь параллельным способом сложения многоразрядных чисел и использованием параллельных регистров, в которых не требуется производить сдвиг операндов. Таким образом записанное число сразу же появляется на выходе регистра и отображается на индикаторе, из этого следует, что затраты времени здесь минимальные.

Существенных недостатков схема не имеет кроме значительных аппаратных затрат, которые связаны с параллельным способом сложения многоразрядных чисел.

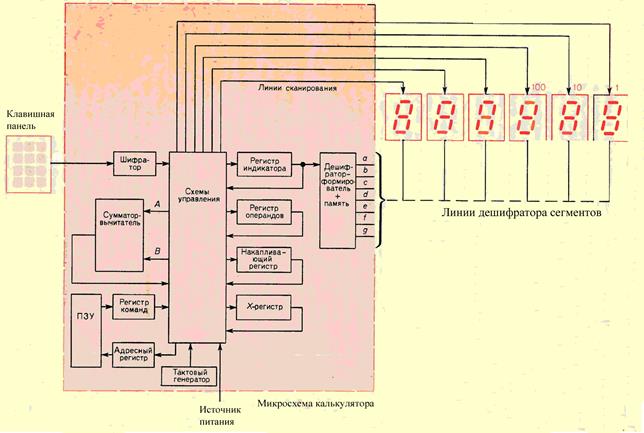

1.4 Микрокалькулятор

Основные узлы, входящие в состав микрокалькулятора это БИС, выполненная на одном кристалле и реализующая работу сотен или тысяч логических элементов, клавишная панель, семисегментный индикатор и источник питания. Как видно из рисунка 1.4, используемая в микрокалькуляторе БИС разбивается на ряд функциональных подсистем. Показанная на рисунке организация БИС только один из нескольких возможных способов обеспечения функционирования микрокалькулятора. Ядро системы — параллельный сумматор-вычитатель. Тактовый генератор синхронизует работу всех частей системы. Тактовая частота довольно высока-от 25 до 500 кГц. При включении микрокалькулятора начинают непрерывно вырабатываться тактовые импульсы, и все схемы работают «вхолостую» до тех пор, пока с клавиатуры не поступит какая-нибудь команда.

Рисунок 1.4 - Схема простейшего микрокалькулятора

Краткое описание принципа работы микрокалькулятора: Шифратор преобразует введенное число в двоично-десятичный код. Блок управления направляет двоичную комбинацию в регистр индикатора, где эта двоичная комбинация запоминается. Эта информация поступает также на входы семисегментного дешифратора, который переводит в возбужденное состояние соответствующие линии. При поступлении «включающего» импульса по шине опроса, подключенной к первому разряду индикатора, в этом разряде кратковременно высвечивается введенная цифра. Опрос разрядов индикатора осуществляется с большой частотой, и поэтому кажется, что цифра светится непрерывно, хотя на самом деле младший разряд индикатора (как и любой другой разряд) включается и выключается много раз за 1 с. Затем мы нажимаем клавишу «+». Код операции сложения передается в дополнительный регистр (Х-регистр) и запоминается. Теперь мы нажимаем на панели клавишу с второй цифрой . Шифратор преобразует десятичное введенное число в двоично-десятичный код. Блок управления пересылает двоичную комбинацию в регистр индикатора, далее эта комбинация поступает на входы дешифратора-формирователя, и после дешифрации на индикаторе появляется введенная вторая цифра. В это же время блок управления пересылает первую двоичную комбинацию в регистр операндов. Теперь мы нажимаем клавишу « = », и в блоке управления организуется проверка содержимого Х-регистра, чтобы «узнать», что же надо делать. Ответ Х-регистра: нужно сложить содержимое регистра операндов и регистра индикатора. Управляющее устройство подает соответствующие двоичные комбинации на входы сумматора. Результат сложения помещается в накапливающий регистр (аккумулятор). Блок управления реализует пересылку полученной двоичной комбинации в регистр индикатора, и на индикаторе появляется .

При обработке многоразрядных чисел и более сложных их представлений, содержащих десятичную точку, работа блока управления осуществляется в соответствии с инструкциями, находящимися в регистре команд. Цикл решения сложной задачи может включать сотни элементарных операций, запрограммированных в ПЗУ. Особенно впечатляет то, что даже сотни таких операций выполняются за время, меньшее 1/10 с.

К преимуществам данного устройства можно отнести хорошее быстродействие и реализацию многочисленных арифметических операций.

Недостаток – сложное конструктивное исполнение устройства.

1.5 Выводы

При разработке арифметико-логического устройства лучше придерживаться организации схемы комбинационного умножителя, который является самым быстродействующим из рассмотренных, а также параллельного устройства сложения-вычитания, которое является более простым по сравнению с микрокалькулятором.

2. Разработка схемы электрической структурной УСТРОЙСТВА

По результатам проведения анализа за основу разрабатываемого устройства была выбрана параллельная система сложения вычитания. Она содержит такие элементы: цифровая панель, шифратор, регистры, сумматор, дешифратор, цифровой выход. Таким образом, разрабатываемое устройство должно содержать следующие блоки:

а) клавиатура;

б) шифратор;

в) блок памяти;

г) блок умножения;

д) блок индикации.

2.1 Клавиатура

Клавиатура обеспечивает возможность ввода перемножаемых чисел. Она представляет собой набор переключателей (ключей), каждому из которых соответствует определенный код символа, код или команда. Символы, для удобства ввода, представляются в десятичном формате.

По заданию с клавиатуры можно ввести трехразрядное число, таким образом, максимальное число, которое можно будет ввести 7 (111 в двоичной форме), и число ноль. При нажатии какой-либо из клавиш может возникнуть дребезг контактов (многократный переход, в течении короткого промежутка времени, от замкнутого состояния к разомкнутому и обратно). Это может привести к формированию пачки импульсов вместо желаемого одиночного импульса. Устранить этот недостаток можно с помощью включения в схему триггера. Сигнал "ноль", прикладываемый с помощью переключателя к одному из входов триггера опрокидывает его. Причем при каждом срабатывании переключателя триггер реагирует на первое же замыкание соответствующей контактной пары и последующая вибрация уже не изменяет его состояния. В исходное состояние триггер переходит при отпускании клавиши.

2.2 Шифратор

Сигнал соответствующий нажатой кнопке на клавиатуре должен быть преобразован в двоичный код для последующего его использования. Это реализовывается с помощью шифратора. В данном устройстве будет использоваться приоритетный шифратор, для предотвращения случая нажатия нескольких кнопок одновременно. В таком случае шифратор реагирует на нажатие кнопки соответствующей более старшему разряду числа.

2.3 Блок памяти

Блок памяти - устройство хранения информации. В качестве этого устройства можно выбрать ОЗУ или регистры. Так как для хранения данных в ОЗУ требуется схема большой сложности, то более удобным способом хранения чисел являются регистры. После преобразования чисел множителя и множимого шифратором они запоминается в соответствующих регистрах множителя и множимого. Также используется регистр для хранения конечного результата.

2.4 Блок умножения

Блок умножения реализует операцию умножения двух чисел которые находятся в регистрах множимого и множителя. Он включает в себя сумматоры для реализации схемы умножения комбинационным методом. При выполнении умножения частные произведения однозначно определяются множимым и очередным битом множителя. Частное ![]() -е произведение либо равно множителю, если

-е произведение либо равно множителю, если![]() , либо равно нулю, если

, либо равно нулю, если ![]() . Каждое последующее частное произведение сдвинуто на один разряд по отношению к предыдущему. Окончательное произведение получается последовательным суммированием частных произведений. Операнды полных сумматоров

. Каждое последующее частное произведение сдвинуто на один разряд по отношению к предыдущему. Окончательное произведение получается последовательным суммированием частных произведений. Операнды полных сумматоров ![]() получают с помощью 2-входовых схем И аналогично

получают с помощью 2-входовых схем И аналогично ![]() .

.

2.5 Блок индикации

Чтобы проконтролировать правильность ввода и узнать результат необходимо устройство отображения информации. Для того чтобы введенные числа и результат отобразить на индикаторе необходим преобразователь кода. Преобразователь кода – преобразует двоичный код хранящийся в регистре результата в код соответствующий данному цифровому индикатору. После преобразования данных они подаются на блок индикации. В качестве блока индикации будет использоваться жидкокристаллический цифровой индикатор. Принцип управления согласно техническому заданию – фазовый.

3. РАЗРАБОТКА СХЕМЫ ЭЛЕКТРИЧЕСКОЙ ПРИНЦИПИАЛЬНОЙ УСТРОЙСТВА

Для построения схемы электрической принципиальной устройства были выбраны два вида цифровых микросхем построенных на основе ТТЛ и КМДП логики. Использование различных видов логики обуславливается только тем, что в микросхемах ТТЛ логики присутствуют микросхемы необходимые для разрабатываемого устройства, а в КМДП логике таких микросхем нет, и наоборот. Т.е. часть необходимых микросхем есть в ТТЛ логике, а часть в КМДП логике. Использование микросхем с разным типом логики связано с некоторыми трудностями, а именно согласованием уровней сигналов на выходах микросхем одного типа и входах микросхем другого типа. Также микросхемам с разным типом логики необходимо разное напряжение питания.

3.1 Клавиатура

Для построения клавиатуры используется двухпозиционный микропереключатель типа МП-12. Пределы коммутирующих токов и напряжений 1мкА…0,5мА и 0,5…36В соответственно.

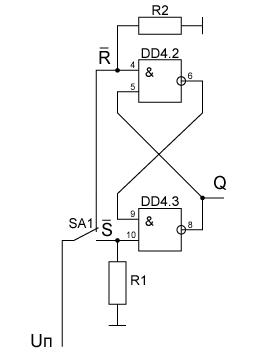

Набор элементов для ввода данных и устранения влияния дребезга изображен на рисунке 3.1.

|

Рисунок 3.1 – Набор элементов для ввода данных и устранения влияния дребезга контактов

Набор составляют МП-12 (SA1), резисторы R1, R2, 2 элемента 2И-НЕ (DD4.2 и DD4.3) – К555ЛА3. Элементы 2И-НЕ подключены таким образом, что реализуют простейший RS триггер с инверсными входами. В исходном положении питание подано на инверсный вход R, а на инверсный вход S подключена земля. Резисторы R1, R2 выбраны номиналом 1кОм, чтобы ограничить входной ток до 1 мА. На прямом выходе Q формируется сигнал логической единицы. Если нажать кнопку, то начнется многократное замыкание-размыкание контактов – дребезг. Но при каждом нажатии на кнопку триггер реагирует только на первое замыкание и последующий дребезг не изменяет состояния триггера. При подаче уровня логической единицы на инверсный вход S, а логического нуля на инверсный вход R на прямом выходе Q получаем уровень логического нуля. При отпускании кнопки триггер возвращается в первоначальное состояние. Таки образом на выходе триггера формируется импульс прямоугольной формы.

Всего в клавиатуре задействовано одиннадцать кнопок. Восемь кнопок отведены под числа от 0 до 7. Девятая кнопка – знак умножить. Десятая кнопка – знак равно. Одиннадцатая кнопка – сброс. В исходном состоянии на выходе всех триггеров соответствующих кнопкам 0…7 и сброс присутствует уровень логической единицы. При нажатии формируется уровень логического нуля (активный уровень).

3.2 Шифратор

После нажатия кнопки формируется уровень логического нуля потому, что в качестве приоритетного шифратора будет использоваться К555ИВ3, а у него все входы и выходы инверсные, и обычно входы сброса в микросхемах инверсные (рисунок 3.2). При подаче на любой из входов лог. 0 на выходах 0-1-2-3 формируется инверсный код номера входа, на который подан лог. 0.

Рисунок 3.2 – Шифратор приоритетов

На выходах шифратора необходимо поставить 3 инвертора, т.к. число трехразрядное, четвертый выход не используется.

3.3 Блок памяти

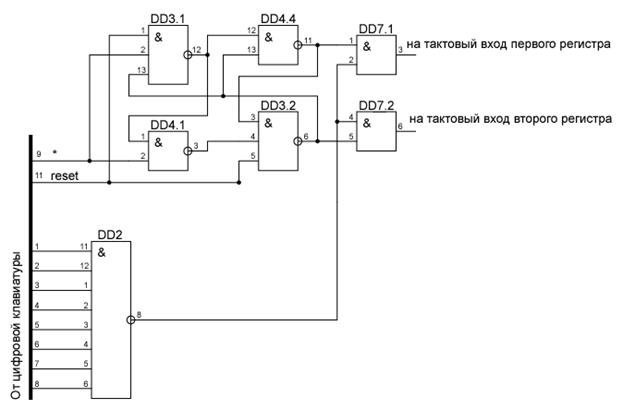

Выходы с триггеров соответствующих кнопкам 0…7 заводятся на входы элемента 8И-НЕ, сигнализирующего состоянием логической единицы на выходе о том, что нажата одна из цифровых кнопок. На рисунке 3.3 изображена схема управления записью в регистры двоичного кода, соответствующего нажатой кнопке.

Рисунок 3.3 – Схема управления записью пришедшего кода в регистры

После действия сигнала reset на выходе реализованного на рисунке 3.3 Т-триггера (элемент DD4.4) уровень логической единицы. Если нажать любую из цифровых кнопок, то на выходе DD2 формируется уровень логической единицы и подается на DD7.1 и туда же подается уровень с выхода DD4.4, на выходе DD7.1 формируется уровень логической единицы, который разрешает запись в первый регистр. Туда записывается двоичный код нажатой цифровой кнопки. При нажатии кнопки умножить, Т-триггер изменяет свое состояние на противоположное, и таким образом, подключает второй регистр, для записи следующего двоичного кода.

Для запоминания входных чисел используются регистры DD8, DD9. Особенность этих регистров в том, что он имеет четыре входа данных, каждому их которых соответствует свой тактовый вход. Но вход сброса общий для всего регистра. Это нужно для того, что входное число умножителя трехразрядное, а нам нужно еще хранить информацию о том, что например кнопка умножить была уже нажата (такая информация занимает как раз один разряд: 0 – не нажата, 1 - нажата). Такая информация позволит нам в дальнейшем гасить жидкокристаллический индикатор в случае если кнопка еще не нажата.

Рисунок 3.4 – Условное графическое обозначение регистра

Всего в схеме электрической принципиальной умножителя используется четыре регистра DD8, DD9, DD26, DD27. В DD8 в первые три разряда записывается пришедшее с клавиатуры число (множимое). В четвертый разряд записывается 1 – флаг того, что число уже пришло и его можно вывести на индикатор. То же для DD9, только записывается уже второе число (множитель). В DD27 записываются 3 младших разряда результата и флаг нажатия кнопки умножить. В DD28 записываются три старших разряда и флаг нажатия кнопки равно.

3.4 Блок умножения

С DD8 и DD9 информация (множимое и множитель) поступают на вход умножителя реализованного комбинационным методом (рисунок 1.1). Схема сумматора который входит в состав умножителя изображена на рисунке 3.5. Умножитель ничем не тактируется, и не зависит ни от каких управляющих сигналов, а поэтому умножает всегда. Т.е. как только будет введено второе число (множимое), на выходе умножителя сформируется результат. А по нажатию кнопки равно он запишется в регистры DD26, DD27.

Рисунок 3.5 – Условное графическое обозначение регистра

На выходах регистров DD26, DD27 – результат умножения в двоичном коде. Перед подачей его на дешифратор семисегментного кода, его нужно преобразовать в двоично-десятичный. Для этого используем микросхему К155ПР7. Т.к. младший разряд в двоичном и двоично-десятичном коде одинаковы, то он не подается на микросхему. Теперь полученный код, и коды с выходов регистров DD8, DD9 необходимо подать на микросхему К561ИД5 (преобразователь двоично-десятичного кода в семисегментный код со встроеной схемой управления цифровым индикатором фазовым методом) предварительно согласовав уровни ТТЛ и КМДП на микросхеме К561ПУ8.

3.5 Блок индикации

Выходы преобразователей в семисегментный код необходимо подключить к жидкокристаллическим индикаторам.

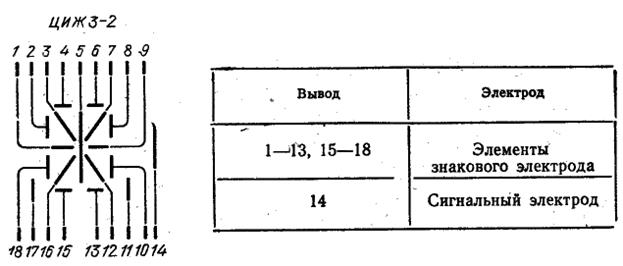

В качестве жидкокристаллического индикатора был выбран ЦИЖ3-2 (рисунок 3.6).

Рисунок 5.6 – Обозначение выводов жидкокристаллического индикатора ЦИЖ3-2

Этот индикатор одноразрядный, чтобы вывести на нем множимое, знак умножения, множитель, знак равенства и результат (два разряда) необходимо шесть индикаторов. Для того, чтобы вывести на индикатор число, в индикаторах отвечающих за отображение чисел пообъединяем контакты:

4,5 – соответствует A

8 – соответствует B

10 – соответствует C

15,13 – соответствует D

18 – соответствует E

2 – соответствует F

1,9 – соответствует G

A, B, C, D, E, F, G – выходы микросхемы К561ИД5.

Для того чтобы вывести на индикатор знак умножения с четвертого разряда регистра (флаг нажатия кнопки умножить) логический уровень через преобразователь ТТЛ-КМДП поступает на К561ИД5 на входы D1 и =1. Если это был уровень логической единицы, то ее двоичный код преобразуется в семисегментный, т.е. активны выходы B, C. Если это был уровень логического нуля, то индикатор отключен. С выхода В или С берем сигнал и пускаем на входы 3, 5, 7, 12, 16 индикатора отвечающего за отображение знака умножения формируя тем самым этот знак. Также отображаем и знак равенства.

3.6 Вывод

Так как в данном устройстве используются микросхемы разных типов логики, то и напряжение питания у них разное. Так для всех микросхем ТТЛ логики используется напряжение питания 5В. Для микросхемы К561ИД5 необходимо два источника питания +5В и –5В. Для микросхемы К561ПУ8 необходимо напряжение питания +10В. Поэтому для защиты от помех в цепь питания для каждого типа логики устанавливаются конденсаторы. Для ТТЛ шесть электролитических конденсаторов К53-26-6,8 и шесть высокочастотных К70-6-0,047. Для КМДП на питании +5В используются конденсаторы установленные для ТТЛ, на питании –5В устанавливается по одному конденсатору из вышеперечисленных, то же на питании +10В.

4 РАСЧЕТНАЯ ЧАСТЬ

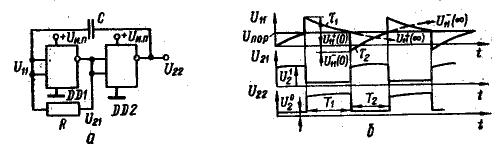

Для схемы возбуждения жидкокристаллического индикатора фазовым методом необходимо подавать на него сигнал прямоугольной формы с частотой 15…20Гц. Поэтому выберем генератор показанный на рисунке 6.1

|

Рисунок 6.1 – а) схема простейшего мультивибратора б) временная диаграмма

Отрицательной обратной связью через резистор R охвачен инвертор DD1. Самовозбуждение обеспечивается емкостной связью, охватывающей два инвертора. Релаксационные процессы перезаряда конденсатора С через резистор R, которые включены последовательно между выходами DD1 и DD2, определяют длительности полупериодов Т1, Т2 частоту генерации f, и скважность выходных импульсов Q.

Для ИМС ТТЛ-типа на сопротивление R накладывается ограничение сверху, поэтому обычно для серий 133, 155 оно не превышает 510 Ом. При R=390 Ом частота генерации приближенно определяется соотношением

fкГц =1,2/СмкФ (4.1)

Пусть частота генерации 40Гц, тогда С=1,2/0,04=30мкФ.

Для конденсатора К73-26-33 частота генерации будет f=1,2/33=36Гц. Данная частота удовлетворяет требованию не менее 20Гц.

Достоинства рассмотренного мультивибратора – простота схемы и стабильность частоты генерации: при изменении напряжения питания ИМС ТТЛ-типа от 4,5 до 5,5 вольт частота изменяется только на 2%. Главный недостаток схемы – искажение вершин выходных импульсов. Но для данной схемы этот недостаток не важен, поскольку от генератора требуется генерировать сигналы не с высокостабильной частотой, а с частотой которой хватит для того чтобы обновлять данные на жидкокристаллическом индикаторе.

ВЫвОДЫ

В результате работы была синтезирована схема умножения комбинационным методом двух трехразрядных чисел, соответствующая требованиям технического задания к курсовому проекту. Цифровой индикатор - жидкокристаллический и принцип управления ЦИ – фазовый.

Т.к. большая часть микросхем необходимая для построения умножителя есть в ТТЛ логике, то основную часть электрической принципиальной схемы реализована на элементах ТТЛ логики. На КМДП логике была построена часть схемы отвечающая за преобразование двоично-десятичного кода в код семисегментного индикатора и реализующая фазовый принцип управления цифровым индикатором. Также на КМДП логике построена часть схемы, отвечающая за преобразование уровней сигналов между ТТЛ и КМДП логикой.

Существуют некоторое ограничение по применению данного устройства для умножения чисел - размер числа не может превышать 3 двоичных разряда. Существует возможность сброса введенных данных (если при вводе пользователь ошибся либо просто провел операцию умножения и желает провести следующую).

Список использованных источников

1. Вервейко А.И. Конспект лекций по ЦЭВМ.- Чернигов: ЧДТУ, 2000.

2. Зубчук В.И. и др. Справочник по цифровой схемотехнике. –К.: Техника, 1990.- 448 с.

3. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги.-М.:КубК, 1996.- 512с.

4. Акимов Н.Н. и др. Резисторы конденсаторы: Справочник.-Минск.:Беларусь, 1994.- 592 с.

ПРИЛОЖЕНИЯ

ПРИЛОЖЕНИЕ А

СХЕМА ЭЛЕКТРИЧЕСКАЯ СТРУКТУРНАЯ

ПРИЛОЖЕНИЕ Б

СХЕМА ЭЛЕКТРИЧЕСКАЯ ПРИНЦИПИАЛЬНАЯ

РЕГИСТРА

ПРИЛОЖЕНИЕ В

СХЕМА ЭЛЕКТРИЧЕСКАЯ ПРИНЦИПИАЛЬНАЯ

ПРИЛОЖЕНИЕ Г

ПЕРЕЧЕНЬ ЭЛЕМЕНТОВ