| Скачать .docx |

Курсовая работа: Разработка тестопригодной схемы МПС на базе МП I8080

Учреждение образования «Гомельский государственный дорожно-строительный техникум имени Ленинского комсомола Белоруссии»

Специальность 2 - 40 02 02 «Электронно-вычислительные средства»

Цикловая комиссия спецпредметов цикла «ЭВС»

КУРСОВОЙ ПРОЕКТ

по дисциплине: «Эксплуатация и ремонт электронных вычислительных средств»

Тема: «Разработка тестопригодной схемы МПС на базе МП I8080»

Исполнитель:

учащийся группы ЭВС-41

Лукашевич Алексей Николаевич

Руководитель работы:

преподаватель

Минин Дмитрий Сергеевич

Гомель 2007

Учреждение образования «Гомельский государственный дорожно-строительный техникум имени Ленинского комсомола Белоруссии»

Цикловая комиссия спецпредметов цикла «ЭВC»

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту

по дисциплине «Эксплуатация и ремонт электронных вычислительных средств»

Тема: «Разработка тестопригодной схемы МПС на базе МП I8080»

Исполнитель: Лукашевич А.Н.

учащийся IVкурса ЭВС-41 группы

Руководитель: Минин Д.С.

Гомель 2007

РЕЦЕНЗИЯ НА КУРСОВОЙ ПРОЕКТ

| Оформление | Техническая грамотность | Замечания | Оценка за курсовую работу |

Оценка защиты курсовой работы _____________________________

______________________________________________________________________________________________________________________________

Общая оценка ____________________________________________

_______________________________________________________________________________________________________________________________

Заключение руководителя курсовой работы ______________________

_________________________________________________________________________________________________________________________________________________________________________________________________

Подпись ________________________

Оценка выставляется в баллах по 10-балльной шкале оценки результатов учебной деятельности учащихся.

Содержание

Введение

1. Расчетно-проектировочный раздел

1.1 Назначение проектируемого устройства и выбор области его применения

1.2 Описание элементной базы

1.3 Разработка структурной схемы проектируемого устройства

1.4 Разработка принципиальной схемы устройства

1.5 Разработка программного обеспечения

2. Эксплуатационно-технологический раздел

2.1 Разработка функциональной модели наиболее вероятных неисправностей устройства

2.2 Разработка алгоритма поиска неисправностей

2.3 Анализ и выбор метода устранения неисправностей

2.4 Разработка технологических инструкций по эксплуатации и ремонту устройства

Заключение

Спецификация

Литература

Приложение

Введение

Данный курсовой проект разработан на тему: «Разработка тестопригодной схемы МП Intel8080», а также предназначен для изучения вопросов диагностирования и обслуживания сложных технических систем.

Цель курсового проекта, охватывающего основные разделы дисциплины, состоит в формировании практических навыков по выбору параметров для диагностики, построению алгоритма поиска неисправностей, выбора вида аппаратуры контроля, формировании у меня как у будущего специалиста знаний основных теоретических положений и практических навыков для решения вопросов, связанных с разработкой, эффективной эксплуатацией, обслуживанием и ремонтом электронных вычислительных систем.

Для объекта диагностирования, необходимо выполнить следующие задания, которые представлены в данном курсовом проекте:

1. Разработать структурную схему устройства.

2. Разработать принципиальную схему устройства.

3. Разработать функциональные модели для двух наиболее часто встречающихся неисправностей.

4. Разработать алгоритм поиска и устранения неисправностей.

5. Проанализировать и выбрать методы устранения неисправностей.

6. Разработать технологическую инструкцию по эксплуатации и ремонту устройства.

В соответствии с вариантом №22, к МП I8080 были подключены следующие компоненты: ОЗУ – 2 Кбайт (реализовано на микросхемах К541РУ2), ПЗУ – 8 Кбайт (реализовано на микросхемах КР568РЕ1), контроллер приоритета прерывания (КПП) (реализован на микросхеме КР580BH59). Реализуемая логическая функция: X1*(X2*X3)VX4.

Выполнение задания курсового проекта предусматривает использование знаний, как из лекционного материала, так и из литературных источников, изучаемых самостоятельно.

1. Расчётно-проектировочный раздел

1.1 Назначение проектируемого устройства и выбор области его применения

Микропроцессорная система на базе микропроцессора I8080 или его отечественного аналога КР580ВИ80А необходима в производстве для получения и анализа данных с датчиков, выполнения заданной функции.

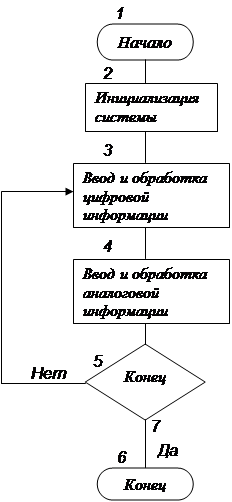

Микропроцессорная система работает по следующему алгоритму(Рисунок 1):

Рисунок 1

Блок 1: начало работы

Блок 2: инициализация системы – обеспечивает начальную установку системы: настройку программных БИС (параллельных и последовательных периферийных адаптеров, контроллера прерываний, таймера), засылку в выходные каналы управляющих воздействий и т.д.

Блок 3 : ввод и обработка цифровой информации – реализует задачу логического управления: принимает информацию от двоичных датчиков Х1…Х4, вычисляет значение булевой функции и выдает это значение в качестве управляющего сигнала (УС) Y1 по выходному каналу.

Блок 4: ввод и обработка аналоговой информации – обеспечивает прием информации с аналоговых датчиков V1…V3 её преобразование в цифровую форму, вычисление значений управляющих воздействий Y2…Y4 и выдачу их по выходному каналу. При этом Y2 и Y3 являются двоичными сигналами, а Y4 – 8-разрядным кодом, преобразуемым в аналоговый сигнал V4.

Блок 5: выбор – обеспечивает циклический режим управления или остановку МПС в соответствии с командой с пульта управления (ПУ) от оператора.

В системе также имеется двоичный датчик аварийной ситуации Х0, единичный сигнал с которого должен вызвать остановку системы в любой момент.

1.2 Описание элементной базы

Микропроцессорная система построена на базе МП Intel8080, советский аналог КР580ВМ80А

Микросхема Intel8080 (КР580ВМ80А) — функционально законченный однокристальный параллельный 8-разрядный микропроцессор с фиксированной системой команд, применяется в качестве центрального процессора в устройствах обработки данных и управления.

Микропроцессор имеет раздельные 16-разрядный канал адреса и 8-разрядный канал данных. Канал адреса обеспечивает прямую адресацию внешней памяти объе мом до 65536 байт, 256 устройств ввода и 256 устройств вывода.

Условное обозначение микропроцессора К580ВМ80А представлено в Приложении 1 (DD1)

Выводы процессора:

D0-D7 - магистраль (шина) данных;

A0-A15 – адресная магистраль (шина);

С1, С2 – тактовые импульсы;

HLD – запрос захвата;

HLDA – подтверждение захвата;

INT – запрос прерывания;

INTA – подтверждение прерывания;

RDY - готовность;

SR – сброс (инициализация);

WI - ожидание;

WR - выдача данных;

DBIN - прием данных;

SYN - сигнал синхронизации;

Ucc1 - +5 V;

Ucc2 - +12 V;

Uio – напряжение смещения -5 V;

GND - общий.

Основные характеристики ПРОЦЕССОРА :

разрядность ШД - 8;

разрядность ША - 16;

адресное пространство - 64 Кб;

число РОН - 6 восьмиразрядных;

организация стека - указатель стека позволяет в любой точки памяти зафиксировать вершину стека;

организация прерываний - прерывания векторные, существует упрощенная возможность организации прерываний на восемь направлений (адресов);

быстродействие - 500 000 коротких (регистр - регистр) операций;

тактовая частота …………………………0,5…2,5 МГц

напряжения питания …………………….5,12 В

мощность рассеивания …………………1,25 Вт

технология n-МДП;

диапазон рабочих температур …………10…+70 С

Uвыс ур(высокого уровня) - ……………9…13 В

Uнизк ур(низкого уровня) - …………… -0,3…+0,8 В

Длительность тактовых импульсов:

С1 і ………………………………………≥60 нс

С2 і……………………………………….220 нс

Так же в комплекте с процессором используются следующие микросхемы

1.2.1 Буферный регистр КР580ИР82

Микросхема КР580ИР82 представляет собой 8-разрядный буферный регистр, предназначенный для ввода и вывода информации со стробированием. Она может использоваться как в микропроцессорных системах, построенных на микросхемах серии КР580, так и в других вычислительных системах и устройствах дискретной автоматики.

Микросхема КР580ИР82 не содержит инвертирующие выходы. Данная микросхема имеет восемь триггеров D-типа и восемь выходных буферов, имеющих на выходе состояние “Выключено”. Управление передачей информации осуществляется с помощью сигнала STB “Строб”.

При поступлении на вход STB сигнала высокого уровня осуществляется не тактируемая передача информации от входа DI до выхода DO. При подаче на вход STB сигнала низкого уровня микросхема хранит информацию предыдущего такта; при подаче на вход STB положительного перепада импульса происходит “защелкивание” входной информации. Выходные буферы микросхемы КР580ИР82 управляются сигналом ОЕ “Разрешение выхода”. При поступлении на вход ОЕ сигнала высокого уровня выходные буферы переводятся в состояние “Выключено”.

Условное обозначение регистра представлено в Приложении 1 (DD3 – DD4)

Основные характеристики РЕГИСТРА:

1. Uпит (напряжение питания) - 5 В

2. Выходное напряжение питания низкого уровня ( Uвых низ ур ): ………. < 0.45В

3. Выходное напряжение питания высокого уровня ( Uвых выс ур ):… ……> 2.4 В

4. tзадер (Время задержки распространения информационного сигнала на выходе относительно информационного сигнала на входе < 30 нс

1.2.2 Генератор тактовых импульсов КР580ГФ24

Микросхема КР580ГФ24 представляет собой генератор тактовых импульсов (ГТИ), предназначенный для совместной работы с ЦПУ KP580BM80A. Генератор формирует: высокоуровневые тактовые сигналы Ф1 и Ф2 о несовпадающими фазами; тактовый сигнал Ф2Т, по уровню совместимый с ТТЛ и синхронизированный с сигналом Ф2; сигнал STSTB “Строб состояния”, который, поступая на системный контроллер, фиксирует состояние шины данных микропроцессора; сигнал RESET “Установка”.

Генератор опорной частоты при подключении к выводам XTAL1 и XTAL2 кварцевого резонатора обеспечивает высокую стабильность частоты, определяемую основной частотой возбуждения кварцевого резонатора.

Выход генератора опорной частоты выведен на внешний вывод OSC и соединен внутри микросхемы со счетчиком-делителем, входящим в состав тактового генератора. Тактовый генератор состоит из счетчика-делителя на 9, логических дешифраторов, формирующих требуемые тактовые импульсы, выходных формирователей и вспомогательных логических схем и триггеров для генерации выходных сигналов: Ф1.Ф2.Ф2Т, STSTB, Тактовые импульсы Ф1 и Ф2 управляют МОП-входами микропроцессора КР580ВМ80А. Тактовый импульс Ф2Т используется для управления ТТЛ-входами в режиме прямого обращения к памяти.

Отрицательный сигнал STSTB, длительность которого равна одному периоду частоты опорного генератора, формируется микросхемой КР580ГФ24 при поступлении на ее вход с микропроцессора КР580ВМ80А сигнала SYNC “Синхронизация”, свидетельствующего о начале машинного цикла.

При поступлении входного сигнала RESIN микросхема КР580ГФ24 с помощью триггера Шмитта и триггера Т1 вырабатывает сигнал RESET, синхронизированный с тактовым сигналом Ф2, По сигналу RESET осуществляется установка в исходное состояние различных устройств микропроцессорной системы.

Наличие в микросхеме триггера Шмитта позволяет подавать на вход RESIN сигнал с пологим фронтом. С помощью триггера Т2 осуществляется стробирование входного сигнала RDYIN “Готовность” тактовым сигналом Ф2.

Условное обозначение регистра представлено в Приложении 1 (DD2)

1.2.3 Системный контроллер КР580ВК38

Микросхема КР580ВК38 выполняет функцию системного контроллера и шинного формирователя, осуществляет формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ) и обеспечивает прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Формирование сигналов I/OW, MEMW в данной микросхеме происходит относительно сигнала STSTB “Строб состояния”, что позволяет при применении в микропроцессорной системе микросхемы КР580ВК38 использовать ЗУ и УВВ с более широким диапазоном быстродействия. Двунаправленный шинный формирователь осуществляет буферирование 8-разрядной шины данных и автоматический контроль направления передачи данных.

Подключение системного контроллера к шине данных микропроцессора осуществляется с помощью двунаправленных выводов DO—D7, к системной шине—с помощью двунаправленных выводов ‘DO—‘D7. При необходимости с помощью сигнала BUSEN “Управление системной шиной” выводы ‘DO—‘D7 системного контроллера могут быть переведены в состояние “Выключено”.

Регистр состояния выполнен на шести D-триггерах и предназначен для хранения информации о состоянии микропроцессора, поступающей по шине данных DO—D7. Запись в регистр состояния осуществляется по сигналу STSTB, поступающему в начале каждого машинного цикла.

Декодирующая матрица в зависимости от режима работы микропроцессора, зафиксированного в регистре состояния, и входных управляющих сигналов HLDA, WR, DBIN формирует сигнал INTA “Подтверждение прерывания” или сигналы чтения/записи при обращении к ОЗУ или УВВ. Условное обозначение системного контроллера представлено в Приложении 1 (DD5)

1.2.4 Постоянное запоминающее устройство (ПЗУ) КР568РЕ1

Микросхема представляет собой статическое постоянное запоминающее устройство ёмкостью 16384 бит (2048*8) с полной дешифрацией адреса, выходными усилителями и схемой управления “Выбор ИС”. Содержит 17784 интегральных элементов. Условное обозначение ПЗУ представлено в Приложении 1 (DD6 – DD8, DD16)

Выводы ПЗУ:

1– выбор ИС;

11,13,14,10,15,16,17,18,19,20,21 – адресные входы;

2,3,4,5,6,7,8,9 – выходы;

12 – общий;

23 – напряжение питания Uп2;

24 – напряжение питания Uп1;

Основные характеристики ПЗУ:

Номинальное напряжение питания Uп1 …………… 12 В±10%

Номинальное напряжение питания Uп2 …………… 5 В±10%

Выходное напряжение низкого уровня………………. ≤ 0,4 В

Выходное напряжение высокого уровня……………. ≥ 2,6 В

Ток потребления……………………………………..… ≤ 50 мА

Ток утечки на выходе…………………………….….…≤ 20 мкА

Удельная потребляемая мощность…………………....≤ 2,4 мкВт/бит

Потребляемая мощность…………………………..…..≤ 300 мВт

Время выборки адреса…………………………………≤ 550 нс

Время цикла……………………………………………≥ 800 нс

Входная (выходная) ёмкость…………………………≤ 10 пФ

1.2.5 Оперативное запоминающее устройства (ОЗУ) К541РУ2

Микросхема представляет собой статическое оперативное запоминающее устройство на 4096 бит (1024x4) со схемами разрядного и адресного управления.

Тип корпуса 2107.18-1. Условное обозначение ОЗУ представлено в Приложении 1 (DD12 – DD15) Таблица истинности приведена в Таблице 1

Выводы ОЗУ:

8 - вход сигнала “Выбор микросхемы”;

1,2,3,4,5,6,7,15,16,17 - адресные входы A0-A9;

11,12,13,14 – выход информации D0-D3;

9 - общий;

10 - вход сигнала “Запись” WR;

18 - напряжение питания.

Таблица 1

Режимы |

Вход | Вход/Выход | |

| CS | WR | DI/D0 | |

| Запись | 0 | 0 | DI |

| Хранение | 1 | X | Z |

| Считывание | 0 | 1 | D0 |

Основные характеристики ОЗУ:

Номинальное напряжение питания…………………5 В±5%

Выходное напряжение низкого уровня……………≤ 0,45 В

Выходное напряжение высокого уровня…………≥ 2,4 В

Напряжение на антизвонном диоде………………..≥ -1,5 В

Входной ток низкого уровня ………………………≤ 400 мкА

Выходной ток высокого…………………………….. ≤50 мкА

Ток потребления……………………………………… ≤ 100 мА

Время выборки адреса………………………………≤ 120 нс

Время доступа…………………………………………≤40 нс

Время выборки разрешения…………………………≤ 35 нс

Время выборки хранения…………………………….≤35 нс

Время выборки записи…………………………….…≤ 35 нс

Время выборки считывания……………………….…≤ 40 нс

Входная емкость.………………………………………≤ 5 пФ

Выходная емкость………………………………..……≤ 8 Пф

1.2.6 Контроллер приоритета прерываний (КПП) КР580ВН59

Микросхема представляет собой программированный контроллер прерываний, который обслуживает до восьми запросов на прерывание ЦП, поступающих от внешних устройств по линии IRO – IR7.

Схема сопряжения с шиной данных - обеспечивает взаимодействие микросхемы с внешней шиной данных, используя сигналы CS, WR, RD, A0 коммутирует внутренние цепи. Низкий уровень (0) на входе CS разрешает подключение м/с к шине, высокий уровень переводит ее выходы в отключенное состояние. Сигнал на входе A0 определяет, какой регистр будет выбираться при операциях чтения и записи: 1- будет выбран маски, 0 - будет выбран регистр управления / состояния или один из системных регистров, в зависимости от предыдущих команд. По низкому сигналу на входах WR (RD) производится запись (чтение ) выбранного регистра, при этом на входе CS должен быть низкий уровень.

Регистр запросов IRR (Interruptrequestregister) - отдельные его биты отвечают входам IRQ. 1 в соответствующем разряде показывает, что по соответствующему входу имеется запрос.

Регистр состояния / выполнения ISR (InterruptStatusRegister) - отдельные его биты отвечают за то, какие прерывания в данный момент обрабатываются.

Регистр маскирования IMR (InterruptMaskRegister) - 1 в соответствующем разряде запрещает обработку своего запроса.

Схема контроля приоритетов - определяет порядок выполнения запросов, полученных по различным входам IRQ.

Режимы работы контроллера :

1. Режим фиксированных приоритетов. В этом режиме приоритеты расставляются в следующем порядке : 7( низший приоритет ) - у входа IRQ7, ..., 0( высший ) - у входа IRQ0. Обработка запроса с меньшим приоритетом задерживается до окончания обработки запроса с более высоким приоритетом. Этот режим устанавливается после операции сброса.

2. Режим автоматического сдвига приоритетов. В этом режиме последнее обработанное прерывание получает низший приоритет, приоритеты остальных входов циклически сдвигаются ( см. таблицу ).

3. Режим программного сдвига приоритетов. Аналогичен предыдущему, но дно приоритетов устанавливается на прерывание с программно указываемым номером.

4. Автоматическое завершение прерывания AEOI. В этом режиме контроллер сбрасывает флаг обработки в ISR сразу же после получения ответа от процессора по линии INTA, т.е. в контроллер не надо посылать команду завершения прерывания EOI. Однако не рекомендуется использовать этот режим, т.к. подпрограмма обработки для такого режима должна допускать повторное вхождения, а также возможна потеря порядка данных, получаемых по прерыванию. В этом режиме контроллер "думает", что обработка прерывания происходит мгновенно.

5. Режим специальной маски. В этом режиме можно забыть о порядке приоритетов прерываний и обработать имеющиеся запросы в том порядке, в каком удобнее. После отмены режима старый порядок приоритетов сохраняется.

6. Режим опроса. В этом режиме прерывания как таковые не происходят вообще. Программа пользователя должна сама опрашивать содержимое регистра IRR и обрабатывать появление 1 в его разрядах как запрос.

Размещение приоритетов в режиме сдвига приоритетов

Вход IRQ с высшим приоритетом

IRQ0 0 1 2 3 4 5 6 7

IRQ1 7 0 1 2 3 4 5 6

IRQ2 6 7 0 1 2 3 4 5

IRQ3 5 6 7 0 1 2 3 4

IRQ4 4 5 6 7 0 1 2 3

IRQ5 3 4 5 6 7 0 1 2

IRQ6 2 3 4 5 6 7 0 1

IRQ7 1 2 3 4 5 6 7 0

Условное обозначение ОЗУ представлено в Приложении 1 (DD17)

Выводы КПП:

27 – А0 - Сигнал выбора регистра, Адрес;

4-11 - D7-D0 - Шина данных;

1 – CS - Выбор микросхемы;

2 – WR – Чтение;

27 – А0 – Запись;

12,13,15 - CAS0- CAS2 – Каскадирование;

14 – GND – Общий;

16 – SP - Выбор ведущего/ведомого режима;

17 – INT - Запрос прерывания на процессор;

18-25 - IR0-IR7 - Запрос прерывания;

26 – INTA - Подтверждение прерывания от процессора;

28 - E+ - Напряжение питания;

Основные характеристики КПП:

Вых. ток в сост. «лог. 0» на ШД=2,0 мА (i0 вых ШД)

Вых. ток в сост. «лог. 1» на ШД=0,4 мА (i1 вых ШД)

Вых. ток в сост. «лог. 0» на ШУ= 2 мА (i0 вых ШУ)

Вых. ток в сост. «лог. 1» на Ш= 0,4 мА (i1 вых ШУ)

Вх. ток в сост. «лог. 0» на ШУ, ШД, ША= 10 мкА

Вх. ток в сост. «лог. 1» на ШУ, ШД, ША= 10 мкА

Макс. ёмкость нагр. по ШД, ШУ= 100 пф

Число выводов = 28

Напряжение питания=+5 В

Ток потр.=100 мА

1.2.7 Дешифратор К155ИД6

Условное обозначение Дешифратора представлено в Приложении 1 (DD10)

Основные характеристики:

Входной ток, мА, не более:

низкого уровня ……………………………………… -1,6

высокого уровня ………………………………………0,04

Входное напряжение, В:

низкого уровня, не более ……………………………0,4

высокого уровня не менее ……………………..……2,4

Выходной ток, мА, не более:

низкого уровня ………………………………………16

высокого уровня………………………………………- 0, 4

Средний ток потребления, не более ………………15мА

Напряжение питания…………………………………5В.

1.2.8 Логические элементы

4 логических элемента 2И на К155ЛИ1. Микросхема имеет два входа на каждый элемент, на выходе вырабатывается сигнал логического И.

4 логических элемента 2ИЛИ на К155ЛЛ1. Микросхема имеет два входа на каждый элемент, на выходе вырабатывается сигнал логического ИЛИ.

Условное обозначение Логических элементов представлено в Приложении 1 К155ЛИ1 (DD9.1 - DD9.4); К155ЛЛ1 (DD11);

Основные характеристики К155ЛИ1 и К155ЛЛ1:

Входной ток, мА, не более:

низкого уровня ………………………………………-1,6

высокого уровня ……………………………………..0,04

Входное напряжение, В:

низкого уровня, не более …………………………….0,4

высокого уровня не менее ……………………………2,4

Выходной ток, мА, не более:

низкого уровня ………………………………………16

высокого уровня…………………………………… - 0, 4

Средний ток потребления, не более ………………15мА

Напряжение питания………………………………….5В.

1.3 Разработка структурной схемы проектируемого устройства

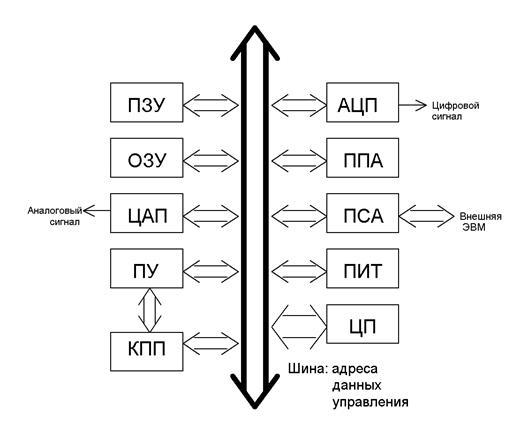

Составные части проектируемого устройства изображаются упрощенно в виде прямоугольников произвольной формы (Рисунок 2 – Структурная схема МПС), т. е. с применением условно-графических обозначений.

Непосредственно рассматривая проектируемую мной МПС на базе I8080 в её составе можно следующие наиболее важных блоки:

Генератор тактовых импульсов (ГТИ) – предназначен для создания последовательностей тактовых импульсов Ф1 и Ф2, а также сигналов готовности Гт, сброса Сбр и строба состояния СС.

Программируемый связной адаптер (ПСА) – представляет собой универсальное приемо-передающее устройство, которое преобразует снимаемую с ШД МПС информацию из параллельной формы в последовательную, пригодную для передачи в линию связи, а также осуществляет обратное преобразование.

Программируемый периферийный адаптер (ППА) – при использовании в качестве интерфейсной БИС позволяет подключать к МПС различное периферийное оборудование без дополнительных логических схем. Инициализация и управление работой ППА осуществляется с использованием шести управляющих и адресующих сигналов, подаваемых низ МПС по линиям управления, 8-разрядного управляющего слова режима, подаваемого от МП через шину данных, а также ряда сигналов, поступающих из внешних устройств.

Программируемый интервальный таймер (ПИТ) – предназначен для реализации различных времязадающих функций. Инициализация и управление работой ПИТ осуществляется с использованием пяти управляющих сигналов, подаваемых от МП по линиям управления, трех 8-разрядных управляющих слов, подаваемых от МП по шине данных, а также трех входных и трех разрешающих сигналов, поступающих от внешних устройств.

Оперативное запоминающее устройство (ОЗУ) – предназначено для временного хранения промежуточных вычислений.

Постоянное запоминающее устройство (ПЗУ) – память программы, в которую записана программа (последовательность выполнения команд) микроЭВМ и постоянные величины (константы), необходимые для ее выполнения.

Микропроцессор (МП) – программно-управляемое устройство, осуществляющее обработку информации и управление ею.

Аналого-цифровой преобразователь (АЦП) – сигналы с аналоговых датчиков V1…V3 преобразует в цифровую форму. С выхода АЦП коды, полученные от аналоговых датчиков сохраняются в памяти для дальнейшей обработки.

Цифро-аналоговый преобразователь – преобразует цифровую информацию в аналоговые сигналы. МПС формирует управляющее воздействие в виде аналогового сигнала с ЦАП. Код поступающий на вход ЦАП формируется как сумма значений полученных после преобразования с АЦП от датчиков V1…V3.

Контроллер приоритета прерываний (КПП) – формирует запрос на прерывание работы МП БИС и выдаёт на шину данных микроЭВМ трехбайтовую команду CALL<A1 ><A2 > и ответ на последовательное поступление трех сигналов ОБ. Пр с шины управлении микро-ЭВМ. Обрабатывает запросы на прерывания четырех уровней:

· INT0 – отказ источника питания (датчик аварийной ситуации Х0)

· INT1 – запрос от аварийного датчика

· INT2 – запрос от внешней ЭВМ

· INT3 – запрос с пульта оператора

Пульт оператора (ПО) - пульт управления содержит регистр со светодиодами индикации значений двоичных датчиков Х1…Х5, кнопку сброса, аварийную сигнализацию при сигнале от датчика Х0, тумблер «Останов», опрашиваемый каждый раз в конце программы.

Рисунок 2

1.4 Разработка принципиальной схемы устройства

Принципиальная схема МПС разрабатывается на основе структурной схемы, которая была разработана в предыдущем разделе. Принципиальная схема является самой полной схемой. На ней изображены все элементы которые в дальнейшем будут находиться в печатной плате. Принципиальная схема проектируемого устройства изображена на формате А3 в Приложении_1.

Главным звеном микропроцессорной системы является центральный процессор. Он представляет собой программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки.

Типовая схема центрального процессора включает в себя микропроцессор КР580ВМ80А(DD1), генератор тактовых импульсов (ГТИ) КР580ГФ24(DD2), системный контроллер (СК) КР580 ВК38 (DD5) и адресные регистры КР580ИР82 (DD3,DD4).

Частота следования синхроимпульсов F1 и F2 в девять раз меньше частоты кварцевого резонатора ZQ1, нужно использовать кварцевый резонатор с частотой 18 КГц. Сопротивление кварцевого резонатора носит индуктивный характер, что приводит к снижению рабочей частоты. Для компенсации индуктивной составляющей резонатора последовательно с ним включается конденсатор емкостью 15-30 пФ.

Кроме тактирования микропроцессора ГТИ используется также как источник системных тактовых сигналов CLK.

Сигнал INT предназначен для начальной установки системных модулей при включении питания. Сигналы HOLD, HLDA, BUSEN реализуют режим прямого доступа к магистрали со стороны других активных модулей системы.

Системный контроллер формирует стробы записи, чтения, сигнал подтверждения прерывания а также буферизирует двунаправленную шину данных.

Построение модулей памяти МП C .

Исходными «кирпичиками» при построении модулей памяти служат отдельные БИС оперативной памяти, а также БИС ПЗУ.

При построении модулей памяти возникают задачи наращивания информационной емкости путем объединения БИС в соответствующую матрицу. Наращивание емкости может производиться двумя путями. Во-первых, можно расширять разрядность путем параллельного включения БИС. Последние в этом случае объединяются по всем выводам, кроме информационных, которые в совокупности образуют расширенную информационную шину.

Второй путь наращивания информационной емкости — объединение БИС памяти по информационным входам — выходам. Кроме них объединяются все остальные входы за исключением входов CS (выбор чипа). Сигналы на этих входах определяют, какой из микросхем необходимо включаться в работу. Максимальное число объединяемых таким образом БИС определяется допустимой емкостной нагрузкой на выходе микросхемы.

В данном случае используются микросхемы ПЗУ КР568РЕ1 – 2К*8 и ОЗУ КР541РУ2 – 1К*4. Выбор нужного слова производится с помощью 11 адресных сигналов А0—А10. Кроме того, эти микросхемы имеют входы CS (выбор чипа), управление этими входами осуществляется с помощью дешифратора типа К155ИД6, выборка микросхемы осуществляется подачей на дешифратор сигналов ADR11-ADR14. Микросхемы ПЗУ (ROM) и ОЗУ (RAM) включаются в работу в соответствии с таблицей раскраски памяти, таблица 2

Таблица 2

| Корпус МС | Адрес |

| ПЗУ 1 | 0000÷07FF |

| ПЗУ 2 | 0800÷0FFF |

| ПЗУ 3 | 1000÷17FF |

| ПЗУ 4 | 1800÷1FFF |

| ОЗУ 1-2 | 2000÷23FF |

| ОЗУ 3-4 | 2400÷27FF |

Разрабатываемый блок – КПП

Микросхема КР580ВН59 является многофункциональным программируемым устройством, формирующим запрос на прерывание работы МП БИС и выдающим на шину данных микроЭВМ трехбайтовую команду CALL<A1 ><A2 > и ответ на последовательное поступление трех сигналов ОБ. Пр с шины управлении микро-ЭВМ. Значения адресов А1 и А2 сообщаются схеме в процессе выполнения программы ее начальной установки. Схема имеет восемь уровней запросов прерывания.

При одновременном поступлении импульсов на запрос прерывания схема определяет приоритетный уровень запроса, а также выполняет прерывание текущей программы обслуживания прерывания по входу запроса с более высоким приоритетом.

Схема имеет двунаправленную шину данных с возможностью перевода ее в третье состояние при подаче единичного сигнала на вход выборки ВМ при одновременной подаче единичных сигналов на входы INT и INTA. Шина данных используется для выдачи в микроЭВМ кoмaнды CALL< А1 > <А2 > информации состояния, содержания внутренних регистров, а также для записи управляющих слов в схему.

Уровень «О» или «1» определяет один из двух адресов внутренних устройств схемы, с которым микроЭВМ обменивается информацией.

Внешние устройства выдают импульсы на формирование запроса прерывания на входные зажимы IRO —IR7 схемы. Уровень «1» на любом из этих входов воспринимается как импульс на формирование запроса прерывания. Все поступающие импульсы на входы. Запрос на прерывание выдается схемой на выход INT и поступает на вход INT Процессора.

1.5 Разработка программного обеспечения

![]() Программа вычисления булевой функции Y=Х1*(Х2*Х3)vХ4.

Программа вычисления булевой функции Y=Х1*(Х2*Х3)vХ4.

![]() МПС опрашивает двоичные датчики, получает от них информацию, после чего вычисляет булевую функцию Y=Х1*(Х2*Х3)vХ4 и передаёт её значение в виде управляющего сигнала по выходному каналу. Таблица истинности представлена в таблице 3

МПС опрашивает двоичные датчики, получает от них информацию, после чего вычисляет булевую функцию Y=Х1*(Х2*Х3)vХ4 и передаёт её значение в виде управляющего сигнала по выходному каналу. Таблица истинности представлена в таблице 3

Таблица 3

| X4 | X3 | X2 | X1 | Y | |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 |

| A | 1 | 0 | 1 | 0 | 0 |

| B | 1 | 0 | 1 | 1 | 1 |

| C | 1 | 1 | 0 | 0 | 1 |

| D | 1 | 1 | 0 | 1 | 1 |

| E | 1 | 1 | 1 | 0 | 0 |

| F | 1 | 1 | 1 | 1 | 1 |

Программа:

0800 3E 9AMVIA,9Ah; Загрузка управляющего слова в аккумулятор

0802 D3 F3 OUTF3h; Запись управляющего слова в порт

0804 DBF0 INF0h; Чтение из порта А исходных данных

0806 E6 0FANI 0Fh; Выделение значимых бит

0808 47 MOVB,A; Сохранение значимых бит

0809 E6 01 ANI 01h; Выделение 1-го бита

080BFE 01 CPI 01h; Сравнение

080DCA 19 08 JZM1; Если равно, то переход к метке М1

0810 78 MOVA,B; Восстановление значимых бит

0811 FE 0CCPI 0Ch; Сравнение

0813 CA 19 08 JZM1; Если равно, то переход к метке М1

0816 C3 2D 08 JMPEND; Переход в конец программы

08 19 3E 01 M1: MVIA,01h; Установка аккумулятора в 1

081BD3 F1 OUTF1; Вывод в порт В результата

081D06 40 MVI B ,40 h ; Организация задержки

081F3EFFM 3: MVI A , FF Время выполнения тактов

0821 DE 01 M 2: SBI 01; 400 000 тактов при частоте 2 МН z = 200 мс.

0823 C2 21 08 JNZ M 2; Если не равно, переход по М2

0826 78 MOV A , B ; Загрузка данных из В в А

0827 DE 01 SBI 01; Вычитание из А 01

0829 47 MOV B , A ; Сохранение результата вычитания в В

082AC2 1F 08 JNZ M 3;

082DAFEND: XRAA; Обнуление аккумулятора

082ED3 F1 OUTF1h; Обнуление порта В

0830 00 NOP; Конец программы

Программа инициализации КПП:

0000 F3 DI ; Запрет прерывания

0001 3E 92 MVI A,12H; Запись в аккумулятор 12h

0003 32 0280 STA 2400H; Запись 2400 в аккумулятор

0006 FB ЕI; Включить обслуживание прерывания

2. Эксплуатационно-технологический раздел

2.1 Разработка функциональной модели наиболее вероятных неисправностей устройства

В работе данного устройства наиболее часто встречаются следующие неисправности:

1. Неисправности в работе ОЗУ в связи со слабой помехозащещенностью.

2. Неисправности в работе ключей SA1-SA5

3. Неисправности вследствие подачи на схему питания выше необходимого.

4. Неисправности в связи с перегоранием светодиодов VD1-VD5

Если такова неисправность обнаружена, то необходимо проверить все элементы схемы на работоспособность (особенно это касается микросхем, транзисторов и конденсаторов)

В данном устройстве будет использоваться наблюдаемость и управляемость для КПП.

Для КПП тестопригодность будет реализована на светодиодах и переключателях. На входы IR4-IR7 (запрос прерывания) и выход INT (Запрос прерывания на процессор) поставим светодиоды АЛ102ГФ, которые будут светиться при подаче на соответствующую линию логической единицы и на выходе INT – при выходе логической единицы. Это будет наблюдаемость. На все входы до светодиодов ставим переключатели, с помощью которых мы можем отключить КПП от МПС и падать на любые входы логические 1 или 0 и наблюдать, что будет на выходе INT (1- горит диод, 0 – не горит). Т.о. управляемость позволяет нам подать на входы комбинацию единиц и нулей, а наблюдаемость подтверждает подачу сигнала и показывает результат на выходе, на основе которого мы можем судить о правильности функционирования блока КПП.

2.2 Разработка алгоритма поиска неисправностей

Алгоритм поиска неисправностей состоит из комплекса основных мероприятий, связанных с отыскиванием неисправности в устройстве. Эти мероприятия могут быть различными и включают в себя операции от осмотра корпуса на наличие повреждений до проверки сигналов в контрольных точках.

Составим алгоритм поиска неисправностей для нашего устройства:

1 Осмотреть корпус устройства на наличие повреждений;

2 Аккуратно разобрать устройство;

3 Тщательно осмотреть места контактов гибких проводников с печатной платой, а также проверить качество крепления выводов ИМС и ЭРЭ к контактным площадкам на плате;

4 Проверить целостность соединительных проводов;

5 Осмотреть печатную плату и ее компоненты на наличие физических повреждений или повреждений вследствие электрического пробоя;

6 Проверить наличие питания на плате;

7 Проверить работоспособность ИМС контрольно-измерительными приборами;

8 Проверить работоспособность генераторов тактов и тона;

9 Проверить выходные сигналы в контрольных точках.

Данный алгоритм позволяет выявить основные неисправности препятствующие нормальной работе МПС.

2.3 Анализ и выбор метода устранения неисправностей

Определение, отыскание неисправностей в процессе ремонта любого устройства является наиболее трудоемкой операцией, требующей большего внимания и мастерства.

Найти неисправность - значит, найти отказавший элемент, блок, модуль и т. д. В процессе ремонта можно выделить четыре этапа: установления факта наличия неисправности; выявление ее характера; устранения неисправности и проверка устройства после ремонта.

Существует несколько способов отыскания неисправностей. Выбор того или иного способа зависит от назначения устройства и особенностей схемы. Для отыскания неисправности требуется хорошее знание, как минимум принципиальной схемы и конструкции ремонтируемого устройства.

Все неисправности любого устройства можно разделить на механические и электрические.

К механическим неисправностям относятся неисправности в механических узлах устройства (выход из строя кнопок и переключателей, а также неконтакт в разъемах).

К электрическим неисправностям относятся такие, которые приводят к изменению электрического сопротивления цепей, значительному увеличению сопротивления, значительному уменьшению его или короткому замыканию (выход из строя резисторов, светодиодов, микросхем и т. п.).

При поиске неисправностей устройства применяют пять способов:

1. Внешний осмотр позволяет выявить большинство механических неисправностей, а также некоторые электрические. Внешним осмотром проверяется качество сборки и монтажа. При проверке качества сборки вручную следует проверить механическое крепление отдельных узлов, таких как переключатели, переменные резисторы, штепсельные соединения (разъемы).

Внешним осмотром проверяют также качество электрического монтажа. При этом выявляют целостность соединительных проводников, наличие затеков припоя, которые могут привести к коротким замыканиям между отдельными участками схемы, обнаруживают провода с нарушенной изоляцией, проверяют качество паек и т. п. Внешним осмотром можно выявить дефекты отдельных элементов (обрыв выводов, резисторов, механическое повреждение конденсаторов и другие).

Внешний осмотр, как правило, делают при отключенном питании аппаратуры. При его проведении особое внимание необходимо обращать на то, чтобы в монтаж не попали случайные предметы, которые при включении устройства могут вызвать короткое замыкание.

Внешним осмотром можно выявить неисправный светоэлемент (по яркости свечения), резистор (по изменению цвета или обугливанию поверхностного слоя) и другие элементы.

Во включенном состоянии можно определить перегрев трансформаторов, электролитических конденсаторов, полупроводниковых элементов. Появление запахов от перегретых обмоток, резисторов, пропиточного материала трансформаторов также сигнализирует о наличии неисправностей в схеме устройства.

Иногда в ходе осмотра возникает сомнение в исправности отдельных элементов. Тогда следует выпаять элемент и проверить его исправность более тщательно.

2. Способ промежуточных измерений. Заключается в последовательной проверке прохождения сигнала от блока к блоку до обнаружения неисправного участка.

3. Способ исключения - заключается в последовательном исключении исправных узлов и блоков.

4. Способ замены отдельных элементов, узлов или блоков на заведомо исправные, широко используется при ремонте устройств ВТ. Например, можно заменить элемент (транзистор, трансформатор, микросхему) или блок на заведомо исправный и убедиться в наличии неисправности на этом участке.

5. Способ сравнения - заключается в сравнении параметров неисправного аппарата с параметрами исправного аппарата того же типа или марки.

Использование того или иного способа поиска неисправности зависит от особенностей схемы устройства.

Так как данное устройство состоит в основном из микросхем, то при нахождении неисправности в интегральной схеме она подлежит замене.

Кроме ИМС в устройстве располагается ряд таких элементов, как транзисторы, резисторы, диоды и конденсаторы. При порче они также нуждаются в замене.

Возможны такие неисправности, как неконтакт (т.е сигнал не проходит от начала своего пути и до конца). При этом надо тщательно осмотреть устройство на наличие обрывов и пропаять подозрительные места.

2.4 Разработка технологических инструкций по эксплуатации и ремонту устройства

Для того чтобы облегчить работу по ремонту устройства сведем в таблицу 4 возможные неисправности и способы их устранения

Таблица 4

Наименование неисправности, внешнее проявление и дополнительные признаки |

Вероятная причина | Способ устранения |

| 1 | 2 | 3 |

| 1. Отсутствие питания | Обрыв провода питания Вышел из строя предохранитель |

Проверьте целостность проводов. При обрыве замените их. Проверьте предохранитель, при неисправности - замените |

| 2. Не светится один из светодиодов VD1 – VD5 | Не поступает Сигнал Светодиод вышел из строя |

Проверка наличия обрывов, короткого замыкания на линии идущей к светодиоду Заменить светодиод |

| 1 | 2 | 3 |

3. При тестировании КПП не реагирует на подаваемые логические сигналы |

Вышел из строя КПП(DD17) Не работают ключи Отсутствует питание |

Проверить DD17, при необходимости заменить, Проверить SA2-SA5, возможны механические повреждения, при необходимости заменить Пункт 1. |

4. Не работает один из блоков МПС (ОЗУ,ПЗУ, КПП и т. д.) |

Неисправен сам блок либо обрыв ША, ШД, ШУ, питания |

Проверка наличия обрывов, короткого замыкания на всех линиях идущих к блоку и от блока Проверить не работающий блок |

Заключение

В данном курсовом проекте мною была разработана МПС на базе I8080 с тестируемым блоком КПП. Благодаря данному курсовому проекту мною были закреплены на практике теоретические знания, охватывающие практически все спецпредметы изученные на учебной скамье, необходимые для будущего техника-электроника.

В ходе проделанной работы были разработаны функциональные узлы МПС на базе I8080 и обеспечены взаимосвязи между ними.

Таким образом, курсовое проектирование по предмету «Эксплуатация и ремонт электронных вычислительных средств», является наиболее важным и ответственным этапом: для учащегося (будущего специалиста) в изучении предмета, а для преподавателя - в самоудовлетворении своим умением преподнести будущему специалисту (технику-электронику) необходимую для его дальнейшей самостоятельной деятельности знаний по своей области деятельности.

Список использованных источников :

1. Галкин О.Н. Микросхемы памяти и их применение: Справочник. –М. Радио и связь, 1990.

2. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. В 2 т./ под редакцией В.А. Шахнова. – М.Радио и связь, 1988.

3. Бирюков С.А. Применение цифровых микросхем серии ТТЛ и КМОП - М.: ДМК, 1999.

4. Справочник: Цифровые интегральные микросхемы: Богданович М.И. и другие. Мн.; 1996.

5. www.assembler/PC.htm языки программирования

6. http://ns.onego.ru/~sprut/Схемы, pадиолюбительские технологии, пpогpаммиpование ПЗУ и дp.

7. http://www.qsl.net/eu5rЖypнал "РАДИОЛЮБИТЕЛЬ"

8. Агаханян Т.М. Интегральные микросхемы.-М. Энергоатомиздат,1983

9. Диск «RADIO» - Большой справочник радиолюбителя

10. Баюков А.В. и др. Полупроводниковые приборы: Диоды, тиристоры, оптоэлектронные приборы. Справочник.-М.: Энергоатомиздат, 1987.

11. Стрыгин В.В, Щарев Л.С. Основы вычислительной микропроцессорной техники и программирования. Москва «Высшая школа» 1989.