| Скачать .docx |

Курсовая работа: Проектирование цифрового корректирующего фильтра

Содержание

1. Ведение

2. Анализ задачи и ее формализация

3. Разработка и обоснование структурной схемы устройства

4. Разработка и обоснование общего алгоритма функционирования устройства и его описание

5. Разработка программы

6. Оценка быстродействия устройства

7. Отладка разработанной программы. Результаты отладки

8. Составление принципиальной схемы устройства и ее описание

9. Заключение

10. Список использованных источников

11. Приложение

Описание структурной схемы микросхемы КА1603РЕ1

Описание структурной схемы микросхемы КР537РУ17

Триггер К555ТМ2

Регистр К1533ИР23

Микросхема К1108ПВ1

1. Введение.

В радиотехнике, наряду с методами аналоговой обработки сигналов, широкое распространение получили методы и устройства цифровой обработки сигналов, реализованные на основе микропроцессоров (МП). Применение МП в радиотехнических системах (РТС) существенно улучшает их технико-экономические показатели (потребление энергии, габариты, стоимость и т.д.), открывает широкие возможности реализации сложных алгоритмов цифровой обработки сигналов (ЦОС).

Применение МП целесообразно в тех случаях, когда реализация определенных функций РТС с использованием «жесткой логики» требует большого количества микросхем .

Микропроцессоры находят применение при решении широкого круга радиотехнических задач, таких как построение радиотехнических измерителей координат, сглаживающих и экстраполирующих фильтров устройств вторичной обработки сигналов, специализированных вычислительных устройств бортовых навигационных комплексов, устройств кодирования и декодирования сигналов, весовой обработки пачечных сигналов в радиолокации, различного рода измерительных устройств и т.п.

При создании радиоэлектронной аппаратуры используются три основных подхода реализации цифровых устройств: аппаратный, программный и аппаратно- программный. При аппаратном получают цифровые устройства с традиционной «жесткой'' логикой, что обеспечивает наибольшее быстродействие устройств, но требует трудоемкой разработки индивидуальной структуры цифрового устройства – спецпроцессора.

При программном подходе цифровое устройство реализуется в виде программы для готовой универсальной ЭВМ, в качестве которой можно использовать микроЭВМ, предназначенную для встраивания непосредственно в разрабатываемые блоки. Аппаратно-программный подход предполагает разработку как программных, так и аппаратных средств. К ним относятся цифровые устройства, реализованные как автоматы с микропрограммным управлением и хранимой в ПЗУ программой, а также цифровые устройства, построенные на основе микропроцессора. Аппаратно-программный подход при использовании современных интегральных схем позволяет в наибольшей степени учесть особенности решаемых задач.

Выбор варианта построения цифрового устройства в каждом конкретном случае осуществляется с учетом всех требований технического задания. Применение «жесткой” логики оправдано в двух основных случаях I) при необходимости получения предельно бысокого быстродействия; 2) при построении относительно несложных устройств на интегральных схемах малой и средней степени интеграции.

Если же от устройства требуется гибкость, т.е. способность изменения функций программным путем в процессе работы или расширения круга решаемых задач, тогда становится целесообразным использование микропроцессоров (МП), Применение оправдано при построении устройств большой сложности, если быстродействие МП оказывается достаточным. Ограничения, связанные с недостаточным быстродействием МП, можно преодолеть построением многопроцессорных устройств или выполнением части функций с помощью специально разработанных аппаратных средств, работающих совместно с МП.

Наибольшая экономичность цифрового устройства по объему оборудования и другим эксплуатационным параметрам, а также наименьшая трудоемкость проектирования достигаются при использовании однокристальных МП.

2. Анализ задачи и ее формализация.

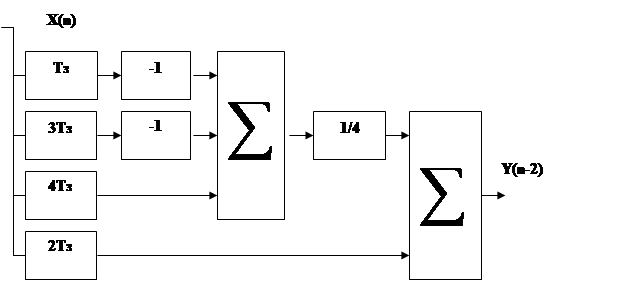

Согласно техническому заданию разностное уравнение имеет вид:

![]()

Для упрощения программы и сокращения числа выполняемых машинных циклов, т.е. для повышения быстродействия, упростим данное выражение и представим его в следующем виде:

![]()

Согласно данному уравнению изобразим структурную схему проектируемого устройства:

где Тз- время задержки, равное интервалу дискретизации.

По заданию проектируемое устройство, т.е. корректирующий фильтр, должно быть реализовано на базе комплекта БИС серии КП580.

Помимо МП ВМ80А, для построения законченного модуля ЦП необходимы:

- генератор тактовых импульсов КР580ГФ24, который вырабатывает тактовые импульсы, импульс сброса и обеспечивает синхронизацию всего устройства в целом.

- системный контроллер и формирователь шины КР580ВК28/38, который обеспечивает работу с памятью и портами, а так же аппаратно формирует команду векторного прерывания RST7.

- буферные регистры КП580ИП82/ИП83

Преобразование входного аналогового сигнала в цифровой код осуществляется с использованием АЦП К1108ПВ1. Поскольку диапазон входного сигнала оказывается не согласованным с рабочим диапазоном используемого АЦП, на входе устройства придется поставить масштабирующий усилитель.

Данные из АЦП выходят в виде 8 разрядного прямого кода. В ЦП они обрабатываются в форме 16 разрядного дополнительного кода, поэтому переполнения не происходит.

Перевод прямого кода в дополнительный реализуем программно.

Из формул видно что, для формирования выходного отчёта необходимо использовать текущее значение входного отчёта и его предыдущие значения. Для хранения входных, выходных, предыдущих значений отсчетов и промежуточных результатов вычисления необходимо выделить область памяти в ОЗУ, поскольку реализовать в полном объеме функции проектируемого устройства с использованием программно доступных регистров МП не возможно.

Обработка отсчетов производится программой, хранящейся в ПЗУ. К моменту прихода следующего отсчета устройство должно закончить обработку предыдущего и находиться в состоянии готовности. Для реализации данного условия необходимо чтобы частота дискретизации была меньше времени обработки одного отсчета.

Для передачи данных внешнему устройству потребуется порт вывода, в качестве которого может служить регистр с параллельной загрузкой. Согласование рабочего кода МП, т.е. параллельного дополнительного кода, с требуемым выходным кодом представления данных реализуем программно.

Процедура вывода данных выполняется независимо от состояния внешнего устройства. Такой вид обмена называется прямым или безусловным. Процедура вывода инициируется и выполняется непосредственно программой, реализуемой ЦП. Программно- управляемый обмен не является единственным типом обмена. Но судя по аппаратным затратам, это наиболее эффективный тип обмена.

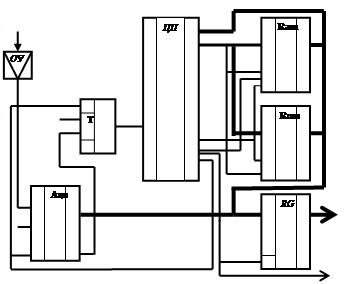

3. Разработка и обоснование структурной схемы устройства

Набор КП580 определяет типовой состав аппаратных средств, образующих структуру вычислительного ядра системы. В его состав входят МП, ОЗУ, ПЗУ, схемы формирования сигналов синхронизации, микросхемы формирования сигналов управления системой. Полная структурная схема МП- устройства получается при объединении структуры вычислительного ядра и дополнительных аппаратных узлов.

Аппаратный состав фильтра в целом уже определен в п.2, незатронутым остается масштабирующий усилитель. Также следует произвести согласование адресов ОЗУ, ПЗУ, портов ввода-вывода с адресами МП.

Вспомогательные схемы целесообразно выполнять с наименьшими аппаратными затратами, т.е. следует стремиться к сокращению количества микросхем.

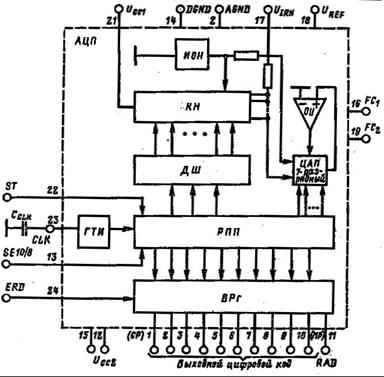

По заданию следует использовать микросхему 10-разрядного быстродействующего функционально законченного АЦП последовательного приближения К1108ПВ1, предназначенную для преобразования аналогового сигнала в двоичный параллельный цифровой код. Микросхемы серии К1108 изготовляются по биполярной технологии, в том числе с применением кремниевых структур с диэлектрической изоляцией, СВЧ транзисторов, элементов ЭСЛ. В состав функциональной схемы преобразователя входят ИОН, ГТИ, выходной регистр с тремя логическими состояниями и функцией хранения информации в течение одного цикла преобразования ВРг РПП, ЦАП, многовходовый КН с входным резисторным вычитающим устройством, дешифратором уровней тока и др. .

Микросхема рассчитана на преобразование однополярного входного напряжения в диапазоне от О до З В, подаваемого на вход через внешний ОУ или УВХ при максимальной частоте преобразования 1,1 МГц для 10-разрядного ре жима и 1,33 МГц для 8-разрядного режима.

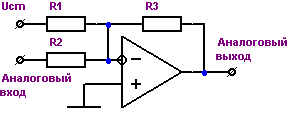

В качестве масштабирующего усилителя возьмём операционный усилитель, обладающий низким коэффициентом шума и имеющий хорошие энергетические показатели.

Для согласования диапазона входного сигнала и рабочего диапазона АЦП добавим к нему цепь обратной связи . Также на вход ОУ придется подать дополнительное опорное напряжение для смещения сигнала. Схема инвертирующего включения ОУ представлена на рис.1. Для упрощения расчетов зададим ![]()

Поскольку:

· диапазон изменения входного сигнала – (-4.5 … 4.5) В.

· рабочий диапазон АЦП – (0 … 3) В.

Напряжение смещения будет равно -4.5 В. Коэффициент передачи петли обратной связи будет равным:

![]()

Коэффициент усиления будет равен:

![]()

Т.о. если задать один из резисторов, можно легко вычислить величину двух других.

Рис.1

Использовать дополнительные регистры для хранения данных, выдаваемых АЦП, ненужно, поскольку заданный АЦП имеет внутренний трёхстабильный регистр. Однако для корректной подачи сигнала прерывания, свидетельствующего об обновлении данных на выходе АЦП, на вход МП и сброса этого сигнала нам потребуется обычный D-триггер, на тактовый вход которого подается сигнал готовности данных с выхода ![]() АЦП. Триггер должен переключаться в единичное состояние по заднему фронту тактового импульса, т.е. при изменении уровня L

-

H

. Во время поступления сигнала чтения из порта, данные из внутреннего регистра АЦП поступают на шину данных ЦП. Одновременно с этим сбрасывается сигнал прерывания, путем установки триггера в нулевое состояние. Во время обработки ЦП очередного отсчета АЦП должно находиться в 3 состоянии, т.е. не нагружать шину данных ЦП, для чего на вход

АЦП. Триггер должен переключаться в единичное состояние по заднему фронту тактового импульса, т.е. при изменении уровня L

-

H

. Во время поступления сигнала чтения из порта, данные из внутреннего регистра АЦП поступают на шину данных ЦП. Одновременно с этим сбрасывается сигнал прерывания, путем установки триггера в нулевое состояние. Во время обработки ЦП очередного отсчета АЦП должно находиться в 3 состоянии, т.е. не нагружать шину данных ЦП, для чего на вход ![]() АЦП должен быть подать сигнал высокого уровня.

АЦП должен быть подать сигнал высокого уровня.

Для согласованной работы ОЗУ, ПЗУ и ЦП выберем микросхемы памяти, которые имеют несколько разрешающих входов и поддерживают трёхстабильное состояние. Для нашего случая наиболее подходящими являются микросхемы:

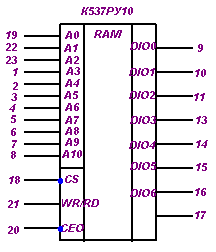

· RAM- K537РУ17, имеющая организацию 8192 слов ![]() 8 разрядов, а также необходимые нам входы:

8 разрядов, а также необходимые нам входы:

- выбор микросхемы ![]()

- разрешение по выходу ![]()

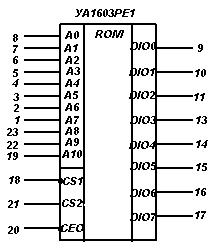

· ROM- К1603РЕ1. Организация- 2048 слов ![]() 8 разрядов.

8 разрядов.

Дополнительные входы:

- выбор микросхемы ![]()

- сигнал разрешения выхода ![]()

![]()

Таблицы истинности обеих микросхем и их более подробное описание приведены в приложении.

В связи с тем, что обе микросхемы памяти выполнены по КМОП технологии, можно отказаться от использования буферных регистров КП580ИП82/ИП83 в ЦП, поскольку нагрузочной способности шин адреса (ША) и данных МП вполне достаточно для обеспечения нормальной работы устройства в целом.

Выбор ОЗУ или ПЗУ при поступлении сигнала чтения памяти от ЦП удобней всего осуществить, используя 11-ю линию А11 ША (см. рис.2). При этом обращение к ПЗУ происходит при подаче процессором сигнала чтения памяти и наличия на ША адреса ячейки в диапазоне ![]() . В остальных случаях ПЗУ находиться в 3 состоянии.

. В остальных случаях ПЗУ находиться в 3 состоянии.

Для обращения к ОЗУ ЦП должен сформировать сигнал читать (или записать) и на ША выставить адрес ячейки ОЗУ в диапазоне ![]() . В остальных случаях ОЗУ также находиться в 3 состоянии.

. В остальных случаях ОЗУ также находиться в 3 состоянии.

Для обмена данными с внешним устройством организуем порт вывода, представляющий собой обычный 8- разрядный регистр с защелкой. Сигналом готовности данных внешнему устройству может служить сигнал вывода в порт ЦП.

Анализируя всё выше перечисленное можно составить общую структурную схему устройства.

Рис.2

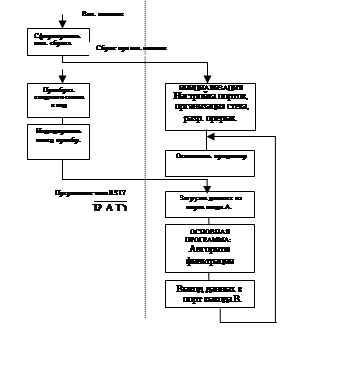

4. Разработка и обоснование общего алгоритма функционирования устройства и его описание.

При включении питания или перезагрузке цифровое устройство должно автоматически настроиться на работу. Для этого аппаратно реализуется схема запуска, которая обнуляет программный счетчик при запуске устройства или при кратковременном сбое питания. Кроме этого необходимо программно настроить порты ввода- вывода, установить маски прерываний (данная функция не поддерживается МП ВМ80А), организовать стек для хранения данных во время выполнения подпрограмм. Этими задачами занимается программа инициализации.

Вторым этапом работы обобщённого алгоритма является основная программа- алгоритм фильтрации.

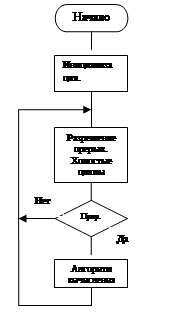

Обобщённый алгоритм функционирования устройства представлен на рис.3

Данные в аккумулятор загружаются из порта ввода по приходу сигнала прерывания RST 7. Работать с прерываниями намного выгоднее, чем реализация постоянного опроса порта о факте наличия данных, поскольку при этом снижаются аппаратные затраты и повышается быстродействие устройства. С учетом этого укрупненный алгоритм функционирования основной программы изображён на рис.4

Аппаратно- реализуемые операции Програмно- реализуемые операции

Рис.3

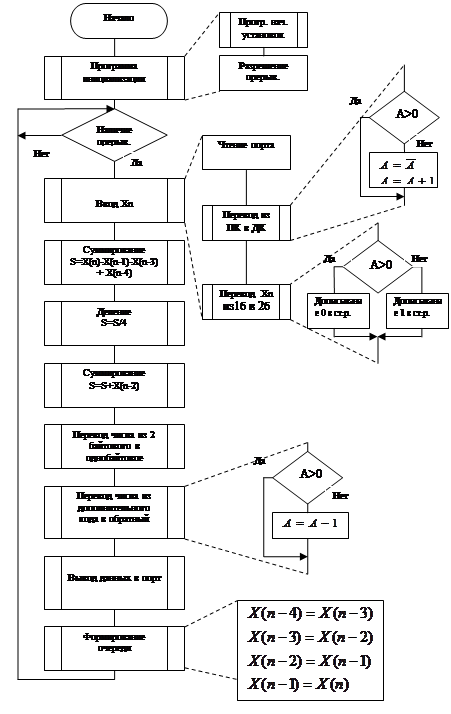

После загрузки данных выполняется основная программа, реализующая алгоритм фильтрации согласно заданному линейно разностному уравнению:

После загрузки данных выполняется основная программа, реализующая алгоритм фильтрации согласно заданному линейно разностному уравнению:

![]()

Анализируя данное уравнение можно отметить следующее:

· в связи с наличием отрицательных единичных коэффициентов организуем подпрограмму инвертирования знака числа.

процедуру деления на 4 проще всего будет выполнить путём двух последовательных арифметических сдвигов вправо. Арифметический сдвиг выгоднее заменить логическим, поскольку при этом сокращается время выполнения программы. На точность вычислений данный переход не повлияет, поскольку перед выводом данных мы переходим к однобайтовой форме представления чисел.

· поскольку при вычислении очередного значения Y(n) используются четыре предыдущих значения входных отсчетов, выгоднее всего использовать подпрограмму формирования очереди, т.е. сдвига поступающих отсчетов, вызываться, которая будет непосредственно после вывода данных в порт.

· В связи с тем, что используемый нами АЦП выдает данные в прямом коде, после операции ввода необходимо перевести код АЦП в код МП, т.е.в дополнительный код.

· Т.к. по заданию выходные данные требуется представить в обратном параллельном коде, перед выводом данных в порт переведем их из дополнительного в обратный код.

С учетом особенностей используемого МП следует обратить внимание на то что:

· Для повышения точности вычислений, перейдем от однобайтового представления числа к двухбайтовому. Данный переход сделаем сразу после ввода данный из порта.

· Перед выводом данных придется обратно перейти к однобайтовому представлению чисел, т.е. масштабировать полученный результат.

Алгоритм работы программной части синтезируемого устройства изображен на рис.5

Рис.5

5. Разработка программы

По описанному в п.4 алгоритму разработаем программу на языке микропроцессора.

Разрабатываемая программа должна полностью соответствовать требованиям, предъявленным к ней в предыдущих пунктах. Кроме этого, в целях повышения быстродействия, вычисление заданного линейно разностного уравнения должно выполняться с максимальной скоростью, т.е. за наименьшее число машинных тактов.

Текст разработанной программы:

Курсовая работа

на тему: Цифровой корректирующий фильтр

выполнил: ст.гр. 116 Сидорочкин Д.В.

Программа фильтрации сигнала.

исходные данные

линейное разностное уравнение Y(n-2)=[X(n) - X(n-1) + 4X(n-2) - X(n-3)+ X(n-4)]/4 = [X(n) + [- X(n-1)] + [-X(n-4)]]/4 + X(n-2)

частота дискретизации Fд = 6 (кГц)

входной сигнал - аналоговый, диапазон изменения (-4.5..+4.5)В

аналого-цифровой преобразователь - К1108ПВ1

выходной сигнал - 8-разрядный параллельный обратный код

микропроцессор - КР580ВМ80А

Программа на языке ассемблера.

SPACESON

ADRSP:.EQUFFFH

PORTIN1:.EQU001H

PORTOUT:.EQU002H

DATA

X:DW00H

Y:.DW00H

Z:DW00H

XN: DW00H

XN_1:DW00H

XN_2:.DW00H

XN_3: DW00H

XN_4: .DW00H

XN_01: .DW00H

XN_03: .DW00H

S: .DW00H

CODE

;-------------------------------------

;Подпрограмма начальных установок.

BGN:MACRO

LXISP,ADRSP

ENDM

;-------------------------------------

;Подпрограмма ввода числа "X" из порта в аккумулятор и преобразование его в дополнительный код с последующим переводом в 2-х байтное число. Результат записывается по адресу Х.

VVX:MACROX

INPORTIN1

PC_DC

1B_2B

SHLDX

ENDM

;-------------------------------------

;Подпрограмма перевода числа из кода АЦП в дополнительный код.

PC_DC:MACRO

RAL

JNCC1#

CMA

ADI02H

C1#:RAR

ENDM

;-------------------------------------

;Подпрограмма перевода 1-но байтного числа в 2-х байтное.

1B_2B:MACRO

MOVL,A

RAL

SBBA

MOVH,A

ENDM

;-------------------------------------

;Подпрограмма суммирования 2-х чисел, находящихся по адресу X и Y. Результат выводится по адресу Z.

SUM:MACROX,Y,Z

LHLDX

XCHG

LHLDY

DADD

SHLDZ

ENDM

;-------------------------------------

;Деление на 4-е. Делимое находится в регистровой паре HL. Результат выводится по адресу X.

DELEN4:MACROX

MOVA,H

RAR

MOVH,A

MOVA,L

RAR

MOVL,A

MOVA,H

RAR

MOVH,A

MOVA,L

RAR

MOVL,A

SHLDX

ENDM

;-------------------------------------

Перевод 2-х байтного числа в1-но байтное. Исходные данные находятся в регистровой паре HL. Результат находится в аккумуляторе.

2B_1B:MACRO

MOVA,H

RAR

MOVH,A

MOVA,L

RAR

ENDM

;-------------------------------------

;Перевод результата вычислений из дополнительного кода в обратный. Исходные данные и результат находятся в аккумуляторе.

DC_OK:MACRO

RAL

JNCD1#

RAR

SUI1H

RAL

CMA

D1#:RAR

ENDM

;-------------------------------------

;Вывод результата, находящегося в аккумуляторе, в порт.

OUTPUT:MACRO

OUT PORTOUT

ENDM

;-------------------------------------

;Формирование очереди.

OCHARED:MACRO

LHLD XN_3

SHLD XN_4

LHLD XN_2

SHLD XN_3

LHLD XN_1

SHLD XN_2

ENDM

;-------------------------------------

;Подпрограмма изменения знака числа на противоположный.

ENVERT:MACROX,Y

LDAX

CMA

INR A

1B_2B

SHLDY

ENDM

;-------------------------------------

INIT: MACRO

BGN

EI

HLT

ENDM

;-------------------------------------

Основная программа.

ORG 0H

INIT

ORG 38H

JMP A1

ORG 50H

A1:VVXXN

ENVERT XN_1,XN_01

ENVERT XN_3,XN_03

SUMXN,XN_4,S

SUMS,XN_01,S

SUMS,XN_03,S

DELEN4S

SUMS,XN_2,S

2B_1B

DC_OK

OUTPUT

OCHARED

EI

HLT

.END

6. Оценка быстродействия устройства

Быстродействие устройства определяется временем, затрачиваемым микропроцессором на выполнение команд. Время выполнения определяется тактовой частотой микропроцессора и количеством тактов затрачиваемых на выполнение команды.

После прихода команды прерывания RST 7 на МП, выходной отсчет появляется максимум через 840 тактов процессора.

Время выполнения считается с момента прихода импульса дискретизации до выдачи результата y(n).

Твып =Nтактов *Tтакта

Рассмотрим случай самого длинного выполнения.

Твып =870*0.4=348 мкс.

Т.к. в нашем случае используется АЦП нужно учесть задержку при преобразовании сигнала из аналогового в цифровой. Для АЦП К1108ПВ1 задержка составляет порядка 10мкс. Следовательно:

Твып =(Nтактов *Tтакта )+ТЗадАЦП

Твып =348+10=358 мкс

Для нормальной работы устройства необходимо, чтобы фильтр успевал закончить обработку до начала следующего цикла фильтрации. Другими совами частота обработки отсчетов должна превышать частоту дискретизации.

Fо > Fд или То < Тд

Заданная частота дискретизации Fд=6 кГц

Tд=1/Fд=166,7 мкс

.

Быстродействие полученного устройства позволяет обрабатывать данные, приходящие с частотой дискретизации не более 2.8 кГц. Поскольку частота дискретизации входного сигнала Fд=6 кГц проектируемый фильтр будет работать некорректно, поскольку во время обработки очередного отсчёта будет проигнорировано как минимум два последующих отсчета, что приведет к нарушению общего алгоритма фильтрации.

7. Отладка разработанной программы. Результаты отладки

Отладка разработанной программы проводилась на ЭВМ с соответствующим программным обеспечением. По окончании отладки были исправлены логические ошибки и получена работоспособная программа.

Вручную были рассчитаны контрольные точки, а затем проверены на ЭВМ. Проверка дала следующие результаты:

Для упрощения процесса проверки в память введём значения отсчётов X(n-1), X(n-2), X(n-3) и X(n-4). Для проверки работоспособности программы, как с положительными, так и с отрицательными числами, значения отсчётов зададим разных знаков. Т.о. перед выполнением программы в ОЗУ содержатся следующие исходные данные:

| переменные |

число |

прямой |

дополнительный |

| Код |

код |

||

| (xn -1 ) |

10 |

0А |

000Ah |

| xn-2 |

5 |

05 |

0005h |

| (xn-3 ) |

-8 |

88h |

FFF8h |

| xn-4 |

-12 |

8Ch |

FFF4h |

В аккумулятор записываем значение 1С

Вычислим результат вычисления линейно разностного уравнения:

![]()

В ходе выполнения программы в ячейки памяти с адресом отсчёта Y(n-2) записывается значение 8h, Значение Y(n-2), выводимое в порт, оказывается равным 4h. Объясняется это переходом перед выводом данных к однобайтовой форме представления чисел.

Т.о. результаты работы программы, с учетом особенностей работы М.П.., полностью совпадают с результатами ручного просчёта.

8. Составление принципиальной схемы устройства и ее описание

При разработки принципиальной схемы следует учесть предъявленные к ней требования, а также для уменьшения стоимости устройства и повышения его быстродействия необходимо стремиться к уменьшению числа используемых микросхем.

В качестве операционного усилителя, который масштабирует и сдвигает входной аналоговый сигнал, возьмём ОУ общего применения марки К140УД14А.

Триггер, обеспечивающий подачу сигнала готовности данных М.П., должен иметь инверсные входы R (вход установки в 0 состояние) и С (тактовый вход). Этим условиям удовлетворяет триггер К555ТМ2. Более подробное его описание приведено в приложении.

Выбор микросхем памяти был описан в п.3. Т.е.

· RAM- KP537РУ17,

· ROM- КA1603РЕ1.

В качестве регистра, служащего портом вывода данных возьмем КР1533ИР23.

Остальные элементы схемы были даны в задании к курсовому проекту. Т.е. М.П. ВМ80А, генератор тактовых импульсов и системный контролер, являющиеся частью комплекта КП580ВМ80А.

Принципиальная электрическая схема корректирующего фильтра приведена в приложении.

9. Заключение.

В данной курсовой работе была построена схема цифрового устройства и разработана программа, обеспечивающая работу данного устройства как цифрового корректирующего фильтра. Цифровые фильтры имеют свои преимущества и недостатки перед аналоговыми.

Аналоговые фильтры физически реализуемы, если в их передаточных функциях степень полинома числителя не выше степени полинома знаменателя. Цифровые фильтры не предъявляют таких ограничений, и, таким образом, они могут иметь характеристики, добиться которых в аналоговых фильтрах невозможно.

К недостаткам цифрового фильтра можно отнести неточность представления коэффициентов вследствие ограниченной разрядности процессора.

Разработанное устройство обладает недостаточным быстродействием см.п.6

Необходимость в высоком быстродействии связана со стремлением обрабатывать в реальном масштабе времени широкополосные сигналы. Из создавшейся ситуации возможны несколько выходов.

1. Уменьшить время выполнения программы за счет реализации некоторых операций, выполняемых программой (перевод из прямого кода в дополнительный, из дополнительного в обратный) аппаратными средствами. Однако это приведет к повышению стоимости устройства , что является нежелательным.

2. Уменьшить частоту дискретизации входного сигнала, но это возможно лишь в том случае, если Fд>Fв, где Fв- верхняя частота сигнала. Если же частота Fд выбрана в соответствии с теоремой Котельникова, т.е. Fд=Fв, уменьшение Fд приведёт к потери информации при восстановлении сигнала.

3. Увеличить тактовую частоту М.П. Однако используемый М.П. ВМ80А не поддерживает увеличение тактовой частоты выше 2.5 МГц.

Анализируя всё выше изложенное можно сделать вывод, что реализовать работоспособное устройство, выполняющее требуемые функции над цифровым сигналом с частотой Fд=6кГц, на базе комплекта КП580ВМ80А невозможно.

10. Список использованных источников

1. Цифровые устройства и микропроцессоры: Методические указания к курсовой работе. /Сост. Н.И.Сальников, -Рязань :РРТИ, 1990. № 1767.

2. Локтюхин В.Н., Лебединская Г.М. Микропроцессорные вычислительные устройства :Методич. указания к курсовой работе./РРТИ. -Рязань, 1988.

3. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. -М. :Радио и связь, 1989.

4. Большие интегральные схемы запоминающих устройств :Справочник. /А.Ю.Гордонова, Н.В.Бекин и др.; Под ред. А.Ю.Гордонова и Ю.Н.Дьякова. -М. :Радио и связь, 1990.

5. Федорков Б.Г., Телец В.А. 0 Микросхемы ЦАП и АЦП :функционирование, параметры, применение. -М. :Энергоатомиздат, 1990.

11. Приложение

Описание структурной схемы микросхемы КА1603РЕ1

Микросхема КА1603РЕ1- постоянное запоминающее устройство, предназначенное для хранения и считывания информации, записанной в процессе изготовления микросхемы.

Структурная схема КА1603РЕ1 содержит входной адресный регистр, состоящий из 11 триггеров; дешифратор строк на семь разрядов и дешифратор столбцов на четыре разряда; накопитель, организованный в виде 8 подматриц, каждая из которых содержит 2048 бит. К каждой подматрице подключены отдельные цепи считывания. Кроме того, микросхема содержит схемы управления, которые вырабатывают управляющие сигналы, необходимые для запоминания и дешифрации адреса, а также считывания сигналов информации.

Назначение выводов микросхемы КА1603РЕ1

| Выводы |

Назначение |

Обозначение |

| 1-8, 19, 22, 23 |

Адресные входы |

А7-А0, А10, А9, А8 |

| 9-11, 13-17 |

Входы-выходы данных |

DIO0-DIO2, DIO3-DIO7 |

| 18, 21 |

Выбор микросхемы |

|

| 20 |

Разрешение по выходу |

|

| 24 |

Напряжение питания |

Ucc |

| 12 |

Общий |

0В |

Таблица истинности микросхем КА1603РЕ1

|

|

|

|

А0-А10 |

DIO0-DIO7 |

Режим работы |

| M |

M |

H |

X |

Roff |

Хранение |

| L |

H |

H |

A |

Roff |

Хранение |

| L |

H |

L |

A |

Данные в прямом коде |

Запрет выхода |

M- ЛЮБАЯ КОМБИНАЦИЯ ЛОГИЧЕСКИХ УРОВНЕЙ СИГНАЛОВ, ОТЛИЧНАЯ ОТ

![]() .

.

Описание структурной схемы микросхемы КР537РУ17

Микросхема состоит из накопителя на 2048*8 бит, выполненного на КМОП- элементах памяти, формирователей адреса строк и столбцов, предназначенных для согласования ОЗУ по входу с уровнями ТТЛ- схем, дешифратора адреса строк на 8 входов и 256 выходов, дешифратора адреса столбцов на 4 входа и 16 выходов, предназначенных для выбора необходимого слова из накопителя.

Микросхема состоит из накопителя на 2048*8 бит, выполненного на КМОП- элементах памяти, формирователей адреса строк и столбцов, предназначенных для согласования ОЗУ по входу с уровнями ТТЛ- схем, дешифратора адреса строк на 8 входов и 256 выходов, дешифратора адреса столбцов на 4 входа и 16 выходов, предназначенных для выбора необходимого слова из накопителя.

Разрядная схема предназначена для записи и считывания информации в накопитель.

Усиление входных- выходных сигналов до необходимых уровней (уровней ТТЛ) осуществляется с помощью выходных формирователей, содержащих усилители считывания.

Назначение выводов микросхемы КР537РУ1 7

| Выводы |

Назначение |

Обозначение |

| 2, 3-10, 21, 23, 24, 25 |

Адресные входы |

A12, A7-A0, A10, A11, A9, A8 |

| 11, 12, 13, 15-19 |

Входы-выходы данных |

DIO0-DIO2, DIO3-DIO7 |

| 20, 26 |

Выбор микросхемы |

|

| 22 |

Разрешение по выходу |

|

| 27 |

Сигнал записи- считывания |

|

| 28 |

Напряжение питания |

Ucc |

| 14 |

Общий |

0В |

Таблица истинности микросхем КР537РУ1 7

|

|

|

|

|

А0-А112 |

DIO0-DIO7 |

Режим работы |

| H |

X |

X |

X |

X |

Roff |

Хранение |

| L |

H |

X |

L |

A |

L |

Запись |

| L |

H |

X |

L |

A |

H |

Запись |

| L |

H |

L |

H |

A |

Данные в прямом коде |

Считывание |

| L |

H |

H |

H |

A |

Roff |

Запрет выхода |

Микросхема К1108ПВ1.

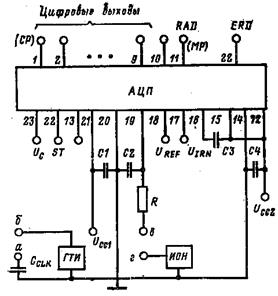

Микросхема 10-разрядного быстродействующего функционально законченного АЦП последовательного приближения К1108ПВ1 (А, Б) предназначена для преобразования аналогового сигнала в двоичный параллельный цифровой код. В состав функциональной схемы преобразователя входят ИОН, ГТИ, выходной регистр с тремя логическими состояниями и функцией хранения информации в течение одного цикла преобразования ВРг РПП, ЦАП, многовходовый КН с входным резисторным вычитающим устройством, дешифратором ДШ уровней тока и др. Микросхема рассчитана на преобразование однополярного входного напряжения в диапазоне от О до З В, подаваемого на вход через внешний ОУ или УВХ при максимальной частоте преобразования 1,1 МГц для 10-разрядного ре жима и 1,33 МГц для 8-разрядного режима. Микросхема К1108ПВ1 размещена в герметичном металлокерамическом корпусе типа 210В.24-1 с двухсторонним вертикальным расположением выводов.

Для работы АЦП К1108ПВ1 требуется несколько внешних керамических конденсаторов и источники напряжения Ucc1 =5В ±5% и Ucc2 =5,2В ±5%. Номинальное значение напряжения внутреннего ИОН составляет 2,5 В. Мощность, потребляемая от источников питания, не превышает 0,85 Вт.

Рис. Функциональная электрическая схема БИС АЦП К1108ПВ1.

Нумерация и назначение выводов микросхемы:

1 - цифровой выход 1 (СР);

2-9-цифровые выходы 2—9;

10 - цифровой выход 10 (МР);

11 - готовность данных ![]() ;

;

12 - напряжение источника питания Ucc2 (цифровая часть);

13- укороченный цикл ![]() ;

;

14 - общий (цифровая земля);

15 - напряжение источника питания Ucc2 (аналоговая часть);

16 - коррекция СУ ЕС1 ;

17 - аналоговый вход![]() ;

;

18 - внешний ИОН ![]() ;

;

19 - коррекция ОУ ИОН FС2 ;

20 - общий (аналоговая земля);

21 - напряжение источника питания Ucc1 ;

22 - запуск ![]() ;

;

23 - такт CLK;

24 - разрешение считывания ![]() .

.

Основные электрические параметры при температуре окружающей среды 25 0 С

Не менее Не более

Число разрядов 10 -

Время преобразования tc , мкс - 0.9

Частота преобразования fc ,МГц 0.41.5

Время преобразования в режиме укороченного

цикла tc 8, мкс- 0.75

Выходное напряжение внутреннего ИОН

![]() ,В 2.42.8

,В 2.42.8

Ток потребления Iсс1, мА - 50

Ток потребления Iсс2 мА- 130

Выходное напряжение низкого уровня ![]() , В - 0.4

, В - 0.4

Выходное напряжение высокого уровня ![]() , В 2.4-

, В 2.4-

Ток потребления от внешнего источника

опорного напряжения Iсс3, мА - 7

Преобразователь изготавливается по биполярной технологии с изоляцией р-n переходами и совмещенными прецизионными тонкопленочными резисторами. Технологические и схемотехнические особенности построения БИС обеспечили ей высокое быстродействие и стабильность статических параметров. Необходимый уровень нелинейности и выходного напряжения достигается за счет применения лазерной подгонки тонкопленочных резисторов.

Цифровая часть БИС АЦП выполнена с применением низкоуровневых дифференциальных токовых переключателей на основе трехуровневых логических элементов.

Внутренний ИОН состоит из опорного элемента на нескольких прямосмещенных р-n перёходах и стабилизирующего усилителя. В аналоговой части БИС используется многовходовый КН.

Основное отличие структурного построения АЦП К1108ПВ1 от классического АЦП ПП заключается в раз делении внутреннего ЦАП на две части (статическую и динамическую), введения селектора опорных уровней на дифференциальных парах идентичных транзисторов и коммутатора управляющих токов селектора.

Жесткая связь крутизны передаточной характеристики АЦП с значениями![]() а также возможность использования внешнего ИОН позволяют применять БИС К1108ПВ в режиме умножения в пределах 10 % зоны относительно номинального значения

а также возможность использования внешнего ИОН позволяют применять БИС К1108ПВ в режиме умножения в пределах 10 % зоны относительно номинального значения

![]() =2,5 В.

=2,5 В.

Динамические свойства АЦП в умножающем режиме определяются быстродействием внутреннего стабилизирующего ОУ, частота которого без подключения внешних элементов коррекции составляет не менее 3—5 МГц.

Комбинированное структурное построение АЦП К1108ПВ1 определяет и внешний вид передаточной характеристики, у которой восемь однородных участков повторяются через 128 ступеней, причем ступени на границах участков (в местах «сшивания» ЦАП старших и младших разрядов) наиболее чувствительны к процессу настройки.

Рассмотренные структурно-схематические построения аналоговой части АЦП значительно повысили его быстродействие, поскольку:

1) переходные процессы, связанные с переключением эталонов трех старших разрядов, отсутствуют;

2) входной ток АЦП протекает через ЦАП младших разрядов, что позволяет уменьшить сопротивление входного резистора в 8 раз по отношению к классическому АЦП ПП и уменьшить постоянную времени установления на выходе ЦАП. Одновременно снижается уровень влияния шумов ЦАП;

3) при сравнении трех старших разрядов коммутируемый ток протекает только по внутренним цепям кристалла, за счет чего исключаются переходные процессы в соединительных проводниках.

Цикл преобразования в режиме 10-разрядного АДП состоит из 12 тактов (десять рабочих в процессе кодирования и по одному служебному в начале и в конце цикла преобразования).

Цикл начинается с первым отрицательным фронтом после поступления команды на запуск ![]() . Во время первого служебного такта осуществляется сброс регистров и установление напряжения на входе селектора опорных уровней.

. Во время первого служебного такта осуществляется сброс регистров и установление напряжения на входе селектора опорных уровней.

В течение следующих десяти тактов происходит кодирование аналогового сигнала при условии, что он зафиксирован на входе АЦП. Благодаря тому, что сброс КН проводятся в конце каждого такта, вход преобразователя нечувствителен к импульсным помехам, действующем на протяжении 2/3 его длительности.

В двенадцатом такте код из регистра хранения переписывается в выходной регистр, после чего формируется сигнал готовности данных. Появление на выходе ![]() (вывод 11 сигнала логический О свидетельствует о смене информации в выходном регистре и ее хранении весь следующий цикл преобразования.

(вывод 11 сигнала логический О свидетельствует о смене информации в выходном регистре и ее хранении весь следующий цикл преобразования.

Для считывания информации необходимо подать на вход ![]() (вывод 24) сигнал логический О. При подаче на этот вход сигнала логическая 1 информационные выходы АЦП переводятся в третье состояние, в котором шина данных МП не нагружается. Одновременно с появлением импульса готовности данных можно производить выборку аналогового сигнала на входе АЦП.

(вывод 24) сигнал логический О. При подаче на этот вход сигнала логическая 1 информационные выходы АЦП переводятся в третье состояние, в котором шина данных МП не нагружается. Одновременно с появлением импульса готовности данных можно производить выборку аналогового сигнала на входе АЦП.

В БИС К1108ПВ1 предусмотрен 8-разрядный режим работы, т.е. с сокращением цикла кодирования на два такта (вход SЕ 10/8 соединяется с шиной отрицательного источника питания).

Запуск АЦП можно считать устойчивым, если сигнал ![]() подается в течение одного периода тактовой частоты. с момента начала очередного цикла. При асинхронном режиме запуска (по отношению к тактовому сигналу) длительность сигнала

подается в течение одного периода тактовой частоты. с момента начала очередного цикла. При асинхронном режиме запуска (по отношению к тактовому сигналу) длительность сигнала ![]() должна быть не менее двух ее периодов. При этом задержка запуска АЦП (относительно фронта сигнала

должна быть не менее двух ее периодов. При этом задержка запуска АЦП (относительно фронта сигнала ![]() ) зависит от текущего положения фронтов и может достигать длительности одного периода тактовой частоты.

) зависит от текущего положения фронтов и может достигать длительности одного периода тактовой частоты.

Если после окончания очередного цикла преобразования на входе ![]() сохраняется уровень логического О, то начинается новый цикл.

сохраняется уровень логического О, то начинается новый цикл.

Порядок подключения источников питания к АЦП произвольный, однако при этом недопустимо включать источник даже кратковременно, если на входе не предусмотрены специальные схемы защиты от превышения уровня ![]() .

.

Типовая схема включения БИС АЦП К11О8ПВI.

С1=1 мкФ; С2=0,47 мкФ (керамический); С3=0,1 мкФ; С4=1 мкФ (керамический); R=100 Ом