| Скачать .docx |

Реферат: Программирование контроллера приёма, задержки и выдачи информации

![]() ВОЕННАЯ АКАДЕМИЯ СВЯЗИ

ВОЕННАЯ АКАДЕМИЯ СВЯЗИ

Курсовой проект

по дисциплине “Организация ЭВМ и систем”.

“Программирование контроллера приёма, задержки и выдачи информации ”.

Выполнили: мл.сержант 4382 уч.гр.

Москвичёв К.С.

курсант 4382 уч.гр.

Мухамадеев Т.В.

Проверил: преподаватель каф.20

Ладис Д.И.

Санкт-Петербург 2011г.

1. Задание.

Контроллер по запросу от управляемого объекта должен вызвать подпрограмму приёма в параллельном или последовательном коде N-байтов управляющего сообщения, в котором указывается произвольный управляющий шеснадцатиричный код, и записать его в модуль оперативной памяти. Затем перейти к подпрограмме временной задержки, реализуемую таймером. После истечения заданного времени задержки контроллер должен перейти к подпрограмме выдачи N-байтов принятого и задержанного управляющего сообщения в последовательном или параллельном коде в управляемый объект. Способ приёма и выдачи управляющей информации, время задержки указываются в варианте проекта.

Вариант № 6.

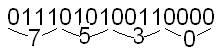

Порт приёма : 1a1a2a4c4

Таймер: 2Cч 2б2б7б10т15

Порт выдачи: 3в1в9в12в13в15в19

2. Цели проекта.

1. Разработать функциональную схему контроллера на основе БИС микропроцессорного комплекса 580 серии.

2. Разработать программу работы модулей (БИС) проектируемого контроллера.

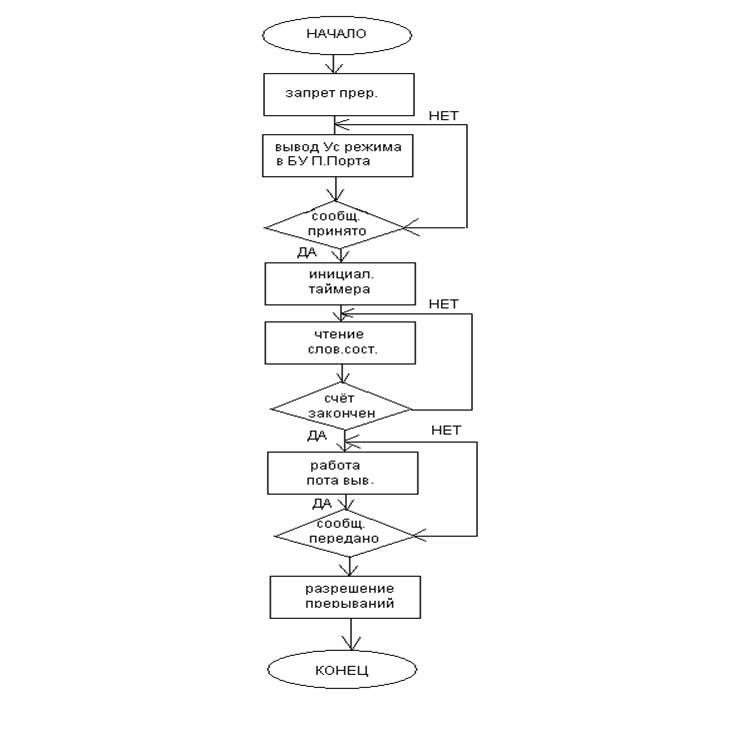

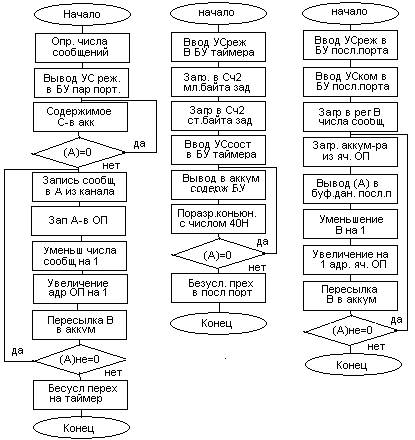

3. Блок схема алгоритма работы контроллера

- Вычисление УС параллельного порта и слова для сравнения, время задержки для таймера, УС1

УС2

для таймера, УСреж. последовательного порта, УСком. последовательного порта.

Параллельный порт производит приём байтов в режиме 0 по каналу А с единичным значением по 4-му разряду канала С.

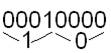

УС 0-го режима параллельного порта

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

D7- признак УС1

D6,D5 – режим 0 канала А

D4 – ввод по каналу А

D3 – ввод старших разрядов канала С

D2 – режим 0 канала В

D1 – режим ввода по каналу В

D0 – ввод младших разрядов канала С

![]()

- Управляющее слово параллельного порта = 99H .

- Слово для сравнения = 10H .

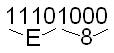

УС режима работы таймера

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

D7,D6 – номер счётчика

D5,D4 – запись младших и старших байтов Ксч

D3,D2,D1 – режим 1

D0 - 16-тиричная система

![]()

- УС режима работы таймера = 82H

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

D7,D6 – команда READBACK

D5,D4 – считывание СС

D3,D2,D1 – по второму счётчику

D0 – безразлично(не используется)

- УС состояния таймера = Е8H

Определение Ксч = Tзадержки х Fработы.сч

15х10-3 с х 2х106 Гц=30х103 раз.

- задержка 7530H

УС режима последовательного порта

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

D7,D6 – асинхронный режим с длительностью стоп бита 2Тх

D5 – контроль по чету

D4 – наличие контроля

D3,D2 – длинна символа 8-ми разрядов

D1,D0 – скорость передачи данных 1-64

![]()

- УС режима последовательного порта = FFH

УС команды последовательного порта

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

D7 – ввод режима поиска синхросимволов отменён (ЕN )

D6 – программный сброс адаптера (IR )

![]() D5 – запрос готовности приёмника БУ принять данные (RTS)

D5 – запрос готовности приёмника БУ принять данные (RTS)

D4 – сброс ошибок в СС (ЕR )

D3 – формирование низкого уровня на входе TxD

D2 – запрет приёмника (RxEN)

D1 – нет запроса готовности БУ выдать данные в порт

D0 – передача разрешения

![]()

- УС команду последовательного порта = 15H

5.Программа работы контроллера

| АДРЕС | КО | КОММЕНТАРИЙ | ||||

| Работа порта приёма | ||||||

| 0А00 | F3 | запрет прерываний. | ||||

| 0А01 | 06 | (В2)-рег.(В) MVI B | ||||

| 0А02 | 05 | количество байт инф. принимаемых в порту. | ||||

| 0А03 | 16 | (В2)-рег.(D) MVID | рег DE содержат адрес ОП куда надо записать данные | |||

| 0А04 | OB | старший разряд адреса ячейки памяти. | ||||

| 0А05 | 1E | (В2)-рег.(Е) MVI E | ||||

| 0А06 | FF | младший разряд адреса ячейки памяти. | ||||

| 0А07 | 3E | MVIA (следующий байт в аккумулятор) | загр. В аккум УС парал.порта | |||

| 0А08 | 99 | УС реж. параллельного порта | ||||

| 0А09 | D3 | OUT (вывод УС из аккум. В БУ) | загр. УС из аккум. в БУ парал.порта | |||

| 0А0А | 9B | БУ пар.порта | ||||

| 0А0В | DB | IN (загрузка содержимого канала С в аккум) | цикл проверяющий готовность порта принимать информацию если 4-ый разряд канала С 1- готов 0-не готов. |

|||

| 0А0С | 9A | адрес канала С | ||||

| 0А0D | E6 | ANI (поразрядная конъюнкция) | ||||

| 0A0E | 10 | выделение 4-го разряда | ||||

| 0A0F | CA | JZ (A==0 ―› переход (В3 В2)) | условный переход | |||

| 0A10 | OB | L-младший байт перехода. | ||||

| 0A11 | OA | H-старший байт перехода. | ||||

| 0A12 | DB | IN (загрузка аккум. из В2) | загрузка содерж. рег. В2 по кан. А в аккум | |||

| 0A13 | 98 | адрес канала А | ||||

| 0A14 | 12 | STAX (A) ―›M по адр. в паре регистров (E)(D) | ||||

| 0A15 | 05 | DCRB (B)-1 | уменьшение на 1 адресов ОП рег. В Е | |||

| 0A16 | 1D | DCRE (E)-1 | ||||

| 0A17 | F8 | MOVA,B для сравнения (В) ―›(А) | сод. рег.В помещ. в аккум для послед ср. | |||

| 0A18 | C2 | JNZ (A≠0 ―› переход на В3 В2) | условный переход | |||

| 0A19 | OB | L-младший байт перехода | ||||

| 0A1A | 0A | H-старший байт перехода | ||||

| 0A1B | C3 | JMP―›B3B2 | безусловный переход на таймер | |||

| 0A1C | 00 | L-младший байт перехода | ||||

| 0A1D | 08 | H-старший байт перехода | ||||

| Работа таймера | ||||||

| 0800 | 3E | MVI A | загрузка в аккум. УС1 таймера | |||

| 0801 | 82 | УС1 таймера | ||||

| 0802 | 03 | OUT | вывод УС1 в БУ таймера | |||

| 0803 | 72 | адрес БУ таймера | ||||

| 0804 | 3E | MVIA | загрузка данных по задержке в СЧ2 | |||

| 0805 | 0C | младший байт задержки | ||||

| 0806 | D3 | OUT | ||||

| 0807 | 71 | адрес СЧ2 | ||||

| 0808 | 3E | MVI A | ||||

| 0809 | 10 | старший байт задержки | ||||

| 080А | D3 | OUT | ||||

| 080В | 71 | адрес СЧ2 | ||||

| 080C | 3E | MVI A | загрузка в таймер УС2 для считывания СС | |||

| 080D | E8 | УС2 счётчика для считыв. СС | ||||

| 080E | D3 | OUT | ||||

| 080F | 72 | адрес БУ таймера | ||||

| 0810 | DB | IN | загрузка СС из БУ в аккумулятор | |||

| 0811 | 72 | адрес БУ таймера | ||||

| 0812 | E6 | ANI (поразрядная конъюнкция) | проверка окончания счёта 1-кон. 0-не конец | |||

| 0813 | 40 | выделение 6-го разряда | ||||

| 0814 | CA | JZ (A==0 ―› переход (В3 В2)) | сравнение аккум. с 0 если 0-переход 1-дальше. | |||

| 0815 | 10 | L-адр.перехода | ||||

| 0816 | 08 | H-адр.перехода | ||||

| 0817 | C3 | JMP | безусловный переход на порт выдачи | |||

| 0818 | 00 | L-адр.задержки | ||||

| 0819 | 09 | H- адр.задержки | ||||

| Работа порта выдачи | ||||||

| 0900 | 06 | MVI B | загрузка в параллельный порт управляющего слова режима и управляющего слова команды |

|||

| 0901 | 05 | кол-во байт информации | ||||

| 0902 | 1E | MVI E | ||||

| 0903 | FF | L разряда вдреса | ||||

| 0904 | 3E | MVI A | ||||

| 0905 | FF | УСреж. П- | ||||

| 0906 | D3 | OUT | ||||

| 0907 | 81 | адресБУП- | ||||

| 0908 | 3E | MVI A | ||||

| 0909 | 15 | УСком. П- | ||||

| 090A | D3 | OUT | ||||

| 090B | 81 | адресБУП- | ||||

| 090C | 1A | LDAX D,E | вывод информации в порт | |||

| 090D | D3 | OUT | ||||

| 090E | 81 | адресбуфера данныхП- | ||||

| 090F | 05 | DCRB (код кол-ва байт) | уменьшение В-1 Е-1 | |||

| 0910 | 1D | DCRE (мл. разряд адреса в ОП) | ||||

| 0911 | 78 | MOVA,B (из В в аакум.) | згр. из В в аккум | |||

| 0912 | C2 | JNZ (A≠0) ―› перех. на В3В2 | условный переход если А≠0 переход если А=0 след. ком. |

|||

| 0913 | 0C | L (мл.адрес перехода) | ||||

| 0914 | 09 | H (ст.адрес перехода) | ||||

| 0915 | F8 | Е1 (разрешение прерываний) | ||||

| 0916 | 76 | HTL (останов) | ||||

6. Схема контроллера.

7.Вывод:

Мы практически разработали функциональную схему контроллера на основе БИС микропроцессорного комплекса 580 серии и программу работы модулей проектируемого контроллера, который должен по запросу от управляемого объекта вызвать подпрограмму приёма в параллельном или последовательном коде N-байтов управляющего сообщения, в котором указывается произвольный управляющий шеснадцатиричный код, и записать его в модуль оперативной памяти. Затем перейти к подпрограмме временной задержки, реализуемую таймером. После истечения заданного времени задержки контроллер должен перейти к подпрограмме выдачи N-байтов принятого и задержанного управляющего сообщения в последовательном или параллельном коде в управляемый объект. Способ приёма и выдачи управляющей информации, время задержки указываются в варианте проекта.

Таким образом, проделав данную работу мы практически применили наши знания о модулях микропроцессорной ЭВМ. Закрепили знание команд микропроцессора В580ВМ80. Полностью разобрались с принципами составления управляющих слов портов ввода-вывода и таймера.