| Скачать .docx |

Курсовая работа: Курсовая работа: Проектирование вычислительного устройства

Содержание

1. Проектирование и синтезирование комбинационной схемы

2. Проектирование и синтезирование автомата Мили

3. Проектирование и синтезирование счетчика с коэффициентом пересчета на D-тригерах

4. Синтезирование вычислительного утройства для реализации алгоритма вычислений на дискретных элементах

1. Проектирование и синтезирование комбинационной схемы

Дана таблица истинности (табл. 1), где m0 …m15 -минтермы функции f :

Таблица 1

| № варианта |

m1 |

m2 |

m3 |

m4 |

m5 |

m6 |

m7 |

m8 |

m9 |

m10 |

m11 |

m12 |

m13 |

m14 |

m15 |

| 15 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| Группы |

Исходные минитермы |

Переменные |

Метка |

Импликанты |

|||

| X1 |

X2 |

X3 |

X4 |

||||

| S1-1 (m1 ) |

0 |

0 |

0 |

1 |

+ |

||

| S1-2 (m2 ) |

0 |

0 |

1 |

0 |

+ |

||

| S1-3 (m8 ) |

1 |

0 |

0 |

0 |

+ |

||

| S2-1 (m3 ) |

0 |

0 |

1 |

1 |

+ |

||

| S2-2 (m9 ) |

1 |

0 |

0 |

1 |

+ |

||

| S3-1 (m7 ) |

0 |

1 |

1 |

1 |

+ |

||

| S3-2 (m14 ) |

1 |

1 |

1 |

0 |

+ |

||

| S4-1 (m15 ) |

1 |

1 |

1 |

1 |

+ |

||

| S’1-1 |

S1-1 +S2-1 |

0 |

0 |

D |

1 |

P1 |

|

| S’1-2 |

S1-1 +S2-2 |

D |

0 |

0 |

1 |

P2 |

|

| S’1-3 |

S1-2 +S2-1 |

0 |

0 |

1 |

D |

P3 |

|

| S’1-4 |

S1-3 +S2-2 |

1 |

0 |

0 |

D |

P4 |

|

| S’2-1 |

S2-1 +S3-1 |

0 |

D |

1 |

1 |

P5 |

|

| S’3-1 |

S3-1 +S4-1 |

D |

1 |

1 |

1 |

P6 |

|

| S’3-2 |

S3-2 +S4-21 |

1 |

1 |

1 |

D |

P7 |

|

Составим таблицу простых импликант (табл.2):

Таблица 2

| Импликанты |

m1 |

m2 |

m3 |

m7 |

m8 |

m9 |

m14 |

m15 |

| P1 |

1 |

1 |

||||||

| P2 |

1 |

1 |

||||||

| P3 |

1 |

1 |

||||||

| P4 |

1 |

1 |

||||||

| P5 |

1 |

1 |

||||||

| P6 |

1 |

1 |

||||||

| P7 |

1 |

1 |

Минимальное покрытие f = P2+P3+P4+P5+P7.

Для проверки составим карту Карно:

|

|

|

||

|

|

|

1(m8 ) |

|

|

|

1(m15 ) |

|

|

|

|

|

|

1(m2 ) |

|

|

|

||

|

|

|

|

|

P2 = ![]() , P3 =

, P3 = ![]() ), P4 =

), P4 = ![]() , P5 =

, P5 = ![]() , P7 =

, P7 = ![]()

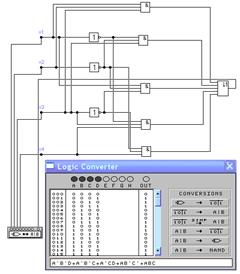

Реализация этой функции представлена на Рис.1:

Рис. 1

2. Проектирование и синтезирование автомата Мили

Дана таблица состояний (табл.3):

Таблица 3

| № варианта |

Состояния |

|||||||

| X = 0 |

X =1 |

|||||||

| 1 |

2 |

3 |

4 |

1 |

2 |

3 |

4 |

|

| 3,0 |

1,0 |

2,1 |

4,1 |

2,0 |

4,0 |

1,1 |

3,1 |

|

Составим таблицу переходов (табл.4):

Таблица 4

| y1 |

y2 |

X |

y1 t+1 |

y2 t+1 |

Z |

|

| 1 |

0 |

0 |

0 |

0 |

1 |

0 |

| 2 |

1 |

0 |

0 |

0 |

0 |

0 |

| 3 |

0 |

1 |

0 |

1 |

0 |

1 |

| 4 |

1 |

1 |

0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

0 |

0 |

| 2 |

1 |

0 |

1 |

1 |

1 |

0 |

| 3 |

0 |

1 |

1 |

0 |

0 |

1 |

| 4 |

1 |

1 |

1 |

0 |

1 |

1 |

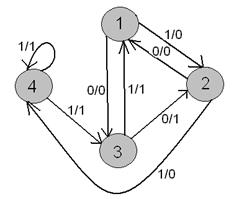

Отобразим таблицу перехода на графе (рис.2):

Рис. 2

Построим карты Карно:

| y1 t+1 |

y2 |

|

y2 |

|

| y1 |

0 |

1 |

0 |

1 |

|

|

0 |

1 |

0 |

1 |

| X |

|

|||

| y1 t+1 |

y2 |

|

y2 |

|

| y1 |

1 |

1 |

0 |

1 |

|

|

0 |

0 |

1 |

0 |

| X |

|

|||

| y1 t+1 |

y2 |

|

y2 |

|

| y1 |

1 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

1 |

| X |

|

|||

| y1 t+1 |

|

| y2 t+1 |

|

| Z |

y2 |

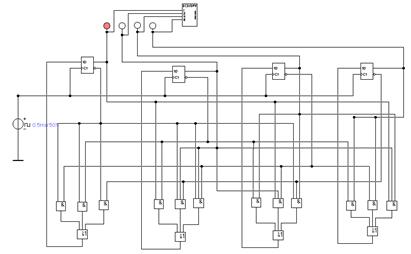

Построим схему в среде Electronics Workbench (рис. 3):

3. Проектирование и синтезирование счетчика с коэффициентом пересчета на D -тригерах

| № варианта |

Ксч |

Отбрасываемые комбинации |

| 15 |

15 |

15 |

Синтезируем пересчетную схему (табл. 5)

| Qt |

Qt+1 |

|

|

|

|

D1 |

D2 |

D3 |

D4 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

| 1 |

2 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

| 2 |

3 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

| 3 |

4 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

| 4 |

5 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

| 5 |

6 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

| 6 |

7 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

| 7 |

8 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

| 8 |

9 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

| 9 |

10 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

| 10 |

11 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

| 11 |

12 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

| 12 |

13 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

| 13 |

14 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

| 14 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

Составим карты Карно:

|

|

|

|||

|

|

|

|||

| D |

|

|||

|

|

1 |

1 |

1 |

|

| 1 |

1 |

1 |

1 |

|

|

|

|

|

||

![]()

|

|

|

||

|

|

1 |

1 |

|

| D |

1 |

1 |

|

|

|

1 |

||

| 1 |

1 |

|

|

|

|

|

|

|

![]()

|

|

|

||

|

|

1 |

1 |

|

| 1 |

1 |

|

|

|

|

1 |

1 |

1 |

|

|

|||

|

|

|

|

|

![]()

|

|

|

||

|

|

1 |

1 |

|

| 1 |

D |

1 |

|

|

|

1 |

||

| 1 |

1 |

|

|

|

|

|

|

|

![]()

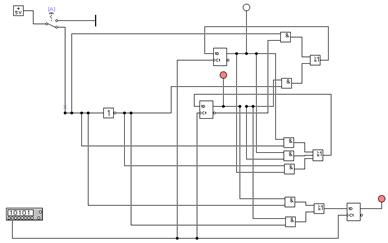

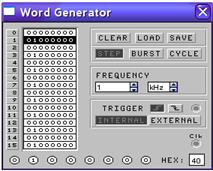

Построим схему в среде Electronics Workbench (рис. 4):

Рис. 4

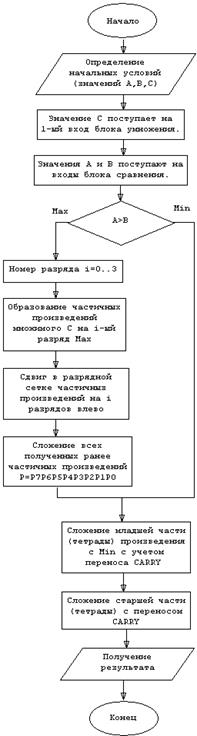

4. Синтезирование вычислительного устройства для реализации алгоритма вычислений на дискретных элементах (Если A > B, то Y = A * C + B иначе Y = A + B * C)

Согласно заданию, нам нужно спроектировать управляющий автомат, который будет реагировать на изменение входных параметров на входе, изменением результата на выходе, т.е. с обратной связью и является асинхронным. Управляющий автомат должен обладать большим быстродействием. Это достигается использованием матричных умножителей.

Структурная схема УА представлена на рисунке 5.

|

Рис.5

Структурная схема функционирования УА представлена на рисунке 6

|

Рис.6

Алгоритм работы :

Определение начальных условий (значений A,B,C)

Значение С поступает на 1-ый вход блока умножения.

Значения А и В поступают на входы блока сравнения.

Результатом работы блока сравнения являются значения MIN и MAX.

MAX поступает на второй вход блока умножения.

MIN поступает на первый вход блока суммирования.

Результат из блока умножения поступает на второй вход блока суммирования. Получение результата из блока суммирования, т.е. значения Y. Для сравнения чисел используется компаратор, который будет реализован на логических элементах.

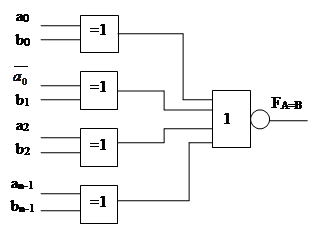

Компараторы

Компаратор – функциональный узел для определения отношения между двумя двоичными числами.

Основными отношениями являются “=” (FA = B ), “>” (FA > B ), остальные отношения получаются из основных:

![]() ,

, ![]() ,

, ![]()

равнение на равенство осуществляется путем поразрядного сравнения двух чисел.

| ai |

bi |

ri |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

1 |

ri – признак равенства bi разряда

Признак равенства одноразрядных чисел можно записать как

![]()

Многоразрядный компаратор на равенство состоит из элементов ИСКЛ. ИЛИ для поразрядного сравнения (рисунок 7).

|

A = an-1 an-2 … a1 a0

B = bn-1 bn-2 … b1 b0

Рис.7

Сравнение на “больше” “>” не является поразрядной операцией. Составим таблицу истинности для сравнения на “>” одноразрядных чисел:

| A |

B |

FA>B |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

![]()

Функцию для 2-х разрядных чисел определим так, если в старшем разряде А = 1 и В = 0, то FA

>

B

= 1 независимо от содержания младших разрядов; если старшие разряды одинаковы, то надо перейти к сравнению младших разрядов, рассуждая далее аналогично. Таким образом, для 2-х разрядных чисел: ![]() , где r1

– признак равенства старших разрядов a1

и b1

.

, где r1

– признак равенства старших разрядов a1

и b1

.

Распространяя рассуждения на многоразрядные числа, получим

![]()

В этом выражении ri – признаки равенства чисел в i-разрядах.

Микросхема компаратора обычно имеет дополнительные входы с теми же обозначениями, что и выходы A = B, A > B, A < B, которые используются для наращивания компаратора путем каскадного соединения схемы.

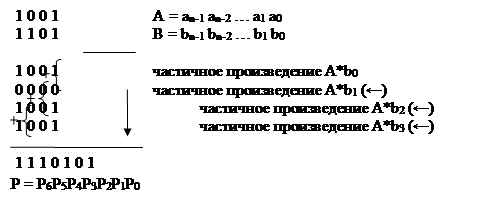

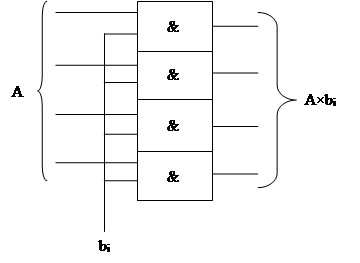

Умножение чисел

Процедура ручного умножения множимого A = an -1 an -2 … a1 a0 на множитель B = bn -1 bn -2 … b1 b0 заключатся в образовании частных произведений множимого A на разряды множителя B, при этом частичные произведения располагаются в разрядной сетке всякий раз со сдвигом на 1 разряд влево. Далее частичные произведения складываются для получения произведения P = P2 n -1 …P1 P0 . Результатом умножения множимого на разряд множителя bi равен 0 в случае bi = 0 или самому множимому A в случае, когда bi = 1, следовательно, для умножения A×bi можно использовать блок конъюнкторов (рисунок 8):

|

Рис.8

Наиболее высокое быстродействие достигается в матричных умножителях, в которых все частичные произведения образуются одновременно на разных блоках конъюнкторов, совмещены во времени, но разделены в пространстве, произведение сразу же образуется с помощью набора из (n-1) сумматоров (n – разрядность чисел), причем сдвиг в разрядной сетке частичных произведений выполняется монтажным способом. Составим блок-схему алгоритма работы УА.

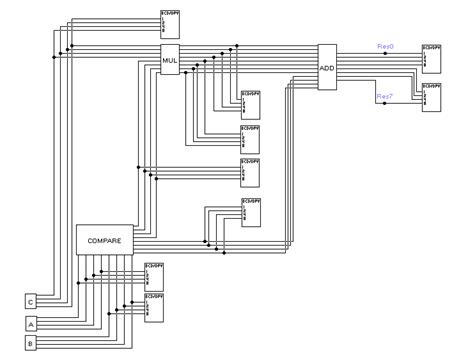

Схема работы вычислительного устройства (рисунок 9)

Рис.9

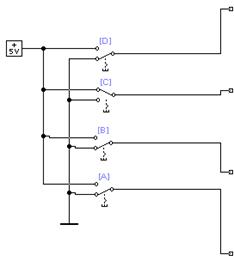

Данные А, В и С будут определяться с помощью блока переключателей, реализуемого следующей схемой (рисунок 10):

Рис.10

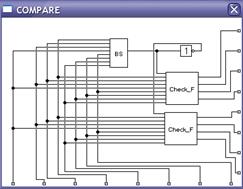

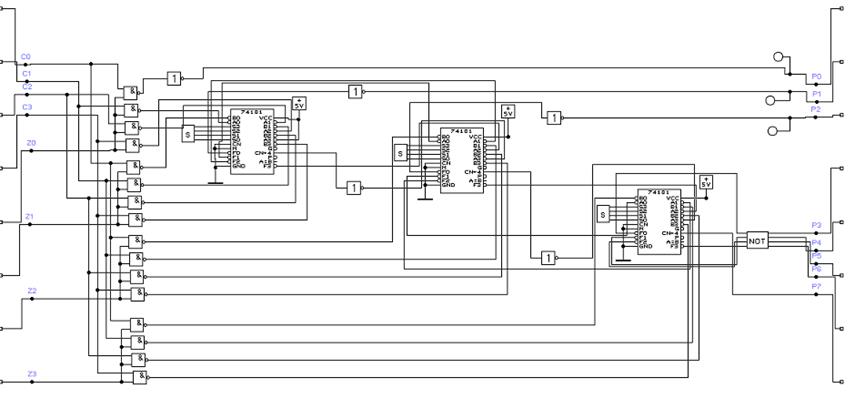

Анализ А и В происходит в Блоке сравнения (COMPARE) (рисунок 11):

Рис.11

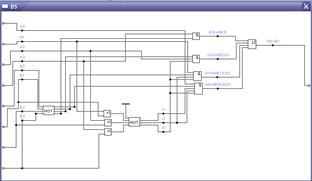

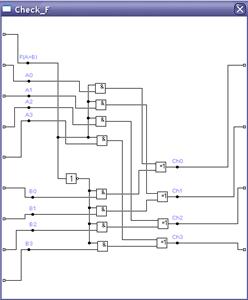

В соответствии с сигналом компаратора BS (рисунок 12) подается сигнал на блоки Check_F (рисунок 13)

Рис.12

Рис.13

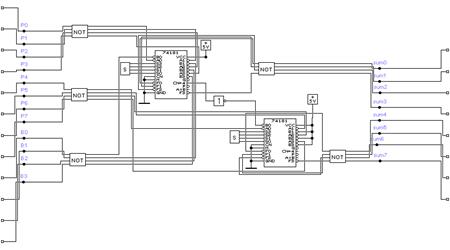

В результате Max подается в Блок умножения (MUL) (рисунок 14), а Min в Блок сложения (ADD) (рисунок 15)

Блок сложения (ADD):

Рис.15

Блок умножения (MUL):

Рис.14

Вывод

Достоинства данного метода очевидны, так как при его реализации выполняется критерий минимума аппаратных затрат и максимум быстродействия по сравнению с методом, в котором умножение двух чисел заменятся сложением.