| Скачать .docx |

Реферат: Центральный процессор персонального компьютера

Тема: Центральный процессор персонального компьютера

Содержание

1. ОБЩАЯ АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА.. 3

2.ПРИНЦИП РАБОТЫ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА.. 10

3.ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ЦЕНТРАЛЬНЫХ ПРОЦЕССОВ.. 18

3.1. Процессоры семейства AMDPhenomII18

3.2. Процессоры семейства IntelCorei7. 20

3.3. Сравнительная характеристика Corei7 920, PhenomIIX4 920, PhenomX4 9950. 23

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ.. 30

Сейчас, принято говорить, что центральный процессор является мозгом компьютера. Фактически, центральный процессор - это крошечный чип, связанный непосредственно с материнской платой, с большим вентилятором (кулером), подключенным непосредственно к нему. Без вентилятора центральный процессор очень быстро бы сгорел.

На сегодняшний день на рынке есть две главные марки центральных процессоров: Intel и AMD.

Различают также два различных центральных процессора: «гнездо» и разъем. «Гнездо» подсоединяется непосредственно к материнской плате, также оно имеет собственный вентилятор, в то время как разъем имеет оболочку, которая держится на центральном процессоре, и вентилятор, связанный с этой оболочкой. Нельзя выделить лучшее из этих двух типов, но «гнездо» становится все более популярным, и, таким образом, становится легче охлаждать процессор, что является главным фактором быстродействия компьютера.

Скорость центрального процессора измеряется в Мегагерцах (Мгц), свыше 1000 Мгц называется Гигагерцем (ГГц). Одно основное неправильное представление относительно центрального процессора – это то, что чем больше число (мегагерц/гигагерц), тем быстрее центральный процессор.

Целью данной курсовой работы является изучение архитектуры, функционирования и основных характеристик центрального процессора.

Для реализации поставленной цели, необходимо решить следующие задачи:

1. Изучить архитектуру центрального процессора

2. Исследовать функционирование центрального процессора

3. Провести сравнительный анализ основных характеристик процессоров.

1. ОБЩАЯ АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Центральный процессор- это центральное устройство компьютера, которое выполняет операции по обработке данных и управляет периферийными устройствами компьютера. У компьютеров четвёртого поколения и старше функции центрального процессора выполняет микропроцессор на основе СБИС, содержащей несколько миллионов элементов, конструктивно созданный на полупроводниковом кристалле путём применения сложной микроэлектронной технологии.

К основным характеристикам процессора относятся:

· Быстродействие (вычислительная мощность) – это среднее число операций процессора в секунду.

· Тактовая частота в МГц. Тактовая равна количеству тактов в секунду. Такт - это промежуток времени между началом подачи текущего импульса ГТЧ и началом подачи следующего. Характерные тактовые частоты микропроцессоров: 40 МГц, 66 МГц, 100 МГц, 130 МГц, 166 МГц, 200 МГц, 333 МГц, 400 МГц, 600 МГц, 800 МГц, 1000 МГц и т. д. До 3ГГц Тактовая частота отражает уровень промышленной технологии, по которой изготавливался данный процессор. Она также характеризирует и компьютер, поэтому по названию модели микропроцессора можно составить достаточно полное представление о том, к какому классу принадлежит компьютер. Поэтому часто компьютерам дают имена микропроцессоров, входящих в их состав. Ниже приведены названия наиболее массовых процессоров, выпущенных фирмой Intel и годы их создания: 8080 (1974 г.), 80286 (1982 г.), 80386DX (1985 г.), 80486DX (1989 г.), 80586 или Pentium (1993 г.), Pentium Pro (1995 г.), Pentium II (1997 г.), Pentium III (1999 г.), Pentium IV (2001 г.). Как видно, увеличение частоты – одна из основных тенденций развития микропроцессоров. На рынке массовых компьютеров лидирующее место среди производителей процессоров занимают 2 фирмы: Intel и AMD. За ними закрепилось базовое название, переходящее от модели к модели. У Intel – это Pentium и модель с урезанной кэш-памятью Pentium Celeron; у AMD – это Athlon и модель с урезанной кэш-памятью Duron.

· Разрядность процессора - это максимальное количество бит информации, которые могут обрабатываться и передаваться процессором одновременно. Разрядность процессора определяется разрядностью регистров, в которые помещаются обрабатываемые данные. Например, если регистр имеет разрядность 2 байта, то разрядность процессора равна 16 (2x8); если 4 байта, то 32; если 8 байтов, то 64.

Существует много различных подходов к реализации структурной схемы (архитектуры) центрального процессора (ЦП). В нашей стране наибольшее распространение получила архитектура, предложенная американской фирмой Intel. Именно поэтому мы сосредоточим основное внимание на изучении процессоров, построенных по идеологии Intel и вычислительных машин, реализованных на базе этих процессоров фирмой IBM.

При разработке Intel8086 применены интересные архитектурные решения, к которым, в частности, относится разделение функций сопряжения с шиной и выполнения команд. В соответствии с этим структуру процессора (рис. 1.1, а)можно условно разделить на две части: блок сопряжения с шиной (БСШ) и исполнительный блок (ИБ).

Рассмотрим назначение и работу отдельных узлов микропроцессора Intel 8086. В нем имеется четырнадцать 16-разрядных регистров, которые по своему назначению можно разделить на три группы (рис. 1.1, б). Регистры АХ, ВХ, СХ, DX образуют группу регистров общего назначения (РОН). Эти регистры могут без ограничений участвовать в выполнении арифметических и логических операций. Некоторые другие операции, например операции над цепочками байтов и слов, предписывают регистрам данной группы специальное использование: АХ - аккумулятор, ВХ - база, СХ - счетчик, DX - данные. В отличие от регистров других групп РОН обладают свойством раздельной адресации старших и младших байтов. Поэтому РОН можно рассматривать как совокупность двух наборов 8-разрядных регистров: набора Н, содержащего АН, ВН, СН, DH, и набора L, содержащего AL, BL, CL, DL. Регистры всех других групп являются неделимыми и оперируют 16-разрядными словами, даже в случае использования только старшего или младшего байта.

Рис. 1.1. Архитектура центрального процессора Intel 8086 и его регистры.

Регистры SP, BP, SI и DI образуют группу указательных и индексных регистров, назначение которых заключается в том, что они содержат значения смещений, используемых для адресации в пределах текущего сегмента памяти. При этом регистры-указатели SP и ВР хранят смещения адреса в пределах текущего сегмента памяти, выделенного под стек, а индексные регистры SI и DI содержат смещения адреса в пределах текущего сегмента памяти, выделенного под данные. С этим связаны и обозначения регистров: SP - указатель стека, ВР - указатель базы, SI - индекс источника и DI - индекс места назначения. Регистры этой группы могут использоваться и как регистры общего назначения.

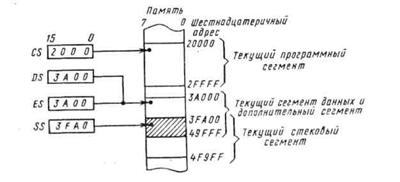

Регистры CS, DS, SS и ES, образующие группу сегментных регистров, играют важную роль во всех действиях ЦП, связанных с адресацией памяти. Обозначения регистров расшифровываются следующим образом: CS - кодовый или программный сегмент, DS - сегмент данных, SS - стековый сегмент и ES - дополнительный сегмент. Содержимое любого из этих регистров определяет текущий начальный адрес сегмента памяти, выделенного пользователем под информацию, соответствующую названию регистра.

Содержимое регистра CS определяет начальный адрес сегмента памяти, в котором располагается объектный код программы. Выборка очередной команды осуществляется относительно содержимого CS с использованием значения указателя команд IP. Содержимое регистра DS определяет начальный адрес текущего сегмента данных, так что обращение к данным в памяти ЦП осуществляет относительно содержимого DS. Для обращения к другим трем сегментам: дополнительному, стековому или программному - используется специальный указатель, который называется префиксом замены сегмента и располагается в соответствующих командах.

Содержимое регистра SS определяет текущий сегмент, выделенный для организации стека. Все обращения к памяти, при которых для вычисления адреса прямо или косвенно используются регистры ВР или SP, осуществляются относительно содержимого регистра SS. К таким обращениям относятся, например, все операции со стеком, включая и те, которые связаны с операциями вызова подпрограмм, прерываниями и операциями возврата. Обращения к данным, использующие регистр ВР (но не SP), могут производиться также и относительно одного из трех других сегментных регистров путем использования префикса замены сегмента.

Рис. 1.2. Регистр флагов

Содержимое регистра ES определяет начальный адрес сегмента, рассматриваемого как дополнительный сегмент данных. В частности, обращения к данным в операциях с цепочками байтов или слов осуществляются относительно ES, а в качестве смещения берется содержимое DI.

Кроме перечисленных регистров имеются два 16-разрядных регистра: IP - указатель команд и F - регистр флагов. В регистре IP формируется относительный (относительно CS)адрес команды, подлежащей исполнению. В регистре F (рис. 1.2) используются следующие девять разрядов: CF - перенос, PF - четность, AF - вспомогательный перенос, ZF - нулевой результат, SF - знак, TF - пошаговый режим, IF - разрешение прерывания, DF - направление, OF - переполнение. Неиспользованные разряды на рисунке заштрихованы.

Флаги AF, CF, PF, SF и ZF характеризуют признаки результата последней арифметической, логической или иной операции, влияющей на эти флаги. Установка флага производится в следующих случаях:

AF - при выполнении операции производится перенос «1» из младшей тетрады байта в старшую или осуществляется заем «1» из старшей тетрады;

CF - при переносе «1» из старшего бита байта (слова) или при заеме единицы в старший бит;

PF - если в представлении результата операции содержится четное число единиц;

SF - при получении «1» в старшем бите результата;

ZF - если в результате выполнения операции получено нулевое значение.

К этой группе флагов относится также флаг OF, который устанавливается при наличии переполнения в результате выполнения арифметических операций над числами со знаком.

Флаги DF, IF и TF используются для управления работой процессора. Флаг DF управляет направлением обработки данных в операциях с цепочками байтов или слов. При DF=1 цепочка обрабатывается снизу вверх, т. е. происходит автоматическое уменьшение (автодекремент) адреса текущего элемента цепочки. При DF=0 цепочка обрабатывается сверху вниз, т. е. происходит автоматическое увеличение (автоинкремент) адреса.

Флаг IF предназначается для разрешения или запрещения (маскирования) внешних прерываний. При IF = 0 внешние прерывания запрещены, т. е. процессор не реагирует на их запросы.

Флаг TF применяется для задания процессору пошагового режима, при котором процессор после выполнения каждой команды останавливается и ждет внешнего запуска. Пошаговый режим задается установкой флага TF= 1 и обычно необходим при отладке программ.

Основные операции по обработке данных выполняются в арифметико-логическом устройстве (АЛУ), с которым связана схема коррекции результатов (СКР), используемая при работе с данными, представленными в двоично-десятичных кодах. Связь внутренних узлов ЦП с шиной ША/Д осуществляется через буфер шины БШ, состоящий из двунаправленных усилителей с тремя устойчивыми выходными состояниями.

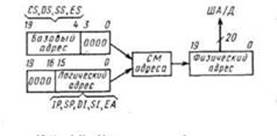

Усовершенствование архитектуры Intel 8086 связано также с введением в структуру микропроцессора специального сумматора (СМ) для вычисления адресов памяти.

Как отмечалось выше, разрядность адресов микропроцессора равна 20. Однако для упрощения операций хранения и пересылки адресной информации процессор манипулирует 16-разрядными логическими адресами, к которым относятся начальные (базовые) адреса сегментов памяти и значения смещений в этих сегментах. Логические адреса используются для вычисления 20-разрядных физических (абсолютных) адресов с помощью следующей процедуры. Содержимое каждого сегментного регистра рассматривается как 16 старших разрядов А19-А4 начального адреса соответствующего сегмента. Младшие разряды A3-А0 этого адреса всегда полагаются равными нулю и поэтому не запоминаются в регистрах, а приписываются справа к старшим разрядам во время операции вычисления физических адресов. Эта операция выполняется сумматором адреса, расположенным в блоке БСШ, и состоит в сложении 20-разрядного начального адреса сегмента с 16-разрядным смещением, которое дополняется четырьмя старшими разрядами А19-А16, равными нулю, как показано на рис. 1.3. Сумматор адресов осуществляет, например, следующие вычисления: CS + IP - при выборке очередной команды, SS + SP - при обращении к стеку, DS + SI и ES + DI - при обработке строк, DS + EA- при обращении к запоминающему устройству с произвольной выборкой (ЕА - исполнительный адрес, формирование которого описано ниже).

Рис. 1.3. Вычисление физического 20-разрядного адреса

Поскольку младшие четыре разряда начального адреса любого сегмента должны быть равны нулю, значения начальных адресов сегментов выбираются кратными 16. Наибольшая емкость памяти, отводимой под один сегмент, определяется максимальным значением 16-разрядного смещения и составляет 64К байт.

На рис. 1.4 приведен пример размещения сегментов памяти.

Рис 1.4. Пример размещения сегментов в памяти

В несложных системах с емкостью памяти не более 64К байт можно отказаться от сегментации памяти и установить все сегментные регистры в нулевое состояние. При этом 16-разрядный адрес смещения будет фактически абсолютным адресом. При использовании системы с большой емкостью памяти (до 1М байт включительно) начальные адреса сегментов задаются исходя из особенностей структуры программного обеспечения и данных, хранимых в памяти.

2.ПРИНЦИП РАБОТЫ ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Рабочий цикл центрального процессора:

01. На буферный регистр адреса центрального процессора посылается содержимое счётчика адреса команд.

02. На буферный регистр адреса запоминающего устройства посылается содержимое буферного регистра адреса центрального процессора.

03. Из запоминающего устройства по адресу счётчика адреса команд происходит выборка адреса команды и передача на буферный регистр адреса запоминающего устройства.

04. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

05. На регистр команд посылается команда с буферного регистра данных центрального процессора.

06. На буферный регистр адреса центрального процессора посылается первый адрес операнда команды.

07. На буферный регистр адреса запоминающего устройства посылается содержимое На буферный регистр адреса центрального процессора.

08. Из запоминающего устройства происход выборка данных по адресу первого операнда команды и передача его на буферный регистр адреса запоминающего устройства.

09. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

10. На аккумулятор передаётся содержимое буферного регистра данных центрального процессора.

11. На буферный регистр адреса центрального процессора посылается содержимое посылается второй адрес операнда команды.

12. На буферный регистр адреса запоминающего устройства посылается содержимое буферного регистра адреса центрального процессора.

13. Из запоминающего устройства происходит выборка данных по адресу второго операнда команды и передача его на буферный регистр адреса запоминающего устройства.

14. На буферный регистр данных центрального процессора подаётся содержимое буфера регистра данных запоминающего устройства.

15. На арифметико-логическое устройство посылается содержимое буферного регистра данных центрального процессора.

16. Расшифровка кода операций и подача кода на схему выработки.

17. Выполнение операций в арифметико-логическом устройстве.

18. Результат арифметическо-логического устройства записывается в запоминающие устройство по второму адресу.

19. В запоминающие устройство по адресу второго операнда команды записывается содержимое буферного регистра данных запоминающего устройства.

20. На буферный регистр данных запоминающего устройства посылается содержимое буферного регистра данных центрального процессора.

21. На буферный регистр данных центрального процессора посылается содержимое арифметико-логического устройства.

22. Изменить счётчик адреса команд.

23. Возврат на первый шаг если не возникла команда "Конец работы".

Система команд процессора Intel 8086 насчитывает более 10 разнообразных форматов команд, отличающихся как длиной формата (машинная команда может занимать от 1 до 6 байт, не считая возможных предшествующих ей префиксов), так и распределением полей в отдельных байтах команды.

Используются 3 вида префиксов (префиксных байтов), которые предшествуют команде и определенным образом влияют на ее выполнение.

К префиксам относятся:

1) seg – префикс замены сегмента;

2) rep – префикс повторения;

3) lock – префикс блокировки шины.

1) Префикс замены сегмента используется для переназначения стандартных сегментов, используемых по умолчанию при обращении к памяти за операндом и (или) при записи результата.

Адрес переназначения сегмента занимает 2 средних бита в префиксном байте

2) Префикс повторения используется исключительно перед командами обработки строк и заставляет повторять ее выполнение многократно в целях поэлементной обработки всей строки.

Использование префикса rep позволяет организовывать цикл по последовательной обработке элементов строки на аппаратном, а не на программном уровне.

3) При выполнении команды с предшествующим ей префиксом lock на все время выполнения команды блокируется шина, связывающая процессор с памятью и портами ввода-вывода.

Действие любого префикса распространяется только на одну машинную команду, которая следует непосредственно за ним.

Форматы команд

1. Однобайтная безадресная команда:

![]()

ОрС

7 0

Рис. 2.1. Однобайтная одноадресная команда

Подобный формат используется либо командами с неявной адресацией, либо командами, не использующими операндов.

Примерами команд первого типа могут служить команды обработки строк, в которых строка–источник и строка-приемник неявно адресуются с использованием регистров SI и DI соответственно.

К ним относятся:

MOVS – пересылка строки,

LODS – загрузка строки,

STOS – запись в память строки,

CMPS – сравнение строк,

SCAS – сканирование строки.

2. Однобайтная одноадресная команда

![]()

![]()

![]()

ОрС W REG

7 4 3 2 0

Рис.2.2 . Однобайтная одноадресная команда

Эта команда задает прямой адрес регистрового операнда (поле reg). Бит w задает длину операнда (1 – слово, 0 – байт).

|

3. Двухадресная команда с постбайтом адресации

Рис.2.3. Двухадресная команда с постбайтом адресации

Бит d кода операции (direction - направление) определяет, по какому адресу записывается результат операции (при d = 1 – в регистр reg, при d = 0 – в регистр или память, адресуемые полем r/m).

Подобный формат широко используется для разнообразных арифметических и логических команд.

|

4. Одноадресная команда с постбайтом адресации

Рис.2.4. Одноадресная команда с постбайтом адресации

В отличие от предыдущего формата, среднее поле постбайта адресации является расширением кода операции (Е – Extended).

Подобный формат используется, во-первых, для однооперандных команд (например, INC, DEC, NEG – negative – изменение знака, NOT – инвертирование) и, во-вторых, для двухоперандных команд, в которых один из операндов адресуется неявно (например, MUL/IMUL – умножение, DIV/IDIV – деление, в которых один из операндов является аккумуляторным, а также команды сдвигов, в которых счетчик числа сдвигов адресуется неявно регистром CL).

На рис. 2.2 приведена схема работы центрального процессора.

Где:

ВШУ, ВШД - внутренняя схема управления, данных;

РОН - регистр общего назначения;

АЛУ - арифметико-логическое устройство;

А - аккумулятор;

БВПК - блок восстановления последовательности команд;

сх1...схN (N=2n ) - схемы выработки управляющего сигнала (не регистр);

ДшОп - Дешифратор операций;

УВПК - устройство восстановления последовательности команд;

А1 , А2 - операнды;

Рез - Результат операции;

Вып - флажок выполнено/не выполнено;

РгКв - регистр команд (выход);

КОп - Код операции;

УУ - устройство управления;

РгК - регистр команд;

КОп - Код операции;

БРК - блок распределения команд;

УРК - устройство распределения команд;

СчАК - счетчик адреса команд (+δ - прибавляет по байту);

БРА, БРД - буферные регистры адреса, данных;

ЗУ - запоминающее устройство;

БРАЗУ , БРДЗУ - буферные регистры адреса, данных запоминающего устройства;

Согласно данной схеме Рабочий цикл Центрального процессора имеет следующий вид

Шаги 1-5: MOV(СчАК,РгКi );

Шаги 6-10: MOV(А1 ,РгК[А1 ]i );

Шаги 11-15: MOV(А2 ,РгК[А2 ]i );

Шаг 16: PARBEGIN

16.1: УРК(РгКi ,РгКАЛУi );

16.2: ДшОп(РгКi -1 );

16.3: выполнение Опi -2 ;

16.4: УВПК(РгКвi -3 );

PAREND;

Шаги 17-22: MOV(РгКв[Рез]i -4 ,[А2 ]);

Шаг 23: СчАК + δ;

Шаг 24: → Шаг 1.

Где:

Оп - операция;

MOV - "проход", введено для сокращения, каждый MOV означает 5 соответствующих шагов:

1. БРА := А1 ;

2. БРАЗУ := БРА;

3. БРДЗУ := [БРАЗУ ];

4. БРД := БРДЗУ ;

5. [А2 ] := БРД.

- то, что стоит в кв. скобках [] означает, что берется не А2 , а значение по адресу А2 ;

- индексы i-1, i-2, i-3 и т.д. означают, что берется предыдущая команда; предпредыдущая и т.п. (которая уже прошла обработку на предыдущем блоке);

-шаги алгоритма 16.1, 16.2, 16.3 и 16.4 выполняются ПАРАЛЛЕЛЬНО

3.ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ЦЕНТРАЛЬНЫХ ПРОЦЕССОВ

3.1. Процессоры семейства AMDPhenomII

Главное отличие новых процессоров семейства AMDPhenomII от процессоров семейства AMDPhenom заключается в том, что они выполнены по 45-нм техпроцессу с применением технологии S0I, в то время как процессоры семейства AMDPhenom выполняются по 65-нм техпроцессу.

Точно так же, как и процессоры семейства AMDPhenom, они представляют собой истинно многоядерные процессоры, то есть все ядра процессора выполнены на одном кристалле.

Среди нововведений, реализованных в новых процессорах AMDPhenomII, можно также отметить усовершенствованную технологию AMDCool'&'Quiet 3.0. Она объединяет в себе ряд функций, позволяющих снизить энергопотребление процессора в те моменты, когда он недозагружен, а также предотвратить перегрев процессора.

При анонсе нового процессора семейства AMDPhenomIIХ4 компания AMD указывала и на другие преимущества в сравнении с предыдущим семейством. В частности, отмечалось, что новые процессоры выполняют больше инструкций за такт (InstructionPerClock, IPC).

Семейство процессоров AMDPhenomII в настоящее время включает три серии: AMDPhenomII Х4 900, AMDPhenomII Х4 800 и AMDPhenomII ХЗ 700.

Процессоры серии AMDPhenomII Х4 900

Сейчас в 900-ю серию процессоров входят две четырехъядерные модели: AMDPhenomII Х4 940 и AMDPhenomIIХ4 920. Каждое ядро процессора AMDPhenomIIХ4 900-й серии имеет выделенный L-2-кэш размером 512 Кбайт и разделяемый между всеми ядрами L3-кэш размером 6 Мбайт.

Процессор AMDPhenomII Х4 940 имеет тактовую частоту 3,0 ГГц, а процессор AMDPhenomII Х4 920 — 2,8 ГГц. Эти процессоры оснащены интегрированным двухканальным контроллером памяти DDR2 и поддерживают память DDR2 667/800/1066.

Процессоры AMDPhenomII Х4 940 и AMDPhenomIIХ4 920 совместимы с разъемами SockeАМ2+/АМ2 и поддерживают шину HyperTransport 3.0 на скорости до 3600 МГц (двусторонняя) пропускной способностью до 16 Гбайт/с. Оба процессора имеют TDP 125 Вт.

Разница между моделями процессоров AMDPhenomIIХ4 940 и AMDPhenomIIХ4 920 заключается не только в тактовой частоте, но еще и том, что процессор AMDPhenomII Х4 940 имеет разблокированный множитель, что позволяет реализовывать его эффективный разгон. Вообще, если говорить о разгонном потенциал процессора AMDPhenomII Х4 940, то, по сообщениям независимых источников в Интернете, он достаточно большой. Так, есть данные что применение жидкого азота для охлаждения процессора позволило достичь рекордной тактовой частоты в 6 ГГц, а посредством обычного воздушного охлаждения этот процессор легко разгоняется до 4 ГГц.

Добавим также, что в скором времени ожидается появление процессора AMDPhenomIIХ4 910 которым будет иметь тактовую частоту 2,6 ГГц.

Процессоры серии AMDPhenomII Х4 800

На данный момент 800-я серия процессоров включает всего одну модель четырехъядерного процессора —AMDPhenomII Х4 810. Однако в скором времени ожидается появление еще одной модели AMDPhenomIIХ4 805.

Отличие процессоров 800-й серии от процессоров 900-й серии заключается в урезанном размере кэша L3 и в том, что в процессорах 800-й серии реализован контроллер памяти, поддерживающий память как DDR2, так и DDR3. Кроме того, процессоры 800-й серии совместимы как с разъемам SocketAM2+/AM2 так и с разъемом SocketAM3.

Каждое ядро процессора AMDPhenomIIX4 810 имеет выделенный L2-кэш размером 512 Кбайт и разделяемый между всеми ядрами L3-кэш размером 4 Мбайт. Процессор AMDPhenomII Х4 810 работает с тактовой частотой 2,6 ГГц. Он оснащен интегрированным двухканальным контроллером памяти DDR2 (поддерживается память DDR2-667/800/1066) и контроллером памяти DDR3 (поддерживается память DDR3-800/1066/1333). TDP процессора составляет 95 Вт.

Процессоры серии AMDPhenomII ХЗ 700

В настоящее время в 700-ю серию процессоров входят две модели: AMDPhenomII ХЗ 720 и AMDPhenomII ХЗ 710. Все процессоры 700-й серии являются трехъядерными. Каждое ядро процессора AMDPhenomII Х3 720 и AMDPhenomII ХЗ 710 имеет выделенный L2-кэш размером 512 Кбайт, а разделяемый между всеми ядрами L3-кэш имеет размер 6 Мбайт.

Как и процессоры 800-й серии, процессоры 700-й серии имеют интегрированный двухканальный контроллер памяти DDR2 (поддерживается память DDR2-667/800/1066) и контроллер памяти DDR3 (поддерживается память DDR3-800/1066/1333).

Процессор AMDPhenomII ХЗ 720 работает на тактовой частоте 2,8 ГГц, а процессор AMDPhenomII ХЗ 710 — на тактовой частоте 2,6 ГГц. Еще одно различие между AMDPhenomII ХЗ 720 и AMDPhenomII ХЗ 710 заключается в том, что в модели AMDPhenomII ХЗ 720 разблокирован множитель, а следовательно, его можно легко разгонять.

3.2. Процессоры семейства IntelCorei7

Рис.3.1. процессор Corei7-965

Процессоры семейства Nehalem, как и полагается первопроходцам новой платформы, будут представлены на рынке высокоуровневыми четырехъядерными решениями на базе ядра Bloomfield, а уже через год пополнятся доступными моделями, которые займут место прежних Core 2 Duo.

Процессор Nehalem

Новые процессоры, получившие название Core i7, изготовляются по технологическим нормам 45 нм с применением high-k диэлектрика и металлического затвора транзисторов, но в отличие от своих предшественников все четыре ядра расположены на одном кристалле. Если помните, Core 2 Quad состоит из двух ядер Core 2 Duo, объединенных в одном корпусе. Кроме того, процессоры Nehalem содержат кэш-память третьего уровня объемом 8 МБ, встроенный трехканальный контроллер памяти DDR3 и контроллер шины Quick Path Interconnect (QPI), которые потребовали значительное увеличение контактов – до 1366, из-за чего размеры CPU нового поколения стали больше и по форме он уже напоминает прямоугольник, а не квадрат как у Core 2. Естественно, ни о какой совместимости разъемов речи не идет.

Кстати, в название Core i7 отражено поколение процессоров, использующих архитектуру P6. Всего на данный момент доступно три модели новых CPU: Core i7-965 Extreme Edition, Core i7-940 и Core i7-920. Главное отличие между ними заключается в рабочей частоте ядер и шины QPI, которая пришла на смену "старушке" FSB, аналогично технологии HyperTransport от AMD. Естественно, экстремальная версия ориентирована на энтузиастов и оверклокеров, имеет более высокую частоту и разблокированный на повышение множитель. Также для Core i7-965 Extreme Edition характерно большее количество множителей для памяти, частота которой формируется путем их умножения на частоту тактового генератора (опорной частоты шины QPI или QPI bclk), равную в номинале 133 МГц. Частоты ядер, шины QPI и кэша L3 также формируются путем умножения определенных коэффициентов на опорную частоту. Если же разгонять процессор методом поднятия QPI bclk, то частоты всех блоков и памяти поднимутся в зависимости от их множителей. Обычные Intel Core i7 будут уже не столь дружелюбны к оверклокерам, но, возможно, со временем данную проблему все-таки решат.

Еще одним новшеством семейства Nehalem стало использование технологии Hyper-Threading (или Simultaneous Multithreading – SMT, технология "одновременной мультипоточности"), от которой отказались при переходе на архитектуру Core. Теперь же каждый процессор Core i7 определяется как восемь логических ядер, что может существенно повысить быстродействие оптимизированных под многопоточность приложений.

Несмотря на перенос части северного моста в CPU, уровень TDP не превышает 130 Вт, что даже ниже чем у 45-нм Intel Core 2 Extreme QX9770 на недавно вышедшем степпинге C0. Связано это как с монолитностью кристалла, так и с меньшим объемом кэша – у QX9770 он составляет 12 МБ, тогда как Core i7 довольствуется кэш-памятью общим объемом в 9 МБ. Но даже с таким уровнем TDP, системы охлаждения для новых процессоров немного выросли в размерах, а монтажные отверстия в материнских платах не совпадают с креплениями от кулеров под Socket LGA775. Учитывая, что сейчас процессоры в большинстве случаев поставляются в коробочном исполнении, то вряд ли стоит переживать на этот счет. Для разгона, конечно, придется подыскать кулер поэффективнее или крепление для старой, но мощной системы охлаждения.

Все основные характеристики процессоров Core i7 занесены в табл. 3.1, представленную ниже.

Таблица 3.1

Характеристики процессоров Core i7

| Модель | Intel Core i7-965 Extreme Edition | Intel Core i7-940 | Intel Core i7-920 |

| Разъём | LGA1366 | LGA1366 | LGA1366 |

| Техпроцесс | 45-нм, с применением high-k диэлектриков | 45-нм, с применением high-k диэлектриков | 45-нм, с применением high-k диэлектриков |

| Число ядер | 4 (8 потоков) | 4 (8 потоков) | 4 (8 потоков) |

| Частота | 3,20 ГГц | 2,93 ГГц | 2,66 ГГц |

| L1 кэш | 4 x 32+32 КБ | 4 x 32+32 КБ | 4 x 32+32 КБ |

| L2 кэш | 4 x 256 КБ | 4 x 256 КБ | 4 x 256 КБ |

| L3 кэш | 8 МБ | 8 МБ | 8 МБ |

| Напряжение | 1,20 В | 1,20 В | 1,20 В |

| TDP | 130 Вт | 130 Вт | 130 Вт |

3.3. Сравнительная характеристика Corei7 920, PhenomIIX4 920, PhenomX4 9950

Сравнительная характеристика процессоров Corei7 920, PhenomIIX4 920, PhenomX4 9950 представлена в табл. 3.2.

Таблица .3.2.

Характеристики процессоров Corei7 920, PhenomIIX4 920, PhenomX4 9950

| Corei7 920 | PhenomIIX4 920 | PhenomX4 9950 | |

| Ядро | Bloomfield | Deneb | Agena |

| Микроархитектура | Nehalem | Stars | Stars |

| Техпроцесс, нм | 45 | 45 | 65 |

| Кол-во транзисторов, млн. шт. | 731 | 758 | 450 |

| Площадь кристалла, кв. мм. | 263 | 258 | 285 |

| Тактовая частота, МГц | 2660 | 2800 | 2600 |

| Кэш L1, Кбайт | 4 x 32+32 | 4 x 64+64 | 4 x 64+64 |

| Кэш L2, Кбайт | 4 x 256 | 4 x 512 | 4 x 512 |

| Кэш L3, Мбайт | 8 | 6 | 2 |

| Тепловыделение, Вт | 130 | 125 | 125 |

| Цена, $ | 302 | 249 | 200 |

Не секрет, что желающие заиметь в составе домашнего ПК Core i7 вместе с процессором вынуждены в довесок обновлять материнскую плату и память. Совершенно не факт, что приживутся старые модули: камни под LGA1366 не выносят высоких напряжений на оперативке. Даже после падения цен, покупка такой системы влетает в копеечку. Материнские платы дешевле двухсот долларов найти сложно, а цены на младший Core i7 начинаются от 274$ (не забываем про выросший курс). Правда, цены на память значительно снизились – раньше двухгигабайтный комплект стоил почти 200$, сейчас эта цифра упала почти до 50$. Итого мы получаем около 580$ за базовый комплект на iCore7 (и это если не потребуется менять, например, блок питания или корпус).

AMD предлагает платформу ценой 230$ (Phenom II X4 920) + 100$ (Gigabyte GA-MA790X-DS4) + 80$ (2 x 1024 Мбайт DDR2-1066) = 410$. Действительно, значительный отрыв (40%) сохраняется даже в пересчете на сегодняшние цены, а 170$ - немаленькая сумма для среднестатистического столичного жителя, не говоря уже о регионах. С точки зрения финансовой выгоды для потребителя AMD обыгрывает своего конкурента. Сравнивать производительность новинки мы будем с младшим представителем Core i7, 920-й моделью, Phenom X4 9950 и PhenomIIX4 920.

В таблице 3.3. приведена характеристика компьютера, на котором проводится тестирование

Таблица 3.3

Характеристика компьютера, на котором производится тестирование

| Core i7 920 | Phenom II X4 920 / Phenom X4 9950 | |

| Материнская плата | MSI X58 Platinum | MSI DKA790GX Platinum |

| Видеокарта | BFG GTX 295 | BFG GTX 295 |

| Оперативная память | Kingson HyperX DDR3-1333 | Corsair Dominator DDR2-1066 |

| Блок питания | BFG 800 Вт | BFG 800 Вт |

| Жесткий диск | WD Raptor 150 Гбайт | WD Raptor 150 Гбайт |

| Операционная система | Windows Vista SP1 | Windows Vista SP1 |

Подбирая тестовые приложения, мы старались охватить все области: игры, работу в двумерных и трехмерных редакторах, кодирование видео, архивацию данных.

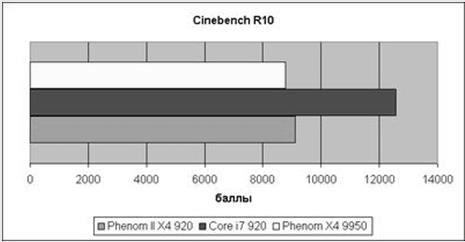

Рис.3.2 Результаты Cinebench R10

Cinebench R10 отдает свой голос за Core i7 – спасибо улучшенному Hyper-threading и оптимизации под многопоточные приложения. Обновленный Phenom обходитпредшественника из-за более высокой тактовой частоты; изменения в ядре и возросший кэш не помогают совершенно.

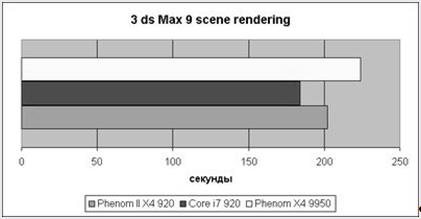

Рис.3.3. Результаты 3ds Max 9

В 3ds Max 9 отставание Deneb от Nehalem уже не столь велико, менее десяти процентов. А вот недостатки Agena проявляются сильнее – десятипроцентный прирост меньше объявленного AMD в пресс-релизе (25%), но уже что-то.

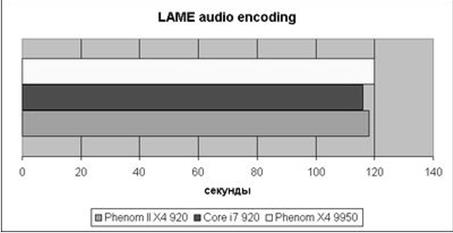

Рис.3.4 Результаты LAME encoding

Перекодирование аудио – однопоточная задача, так что разница между всеми тремя участниками теста невелика.

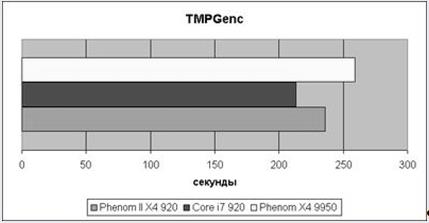

Рис.3.5.Результаты TMPGenc encoding

С конвертированием видео ситуация лучше, около 10% отрыва между соревнующимися. Расстановка сил не претерпела изменений – лидирует Core i7, за ним Phenom II X4, и в хвосте "старичок" 9950.

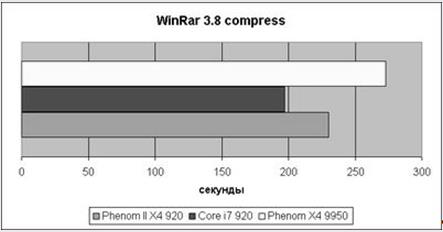

Рис.3.6. Результаты WinRar 3.80

WinRar 3.80 никаких сюрпризов не подносит – та же картина с незначительными изменениями.

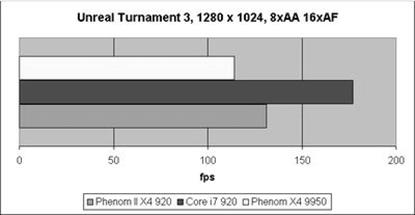

Рис. 3.7. Результаты UT3

Unreal Tournament 3 отдал предпочтение продукции Intel, видимо, за счет разницы в архитектуре.

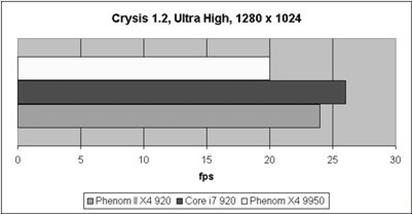

Рис.3.8. Результаты Crysis 1.2

В Crysis отставание Phenom X4 от новичка обусловлено ростом тактовой частоты; Core i7, как всегда, на первом месте.

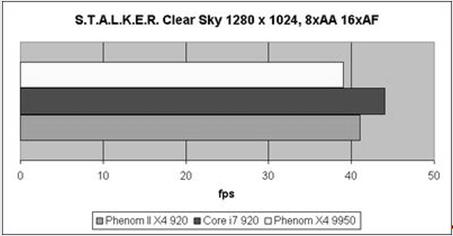

Рис.3.9 Результаты S.T.A.L.K.E.R. Clear Sky

S.T.A.L.K.E.R. Clear Sky не выбивается из общего порядка

Общий итог по тестам – Phenom II X4 шустрее первого на 10%, и примерно на столько же проигрывает младшему Core i7. Если же принять во внимание стоимость, то картина меняется: платформа Dragon обходит самую дешевую конфигурацию на Nehalem по соотношению цена/производительность.

Новый процессор AMDопределенно улучшил свои позиции, хоть он и не конкурент по скорости Core i7 (да и четырехядерники на Core 2 Quad по отдельным показателям лучше), но в сравнении с Phenom X4 сделан значительный шаг вперед. Прибавим к этому грамотное позиционирование продукта (в составе платформы), совместимость с уже вышедшими материнскими платами, и дешевизну. У Dragon определенно есть будущее.

Данная курсовая работа посвящена изучению архитектуры, функционированию центрального процессора персонального компьютера.

В первом разделе работы приведено определение центрального процессора, приведены основные характеристики. В работе приведена схема структуры Центрального процессора, описана работа основных регистров.

Второй раздел посвящен принципам работы Центрального процессора персонального компьютера. В разделе приведен общий рабочий цикл центрального процессора, который состоит из 23 шагов. Описаны форматы команд, которые могут быть: однобайтная одноадресная команда, двухадресная команда с постбайтом адресации и одноадресная команда с постбайтом адресации. Также приведена схема работы центрального процессора и алгоритм функционирования.

В третьем разделе приведены осноные характеристики процессоров семейства AMD и IntelCorei7. Проведен сравнительный анализ основных характеристик процессоров Corei7 920, PhenomIIX4 920, PhenomX4 9950.

При сравнении процессоров Intelcorei7 920, AMDPhenom II X4 920 и AMDPhenomX4 9950, то можно сделать вывод о том, что в целом AMD Phenom II X4 по производительности стоит вровень с процессорами Intel предыдущего поколения (Core 2 Quad) и весьма значительно отстает от Intel Core i7. Но в сравнении AMDPhenomX4 и AMDPhenom II X4 сделан значительный шаг вперёд. Говоря о цене; Intel, то он стоит почти в два раза больше, чем AMD.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

1. Акулов О. А., Медведьев Н. В. Информатика: базовый курс. М.: Омега-Л, 2006.

2. Богумирский В.С. Руководство пользователя ПК. В 2-х ч. - СПб: Ассоциация OILCO, 1992. – 88 c.

3. Дорот В. А., Новиков Ф. Н. Толковый словарь современной компьютерной лексики. 2-е изд. СПб.: BHV, 2001.

4. Информатика: Учебник. Под ред. Макаровой Н. В. М.: Финансы и статистика, 2000.

5. Лесничая И.Г. Информатика и информационные технологии. Учебное пособие. М.: Издательство Эксмо, 2007

6. Макарова Н.В., Николайчук Г.С., Титова Ю.Ф. Компьютерное делопроизводство. - СПб.: Издательский дом «Питер», 2002.

7. Под ред. Косарева В.П., Королева Ю.М. Экономическая информатика и вычислительная техника. - М.: Перспектива, 2000. - 99с.

8. Под ред. проф. Шуремова Е.Л., доц. Тимаковой Н.А., доц. Мамонтовой Е.А. Практикум по экономической информатике. - М.: Перспектива, 2000.

9. Попов В.Б. Основы компьютерных технологий. М. : Финансы и статистика, 2002.

10. Рассел Борланд. Running Word 6.0 для Windows (Русскаяредакция). -М.: ТОО Channel Trading Ltd., 2005. – 213 c.