| Скачать .docx |

Книга: Цифровые интегральные микросхемы Микроэлектроника -

ВВЕДЕНИЕ

Основные понятия и определения

В настоящее время цифровая электроника базируется на достижениях микроэлектроники, для которой характерно органическое единство физических, конструкторско-технических и схемотехнических аспектов. Микроэлектроника охватывает вопросы исследования, разработки и принципов применения интегральных микросхем.

Интегральная микросхема (ИС) – это совокупность электрически связанных компонентов (транзисторов, диодов, резисторов и др.), изготовленных в едином технологическом цикле на единой полупроводниковой основе (подложке).

Интегральная микросхема выполняет определенные функции обработки (преобразования) информации, заданной в виде электрических сигналов: напряжений или токов. Электрические сигналы могут представлять информацию в непрерывной (аналоговой), дискретной и цифровой форме.

Аналоговые и дискретные сигналы обрабатываются аналоговыми или линейными микросхемами, цифровые сигналы – цифровыми микросхемами. Существует целый класс устройств и соответственно микросхем называемых аналого-цифровыми или цифро-аналоговыми и, служащих для преобразования сигналов из одной формы в другую.

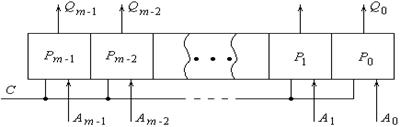

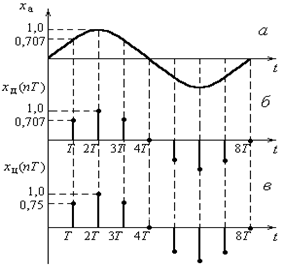

Аналоговый сигнал описывается непрерывной или кусочно-непрерывной функцией, причем и аргумент и сама функция могут принимать любые значения из некоторых интервалов. На рис. 1, а приведено графическое изображение гармонического сигнала

![]() в качестве примера аналогового сигнала,

в качестве примера аналогового сигнала,

где ![]() ,

, ![]() ,

,

Um

= 1, ![]() ,

, ![]() .

.

Рис. 1. Три формы представления сигналов

Дискретный сигнал

– это форма представления непрерывного сигнала в виде решетчатой функции ![]() (временного ряда) (рис. 1, б), которая может принимать любые значения на некотором интервале

(временного ряда) (рис. 1, б), которая может принимать любые значения на некотором интервале ![]() а независимая переменная n принимает лишь дискретные значения (n = 0,1), где T – интервал дискретизации.

а независимая переменная n принимает лишь дискретные значения (n = 0,1), где T – интервал дискретизации.

Как видно из приведенных диаграмм значения дискретного и аналогового сигналов в однозначных временных точках абсолютно совпадают.

Цифровой сигнал – квантованный временной ряд

![]() ,

,

графически представленный на рис. 1, в, принимающий лишь ряд дискретных значений – уровней квантования, а независимая переменная n принимает значения 0, 1, Нелинейная функция Qк – задает значения уровней квантования в двоичном коде. Число Kуровней квантования и число S разрядов соответствующих кодов связаны зависимостью

![]() .

.

Функциональная сложность интегральных схем

Компоненты, входящие в состав ИС, не могут быть выделены из нее в качестве самостоятельных изделий, кроме того, они характеризуются некоторыми особенностями по сравнению с дискретными транзисторами, диодами и т. д.

Особенностью цифровых ИС является высокая сложность выполняемых ими функций, поэтому количество компонентов в одной микросхеме может исчисляться сотнями тысяч и даже миллионами.

Функциональную сложность ИС обычно характеризуют степенью компонентной интеграции, т. е. количеством чаще всего транзисторов на кристалле. Количественно степень интеграции описывается условным коэффициентом K = lg N , где N – число компонентов.

В зависимости от значений K интегральные схемы подразделяются:

K£ 1…2, (N £ 100) – малая интегральная схема (МИС или IS);

2 £K£ 3…4, (N £ 10000) – интегральная схема средней степени интеграции (СИС или MSI);

3…4 £K < 5, (N < 105 ) – большая интегральная схема (БИС или LSI);

K³ 5, (N ³ 105 ) – сверхбольшая интегральная схема (СБИС или

VLSI).

Сокращенияприведенныенаанглийскомязыкеимеютследующийсмысл: IS – Integrated Circuit; MSI – Medium Scale Integration; LSI – Large Scale Integration; VLSI – Very Large Scale Integration.

Иногда сложность ИС характеризуют таким показателем, как плотность упаковки. Это количество компонентов, приходящихся на единицу площади кристалла. Этот показатель характеризует уровень технологии, и в настоящее время он составляет ~ 1000 компонентов/мм2 .

Особенности технологии и производства ИС

При изготовлении интегральных схем используется групповой метод производства и в основном планарная технология.

Групповой метод производства предполагает изготовление на одной полупроводниковой пластине большого количества однотипных ИС и одновременную обработку десятков таких пластин. После завершения цикла изготовления пластины разрезаются в двух взаимно перпендикулярных направлениях на отдельные кристаллы – чипы (chip), каждый из которых представляет собой ИС.

Планарная (плоскостная) технология – это такая организация технологического процесса, при которой все составляющие ИС формируются в одной плоскости.

Необходимо отметить, что создание и освоение изделий микроэлектроники является чрезвычайно дорогостоящим делом.

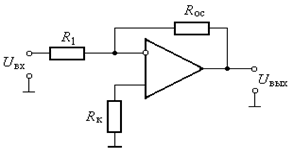

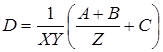

Стоимость D одной ИС (одного кристалла) упрощенно можно вычислить следующим образом:

,

,

где A – затраты на НИР и ОКР по созданию ИС; B – затраты на технологическое оборудование; С – текущие расходы на материалы, электроэнергию, заработную плату в пересчете на одну пластину; Z – количество пластин, изготавливаемых до амортизации основных производственных фондов; X – количество кристаллов на пластине; Y – отношение годных ИС к количеству, запущенных в производство.

Увеличение Y достигается совершенствованием технологии, а рост числа кристаллов X достигается увеличением размера пластины и уменьшением размеров элементов ИС.

Полупроводниковые интегральные схемы

Классификация ИС может производиться по различным признакам. Однако по способу производства современные микросхемы можно разделить на полупроводниковые, пленочные, гибридные. Основу современной цифровой электроники составляют полупроводниковые интегральные схемы.

Широкое распространение получили следующие полупроводниковые ИС:

· биполярные;

· МДП (МОП) – металл-диэлектрик (окисел)-полупроводник;

· БиМОП – сочетание двух первых типов.

Технология полупроводниковых ИС основана на легировании полупроводниковой (кремниевой) пластины поочередно донорными и акцепторными примесями, в результате чего под поверхностью образуются тонкие слои с разным типом проводимости и p–n-переходы на границах слоев. Отдельные слои используются в качестве резисторов, а p–n-переходы – в диодных и транзисторных структурах.

Легирование осуществляется локально с помощью специальных масок с отверстиями, через которые атомы примеси проникают в пластину на нужных участках. Роль маски обычно играет пленка двуокиси кремния SiO2 , покрывающая поверхность кремниевой пластины. В этой пленке различными методами формируются окна необходимой формы.

Основным элементом биполярных ИС является n–p–n-транзистор (биполярный транзистор), и на его изготовление ориентируется весь технологический цикл. Все другие элементы, по возможности, изготавливаются с этим транзистором, без дополнительных технологических операций.

Основным элементом МДП (МОП) ИС является МДП (МОП)-транзистор.

Элементы биполярной ИС необходимо изолировать друг от друга, чтобы они не взаимодействовали через кристалл. Элементы МДП (МОП) ИС не нуждаются в специальной изоляции друг от друга. В этом одно из главных преимуществ МОП ИС по сравнению с биполярными.

В последнее время широкое распространение в качестве материала подложки получил арсенид-галлий. В полупроводниковых микросхемах на такой основе активными элементами служат полевые транзисторы с управляющим переходом металл-полупроводник (МЕП-транзисторы).

Размеры кристаллов у современных полупроводниковых ИС достигают 20´20 мм2 , а размеры фрагментов элементов ИС составляют десятые доли микрометра.

Исторические этапы микроэлектроники

Первый этап – изобретение точечного германиевого транзистора в 1948 году в лаборатории BellTelephoneLaboratories.

Второй этап – создание плоскостных кремниевых транзисторов в 1953 году на фирме TexasInstrumentIncorporation и налаживание их группового производства.

Третий этап – создание первой интегральной схемы в 1961 году на фирме FairchildSemiconductor, представляющей собой триггер, состоящий из четырех биполярных транзисторов и двух резисторов.

1. ОСНОВЫ ТЕОРИИ ИНТЕГРАЛЬНЫХ ЦИФРОВЫХ УСТРОЙСТВ

1.1 Логические основы цифровой интегральной электроники

Функционирование любой цифровой системы происходит в двоичной системе счисления, оперирующей только двумя цифрами: нуль (0) и единица (1). В данном случае имеется в виду логические нуль и единица.

Математический аппарат, на основе которого осуществляется описание цифровых схем, – это алгебра логики, или, как ее еще называют по имени автора – английского математика Джорджа Буля (1815-1864), булева алгебра. В практических целях первым применил ее американский ученый Клод Шеннон в 1938 году при исследовании электрических цепей с контактными выключателями.

Предметом рассмотрения алгебры логики является утверждение, которое может быть либо истинным, либо ложным. Принято «истинно» обозначать цифрой 1, «ложно» – цифрой 0.

Простые утверждения, объединенные логическими операциями, образуют сложные утверждения. Если простые утверждения обозначить буквами, например, A, B, C, …, а сложные буквой F, то, используя законы алгебры логики, можно описать математически сколь угодно сложную цифровую схему.

В алгебре логики известны три основные логические операции:

1. Логическое умножение (конъюнкция или операция И ). Записывается как F = A B, F = A·B, F = AB, читается – A и B. Операция обозначает, что сложное высказывание истинно лишь тогда, когда истинны все простые высказывания.

2. Логическое сложение (дизъюнкция или операция ИЛИ ). Записывается как F = AÚB, F = A+B, читается – F = A или B. Обозначает, что сложное высказывание истинно, если истинно хотя бы одно из простых высказываний, и тем более, если истинны оба.

3. Логическое отрицание (инверсия или операция НЕ ). Записывается F = Ā , читается – F = «не» A. Операция обозначает, что сложное высказывание истинно, если простое ложно, и наоборот.

Словесное описание приведенных логических операций можно свести к их табличному (табл. 1) описанию или заданию:

Таблица 1

Аргументы (простые высказывания) |

Логические операции (булевы функции) | ||||

| А | В | И | ИЛИ | НЕ | |

| AÙB | AÚB | ||||

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

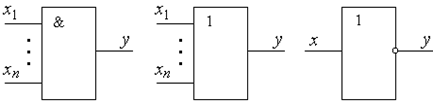

Таким образом, выполнение сколь угодно сложной логической операции может быть сведено к трем вышеперечисленным операциям. Следовательно, имея некоторые технические устройства, реализующие операции И , ИЛИ , НЕ , можно построить сколь угодно сложное цифровое устройство. Такие устройства называются соответственно логическими элементами И , ИЛИ , НЕ (рис. 2) и образуют основной базис или функционально полную систему логических элементов.

а б в

Рис. 2. Условное обозначение логических элементов на электрических схемах: И (а), ИЛИ (б), НЕ (в)

В интегральной цифровой электронике широко используются элементы других базисов: ИЛИ – НЕ (стрелка Пирса A↓B), а также И – НЕ (штрих Шеффера A│B), каждый из которых также является функционально полной системой элементов.

1.2 Кодирование сигналов в цифровых устройствах

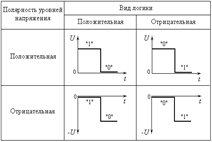

По виду кодирования электрических сигналов двоичными цифрами элементы цифровой техники делятся на потенциальные, импульсные и импульсно-потенциальные.

В потенциальных элементах нулю и единице соответствуют два резко отличающихся уровня – высокий и низкий. При этом напряжения могут быть как положительными, так и отрицательными относительно корпуса, электрический потенциал которого принимается за нулевой.

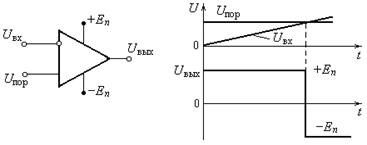

Различают элементы, работающие в положительной и отрицательной логике (рис. 3).

Рис. 3. Кодирование электрических сигналов в потенциальных элементах

Таким образом, для положительной логики характерны более высокие значения напряжений, которые соответствуют логической единице.

У импульсных цифровых устройств логическими нулями и единицами кодируются перепады напряжений, наличие или отсутствие импульса, полярность импульса.

В цифровых схемах используются также импульсно-потенциальные элементы, в которых одна часть сигналов кодируется различными уровнями напряжения, а другая – перепадами напряжения.

1.3 Классификация цифровых устройств

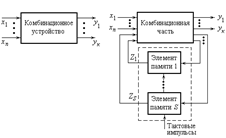

В общем случае на вход цифрового устройства поступает множество двоичных переменных X(x1 … xn ), а с выхода снимается множество двоичных переменных Y(y1 … yk ),. Устройство при этом осуществляет определенную логическую функцию между входными и выходными переменными.

Цифровые устройства можно разделить на комбинационные и последовательностные.

В комбинационных – значения Y в течение каждого такта определяются только значениями X в этом же такте. Такие устройства состоят из логических элементов.

В последовательностных – значения Y определяются значениями X, как в течение рассматриваемого такта, так и существовавшими в ряде предыдущих тактов. Для этого в последовательностных устройствах, кроме логических должны быть еще и запоминающие элементы.

Структура последовательностного и комбинационного устройства приведена на рис. 4.

а б

а б

Рис. 4. Структура комбинационного а и последовательностного б цифровых устройств

Запоминающее устройство может хранить информацию не бесконечно большого, а только ограниченного числа тактов, поэтому цифровые устройства с памятью называют конечными автоматами, к которым относят все ЭВМ.

Таблицы, показывающие взаимосвязь между входными и выходными переменными комбинационных устройств, называют таблицами истинности. Алгебраическая форма этих связей представляет систему уравнений

y1 = y1 (x1 , x2 , …, xn ),

yk = yk (x1 , x2 , …, xn ).

В общем виде в последовательностных устройствах выходные переменные yi зависят не только от входных сигналов xm , но и от сигналов элементов памяти, поступающих за этот же такт.

В частности, в автоматах Мили выходные сигналы формируются именно таким образом, т. е.

yi t+1 = fi (x1 , x2 , …, xn , z1 , z2 , …, zs )t+1 .

Это выражение называется функцией выхода автомата Мили.

В автоматах Мура выходные сигналы являются функциями только сигналов элементов памяти в этом же такте, т.е.

yi t+1 = fi (z1 , z2 , …, zs )t+1 .

Это выражение называется функцией выхода автомата Мура.

Для описания работы последовательностных устройств используются таблицы переходов состояний.

Таблицы истинности соответствуют только статическим или установившимся режимам работы цифровых устройств. При изменении входных сигналов в комбинационной схеме из-за инерционности логических элементов в ней начинает протекать переходный процесс. Максимальная длительность переходного процесса определяется максимальным числом последовательно включенных ЛЭ. Входные сигналы xm изменяются не мгновенно, а в течение некоторого времени τф , т. е. сигналы имеют фронты конечной длительности. В течение этого времени входные сигналы имеют неопределенное значение. По этой причине, а также из-за задержек сигналов в ЛЭ выходные сигналы комбинационной схемы в течение переходного процесса могут принимать значения не соответствующие описывающим их функциям. Это явление называют переходными состояниями или «гонками». Появление кратковременных ложных значений выходных сигналов комбинационной схемы может привести к неправильному срабатыванию других схем, подключенных к ее выходам.

Цифровые устройства можно разделить на асинхронные и синхронные. В асинхронных изменение входных сигналов сразу же вызывает изменение выходных сигналов. В синхронных изменение выходных сигналов, соответствующее новому сочетанию входных, происходит только после подачи синхронизирующих (тактовых) импульсов, управляющих работой автомата. Период синхроимпульсов является, таким образом, минимальным временем между выполнением автоматом двух последовательных микроопераций, т.е. служит единицей машинного времени, называемой тактом. В зависимости от структуры автомата за один такт могут выполняться одна или несколько микроопераций, если они совмещены во времени.

В асинхронных устройствах отсутствуют синхронизирующие сигналы, поэтому в их структуры обычно включаются специальные схемы, которые после окончания каждой микрооперации вырабатывают сигнал готовности к выполнению следующей микрооперации.

Синхронные устройства, в принципе, имеют меньшее быстродействие, чем асинхронные, однако в них легко устраняются опасные состязания.

1.4 Основные теоремы и положения алгебры логики

Принцип двойственности

Запишем алгоритм выполнения операций ИЛИ и И , расположив строки таблицы для операции И в обратном порядке – снизу вверх:

Или 0 Ú 0 = 0 и 1 · 1 = 1

0 Ú 1 = 1 1 · 0 = 0

1 Ú 0 = 1 0 · 1 = 0

1 Ú 1 = 1 0 · 0 = 0

Если в этих таблицах переменные заменить их инверсиями, а знаки дизъюнкции на знаки конъюнкции и наоборот, то алгоритмы меняются местами. Таблица истинности для ИЛИ становится таблицей истинности для И и наоборот.

В этом состоит принцип двойственности, который в общем виде записывается так:

![]() ,

, ![]() .

.

Для любого числа переменных это правило, называемое еще теоремой де Моргана, имеет вид:

![]() ;

; ![]() .

.

На практике принцип двойственности приводит к тому, что логический элемент, выполняющий в положительной логике операцию И , в случае отрицательной логики будет выполнять операцию ИЛИ .

Для преобразования выражений алгебры логики с целью их упрощения или приведения к удобному виду используются, как и в обычной алгебре, скобки, а если их нет, то сначала выполняется отрицание (инверсия) над отдельными переменными, затем логическое умножение (конъюнкция), затем логическое сложение (дизъюнкция). Если же знак инверсии расположен над целым выражением, то она выполняется в последнюю очередь.

В алгебре логики используется целый ряд теорем.

Теоремы для одной переменной :

1. A Ú 0 = A4. A Ú Ā = 17. A · A = A

2. A Ú 1 = 15. A · 0 = 08. A · Ā = 0

3. AÚA = A6. A · 1 = 19. ![]()

Теоремы для двух и более переменных :

10. а) A Ú B = B Ú A, б) AB = BA

переместительный закон, означает, что все входы логического элемента равнозначны.

11. а) A Ú B Ú C = A Ú (B Ú C) = (A Ú B) Ú C,

б) ABC = A(BC) = (AB)C – сочетательный закон.

12. а) A (B Ú C) = AB Ú AC, б) A Ú BC = (A Ú B)(A Ú C) –

распределительный закон.

Данная теорема и все последующие вытекают из принципа двойственности. Применим его к выражению 12, а:

![]() – левая часть,

– левая часть,

![]() – правая часть.

– правая часть.

Введя новые обозначения: ![]() , получим обозначения:

, получим обозначения: ![]() , а это и есть теорема 12, б.

, а это и есть теорема 12, б.

13. а) A Ú AB = A, б) A(A Ú B) = A

– закон поглощения (A поглощает B).

Доказательство 13, а:

AÚAB = A(1 ÚB) = A · 1 = A, (используя теоремы 2, 6).

Теорема 13, б следует из принципа двойственности.

14. а) ![]() , б)

, б) ![]() .

.

Доказательство 14.а:

![]() , (используя теоремы 8 и 1).

, (используя теоремы 8 и 1).

Теорема 14, б следует из принципа двойственности.

15. а) AB Ú ĀB = B, б) (A Ú B)(Ā Ú B) = B, закон склеивания (склеивание по A).

Доказательство 15, а:

AB Ú ĀB = B(A Ú Ā) = B · 1 = B, (используя теоремы 4 и 6).

Теорема 15, б следует из принципа двойственности.

Логические (булевы) функции

Булева функция (F) является результатом выполнения логических операций над двоичными переменными – аргументами (A, B, C, …) и полностью зависит от их значений.

Задать булеву функцию – значит указать ее значения (0 или 1) при всех возможных комбинациях значений переменных.

Каждая комбинация аргументов называется набором, при N аргументах существует 2N наборов.

Если, известны значения функции на всех наборах аргументов, она называется полностью определенной. Если же на некоторых наборах значение функции неизвестно, то она называется недоопределенной, а соответствующие наборы – запрещенными наборами. Значения функции на запрещенных наборах можно задать по своему усмотрению (доопределить функцию).

Логические функции могут иметь различные формы представления: словесное, табличное, алгебраическое, графическое.

Рассмотрим два примера словесного задания булевой функции.

Полностью определенная функция F1 трех аргументов A, B, C принимает значение 1, если два любых аргумента (или все три) равны 1. В других случаях функция равна нулю. Количество наборов равно 23 = 8.

Недоопределенная функция F2 трех аргументов A, B, C принимает значение 1, если два любых аргумента равны 1, и равна нулю в остальных случаях, кроме случаев однозначности всех трех аргументов.

Если пронумеровать наборы от 0 до 23 – 1, эти словесно заданные функции можно представить в виде таблицы истинности (табл. 1).

Таблица 1

| Номера наборов | A | B | C | F1 | F2 | F3 | F4 |

| 0 | 0 | 0 | 0 | 0 | – | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 3 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 | – | 1 | 1 |

Функция F 2 не определена на 0 и 7 наборах, где все три аргумента однозначны, поэтому в таблице 1 против этих наборов проставлены прочерки.

Отдельный интерес представляют функции F3 и F4 .

Конституентой единицы (F3 ) называют функцию n аргументов, которая принимает значение, равное единице, только на одном наборе аргументов. На всех остальных наборах она равна нулю.

Конституентой нуля (F4 ) называют функцию n аргументов, которая принимает значение, равное нулю, только на одном наборе аргументов.

От табличного задания булевой функции можно перейти к ее алгебраическому представлению, причем в двух формах: совершенной дизъюнктивной, нормальной форме и совершенной конъюнктивной, нормальной форме.

Совершенной дизъюнктивной, нормальной формой (Сов ДНФ) функции называют дизъюнкцию конституент единицы – минтермов, взятых на тех наборах, на которых единице равна сама функция.

Минтерм – конъюнкция всех переменных в наборе, которые берутся в прямом виде, если их значение равно единице, либо в инверсном виде, если их значение в наборе равно нулю.

Функция F1 в Сов ДНФ будет иметь вид:

![]() .

.

Совершенной конъюнктивной, нормальной формой (Сов КНФ) функции называют конъюнкцию конституент нуля – макстермов, взятых на тех наборах, на которых нулю равна сама функция.

Макстерм – дизъюнкция всех переменных в наборе, которые берутся в прямом виде, если их значение равно нулю, либо в инверсном виде, если их значение в наборе равно единице.

Функция F1 в Сов КНФ примет вид:

![]() .

.

Теоремы булевой алгебры позволяют достаточно просто перейти от одной формы представления булевой функции к другой. Однако, с точки зрения минимизации алгебраических выражений более удобна Сов ДНФ.

1.5 Минимизация булевых функций

Аналитические методы минимизации

Используя законы булевой алгебры, можно получить для одной и той же логической функции множество эквивалентных представлений. Чем проще аналитическое выражение функции, тем экономичнее и проще ее практическая реализация на интегральных микросхемах. Сложность булевой функции определяется ее рангом, т.е. количеством переменных в ее конъюнктивных или дизъюнктивных членах.

Представление булевой функции в Сов ДНФ в большинстве случаев не является минимальным.

Используя операции поглощения и склеивания, его можно существенно упростить. Часто используется неполное склеивание, при котором оба члена, участвовавших в склеивании (или один из них), могут повторно склеиваться с другими оставшимися членами Сов ДНФ.

В процессе минимизации важно отыскать смежные конституенты, которые отличаются только одним аргументом (в одну конституенту аргумент входит с инверсией, а в другую – без нее).

Две смежные конституенты, склеиваясь, образуют импликанту рангом на единицу ниже, чем исходные конституенты.

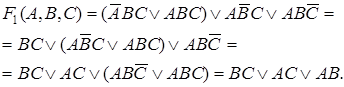

Используя, например, неполное склеивание последней коституенты в Сов ДНФ функции F1 последовательно с остальными, приходим к следующему выражению:

Процесс многоступенчатого склеивания приводит к импликантам, которые не склеиваются с другими. Такие импликанты называют простыми. Форма записи булевой функции в ДНФ, состоящая только из простых импликант, называется сокращенной дизъюнктивной нормальной формой (Сокр ДНФ).

В некоторых случаях в Сокр ДНФ могут содержаться лишние импликанты, которые могут быть исключены без изменения значения функции.

Одним из методов отыскания лишних импликант является метод испытания членов: чтобы испытать некоторый член функции, следует исключить его из Сокр ДНФ и подставить в оставшееся выражение такие значения аргументов, которые обращают исключенный член в единицу. Если при такой подстановке оставшееся выражение окажется тождественно равным единице, то испытуемый член является лишним.

Найдем для примера тупиковую форму Сокр ДНФ

![]() .

.

Испытаем член AC. AC = 1, если A = 1 и C = 1. Подставим в оставшееся выражение ![]() A = 1 и C = 1, получим

A = 1 и C = 1, получим

![]() .

.

При B = 0 F(A, B, C) = 1·1 Ú 0·0 = 1, но при ![]() F(A, B, C) = 0·1 Ú 0·0 = 0. Следовательно, член ACне лишний.

F(A, B, C) = 0·1 Ú 0·0 = 0. Следовательно, член ACне лишний.

Испытаем член BC, равный 1 при B = 0, C = 1. При этом

![]() .

.

Последнее выражение равно 1 как при A = 1, так и при A = 0. Поэтому член ![]() – лишний.

– лишний.

Испытание члена ![]() по этой же методике показывает, что он не является лишним, в итоге тупиковая форма исходной функции имеет вид:

по этой же методике показывает, что он не является лишним, в итоге тупиковая форма исходной функции имеет вид:

![]() .

.

Минимизация булевых функций с помощью карт Карно

Для минимизации функций относительно небольшого числа переменной (не более шести) наиболее простым и наглядным является графический метод, использующий карты Карно.

Карта Карно – это прямоугольник, разбитый на квадраты, число которых равно числу наборов рассматриваемой функции, т. е. 2n . Клетки размечаются так, чтобы наборы, для которых возможны смежные конституенты, оказались бы в соседних клетках.

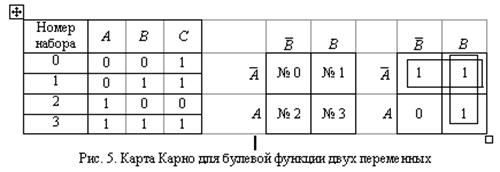

При заполнении карты Карно в ее клетки проставляют значения функции для соответствующих наборов, которые являются координатами клеток. Например, для функции двух переменных А и В (рис. 5) карта Карно имеет вид

Единицы, представленные в клетках, обозначают конституенты единицы рассматриваемой функции. Отыскание минимальной ее формы сводится к определению варианта, при котором все конституенты единицы накрываются (охватываются контурами покрытия) наименьшим числом наиболее коротких импликант. Объединение клеток на карте эквивалентно выполнению операции склеивания.

Всегда нужно стремиться к минимальному количеству контуров и максимальной площади каждого из них, руководствуясь следующими правилами:

· площадь контура покрытия должна быть Sk

= 2m-i

клеток, где ![]() – целое число, m – число переменных. Если, например, m = 3, то Sk

= 1, 2, 4, или 8 клеток;

– целое число, m – число переменных. Если, например, m = 3, то Sk

= 1, 2, 4, или 8 клеток;

· число сокращаемых переменных Nперем. = log2 Sk , т.е. при Sk = 1 не сокращается ни одна переменная, при Sk = 2 сокращается одна переменная и т.д.

В примере на рис. 5 пара единиц верхней строки охватывается импликантой Ā (т.е. обе клетки ) имеют общий аргумент Ā). Пара единиц правого столбца накрывается импликантой B, как общей для обеих клеток. Следовательно, минимальная ДНФ функции F(A,B) = Ā Ú B.

Если имеется несколько вариантов объединения конституент контурами, то можно получить несколько различных эквивалентных минимальных ДНФ функции, одна из которых выбирается для реализации в цифровом устройстве.

Карту Карно удобно использовать и для минимизации функций, заданных в алгебраической форме, например,

![]() .

.

Карта Карно, состоящая из 23 = 8 клеток, может быть размечена, как показано на рис. 6.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() При охвате единиц контурами склеивания карту Карно можно сворачивать в цилиндр, как вдоль горизон-тальной, так и вертикальной оси. В результате все четыре единицы, расположенные в углах Карты, охватываются контуром с общей импликан-той

При охвате единиц контурами склеивания карту Карно можно сворачивать в цилиндр, как вдоль горизон-тальной, так и вертикальной оси. В результате все четыре единицы, расположенные в углах Карты, охватываются контуром с общей импликан-той ![]() . Такой минимизации соответствует выражение

. Такой минимизации соответствует выражение

![]() .

.

Минимизация недоопределенных функций

Недоопределенность функции означает, что запрещенные наборы никогда не появятся в процессе работы устройства. Значит, такую функцию можно произвольно доопределить, установив ее значения на запрещенных наборах, и это не отразится на работе устройства, но обчит его реализацию.

Пусть необходимо минимизировать булеву функцию, заданную картой Карно (рис. 7).

Если группировать единицы в контурах только по исходному заданию (рис. 7, а), то минимальная форма функции будет иметь вид:

![]() .

.

После доопределения функции (рис. 7, б), ее минимальная ДНФ (заметим, что это будет уже другая полностью определенная функция j) оказывается предельно простой

![]() .

.

Функция j, значения которой совпадают со значениями заданной функции F на тех наборах, где F определена, называется эквивалентной.

Таким образом, задача минимизации недоопределенной функции сводится к отысканию такой эквивалентной функции, которая имеет простейшую форму.

При синтезе комбинационных схем всегда возникает вопрос выявления опасных состязаний. С этой целью на практике пользуются простым и удобным формальный критерием Хаффмена: статические опасные состязания в устройстве с минимизированной структурой могут иметь место, если на карте Карно при охвате соседних клеток контурами склеивания окажутся хотя бы две соседние клетки, не покрытые контуром.

Поэтому устранение опасных состязаний достигается возвращением импликант, которые оказались лишними при переходе от сокращенной к тупиковой ДНФ.

1.6 Реализация логических функций на элементах И–НЕ, ИЛИ–НЕ

При реализации цифровых устройств на интегральных микросхемах широко используются базисы И-НЕ или ИЛИ-НЕ . Для этого минимизированные логические функции путем преобразований приводятся к соответствующему виду.

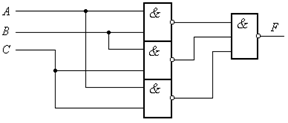

Пусть минимальная ДНФ функция

![]() .

.

Применим к этому выражению двойное отрицание и теорему де Моргана

![]() .

.

Как видно, функция F включает только операции И-НЕ , и ее реализация в базисе И-НЕ имеет вид (рис. 8)

Рис. 8. Реализация функции ![]() в базисе И-НЕ

в базисе И-НЕ

Аналогичным образом от КНФ функции можно перейти к ее форме, удобной для реализации в базисе ИЛИ-НЕ .

2. ЭЛЕМЕНТНАЯ БАЗА ЦИФРОВЫХ СИСТЕМ

2.1 Принципы построения полупроводниковых ключевых схем

В цифровой электронике ключевая схема предназначена для коммутации (переключения) тока в нагрузке или создания двух резко отличающихся уровней напряжения на нагрузке, соответствующих логическому нулю и логической единице.

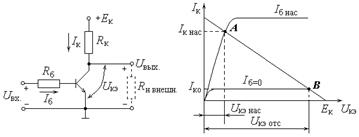

Ключевая схема на биполярном транзисторе

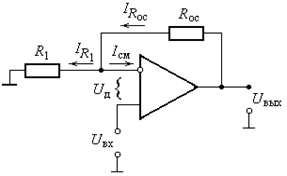

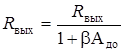

В интегральных микросхемах выполненных на биполярных транзисторах роль ключа выполняет транзистор, включенный по схеме с общим эмиттером (рис. 9).

а б

а б

Рис.9. Ключевая схема на биполярном транзисторе: а- принципиальная схема; б – вольт/амперная характеристика (ВАХ) ключа

Управление состоянием ключа осуществляется сигналом Uвх . При Uвх = 0 соответственно Iб = 0 и состояние схемы определяется точкой B на ВАХ ключа. Транзистор находится в состоянии отсечки, что эквивалентно разомкнутому ключу, а выходное напряжение Uвых равно Uкэ отс , т. е. несколько меньше, чем Eк . Ток через транзистор Iко в этом случае пренебрежительно мал.

При Uвх

, достаточном для создания базового тока Iб нас

, переводящего транзистор в режим насыщения, состояние схемы определяется точкой А

на ВАХ, что равносильно замкнутому ключу. Выходное напряжение равно Uкэ нас

, т.е. несколько выше нулевого уровня, а ток через транзистор Iк нас

максимален и равен ![]() .

.

Оценим энергетические затраты в ключевой схеме:

1.В режиме отсечки мощность, выделяемая на транзисторе и вызывающая его нагревание, определяется выражением

Pотс = Iко × Uкэ отс .

Вследствие крайней малости Iко , мощность Pотс значительно меньше допустимой величины.

2.В режиме насыщения мощность Pнас = Iк нас × Uкэ нас . Так как Uкэ нас мало, Pнас также находится в допустимых пределах.

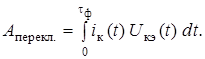

3.Более подробно рассмотрим процесс переключения – процесс перехода ключа из одного состояния в другое.

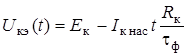

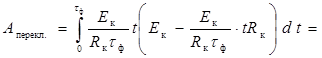

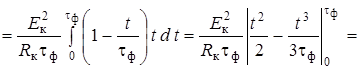

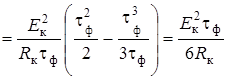

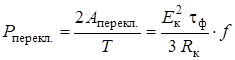

Так как переключение транзистора происходит не мгновенно, а в течение времени tф , ток iк (t) и напряжение Uкэ (t) достигают относительно высоких величин. На переключение транзистора затрачивается энергия

Допустив, что ток iк (t) за время переключения изменяется по линейному закону, т.е. iк (t)=Iнас × t/tф , и, считая, что Rк , Eк известны, получим

.

.

Тогда с учетом

Если транзистор ключа переключается с частотой f, то мощность, выделяемая на нем, будет равна

,

,

где  – период переключения.

– период переключения.

В этом случае, в зависимости от частоты переключения и режимов работы ключа, Pперекл. может достигать значительных величин.

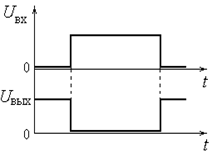

Идеализированная временная диаграмма работы ключа приведена на рис. 10.

Анализ временной диаграммы работы ключевой схемы (рис. 9) показывает, что для статистического режима если Uвх – низкий потенциал, то Uвых – высокий, и наоборот. Следовательно, простейшая ключевая схема на транзисторе с нагрузкой в цепи коллектора, с которого снимается выходное напряжение, является инвертором, реализующим функцию НЕ как в положительной, так и в отрицательной логике.

Рис. 10. Идеализированная временная диаграмма работы ключа

Ключевая схема на полевых транзисторах

Ключевые схемы на полевых транзисторах имеют следующие преимущества перед биполярными:

·малое сопротивление в открытом состоянии,

·высокое сопротивление в закрытом состоянии,

·незначительная мощность, потребляемая от источника управляющего сигнала.

Схемотехнически полупроводниковые ключи на биполярном и полевом транзисторе практически идентичны.

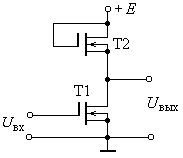

Однако в интегральной схемотехнике в качестве нагрузочного резистора Rиспользуется МДП-транзистор того же типа, что и транзистор, выполняющий роль ключа (рис. 11).

Рис. 11. Ключевая схема на МДП-транзисторах

Это позволяет сократить число технологических операций при изготовлении микросхем. Чтобы транзистор Т2 выполнял роль резистора необходимо обеспечить постоянно открытое состояние его канала. Для этого затвор транзистора Т2 соединяют с его стоком.

Ключевая схема на комплементарных транзисторах

В рассмотренных ключевых схемах существенным недостатком является протекание тока через сопротивление Rк как в открытом, так и в закрытом состояниях и, как следствие его значительное нагревание.

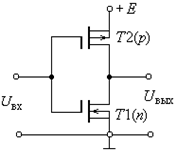

Этого недостатка лишен инвертор на комплементарных (взаимодополняющихся) МДП-транзисторах (рис. 12).

Рис. 12. Комплементарный МДП-транзисторный ключ

Схема построена на двух транзисторах Т1 и Т2 с одинаковыми характеристиками, но с каналами разных типов проводимости. Схема симметрична: когда один из транзисторов выполняет роль замкнутого ключа, то другой служит нагрузочным сопротивлением и наоборот.

В положительной логике и при положительной полярности напряжения питания при подаче на вход схемы логического 0 (Uвх » 0 В) транзистор Т1 будет заперт, а транзистор Т2 оказывается в режиме глубокого насыщения и через него потенциал +Е поступает на выход, реализуя на выходе логическую 1. Сквозной ток протекающий через оба последовательно соединенных транзистора практически равен нулю, так как сопротивление закрытого транзистора Т1 очень велико.

Если на вход ключа подана логическая 1, то состояния транзисторов меняется на противоположное и через открытый транзистор Т1 на выход будет подан нулевой потенциал корпуса Uвых » 0 В, реализуя логический 0. При этом сквозной ток по прежнему останется близким к нулю вследствие большого сопротивления запертого транзистора Т2.

Таким образом, в статическом состоянии схема практически не потребляет мощности от источника питания.

В режиме переключения имеется некоторый интервал входных сигналов при которых открыты оба транзистора и сквозной ток может достигать значительных величин. Однако для КМДП-ключей типичны низкие напряжения питания, так что заметного возрастания тока во время переключения обычно не происходит.

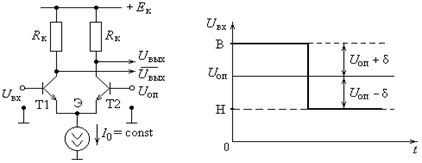

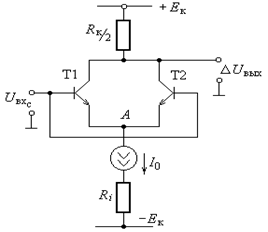

Переключатель тока

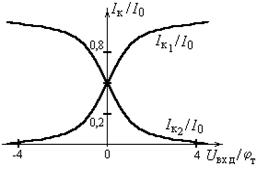

Переключателем тока называют симметричную схему (рис. 12.), в которой заданный ток I0 протекает через ту или иную ее ветвь в зависимости от потенциала Uвх на одном из входов. На втором входе поддерживается некоторое неизменное опорное напряжение Uоп .

а б

а б

Рис. 13. Переключатель тока: а – электрическая схема;

б – временная диаграмма его работы

Опорное напряжение Uоп равно промежуточному значению между напряжениями высокого (В) и низкого (Н) уровней выходного напряжения.

Так как эмиттеры транзисторов соединены между собой, то падение напряжения Uэ прикладывается одновременно к базам Т1 и Т2

Если на вход переключателя подан высокий уровень (В) т. е. Uвх = Uоп + d, то транзистор Т1 будет открытым, так как на его базе будет прямое напряжение Ud э1 = Uвх – Uэ > 0, а Т2 закрыт (Ud э2 = Uоп – Uэ < 0). Каждая из ветвей переключателя представляет собой инвертор, поэтому на выходе Uвых1 будет низкий потенциал, на выходе Uвых2 – высокий.

Если на вход подан низкий уровень (Н), т. е. Uвх = Uоп – d, то откроется Т2, а Т1 закроется. Обычно величины ïdï= 0,1 … 0,5 В достаточно для перевода схемы из одного состояния в другое, сохраняя активный режим открытого транзистора.

Таким образом особенность переключателей тока состоит в использовании ненасыщенного режима работы транзисторов, что обеспечивает их повышенное быстродействие и по той же причине повышенные энергетические затраты в статическом режиме.

2.2 Переходные процессы в ключевых схемах

В реальных ключевых схемах изменение состояния транзисторов под действием ступенчатого входного напряжения происходит в течение некоторого времени, зависящего от целого ряда факторов: типа транзистора ключа, режимов его работы, характера нагрузки и т.д. При этом изменения выходных токов ключа при отпирании и запирании транзистора отличаются от линейного закона, а форма выходного напряжения значительно отличается от формы входного.

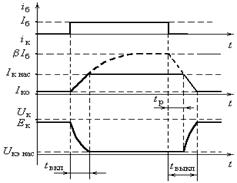

Переходные процессы биполярного ключа

Процесс переключения биполярного транзистора определяется двумя факторами: процессами накопления и рассасывания неосновных носителей в базе, формирующих ток коллектора ik , и наличием емкостей эмиттерного и коллекторного переходов Cэ и Cк , которые перезаряжаются при переключениях. Если входное напряжение Uвх равно нулю, то транзистор закрыт и ток коллектора ik равен неуправляемому току Iк0 (рис. 14).

Рис.14. Переходные процессы в ключе на биполярном транзисторе

При подаче входного напряжения ступенчатой формы появляется базовый ток Iб такой же формы. Если величина Iб достаточна для ввода транзистора в насыщение, то возрастающий ток коллектора будет стремиться к уровню bIб , где b – коэффициент усиления тока транзистора. Нелинейный характер нарастания ik определяется наличием емкостей переходов база-эмиттер (Cэ ) и база-коллектор (Cк ). Максимальное значение ik ограничено сопротивлением Rk и не может превысить величины

![]() .

.

Значение коллекторного тока, в тоже время, определяется количеством неосновных носителей в базе, поэтому, когда ток ik достигнет величины Ikнас , его рост прекратится, но рост числа носителей заряда в базе будет расти до величины соответствующей току Iб . Таким образом, в базе транзистора накапливается избыточный заряд неосновных носителей, не участвующих в создании коллекторного тока.

Как видно из диаграммы, процесс открывания транзистора занимает некоторый интервал времени tвкл . Уменьшение этого времени на практике достигают повышением в 1,5¼3 раза базового тока, по отношению к току, достаточному для введения транзистор в насыщение.

Однако увеличение базового тока в этом случае приводит к увеличению избыточного заряда неосновных носителей в базе, которые после снятия входного сигнала (отключения тока Iб ) продолжают поддерживать некоторое время tр коллекторный ток неизменным. Отрезок времени tр называют временем рассасывания неосновных носителей из базы. Только после удаления избыточного заряда из базы начинается процесс уменьшения коллекторного тока до уровня Iк0 .

В быстродействующих ключевых схемах принимают меры для уменьшения tр , и соответственно, tвыкл , в целом.

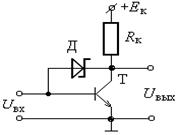

Ключевая схема на транзисторе Шоттки

Процесс рассасывания можно устранить, если транзистору сразу же после отирания создать режим, когда бы он находился на границе между состоянием насыщения и активным режимом работы. Этого можно достичь шунтированием перехода коллектор-база транзистора диодом Шоттки (рис. 15).

Рис. 15. Ключевая схема на транзисторе Шоттки

Когда транзистор закрыт или работает в активном режиме, потенциал коллектора выше потен-циала базы и, следовательно, диод закрыт и не влияет на работу клю-ча. В режиме насыщения, когда транзистор полностью открыт, потенциал его коллектора оказывается ниже потенциала базы, что приводит к открыванию диода, на котором устанавливается напряжение менее 0,5 В, т. е. меньше напряжения, открывающего переход база–коллектор. Транзистор тем самым окажется на грани насыщения, так как диод зашунтирует через себя ту часть тока базы, которая создала бы избыточный заряд.

В интегральном исполнении диод Шоттки представляет собой контакт металла с коллекторной областью транзистора и составляет единую структуру, называемую транзистором Шоттки. Особенностью диода Шоттки является низкое прямое падение на нем напряжения порядка 0,4 В.

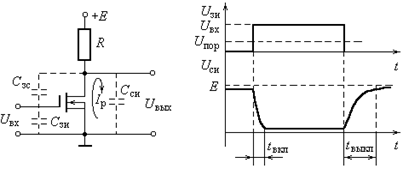

Переходные процессы в ключевой схеме на МДП-транзисторе

Основное влияние на характер протекания переходных процессов в ключевых схемах на полевых транзисторах оказывают емкости, образованные между их выводами (рис. 16).

а б

а б

Рис. 16. Переходные процессы в ключевой схеме на МДП-транзисторах: а – эквивалентная схема, б – временные диаграммы

При закрытом транзисторе выходная емкость Cси заряжена до напряжения, практически равного E. Когда входное напряжение превышает пороговое напряжение Uпор (напряжение открывания транзистора) в течение времени задержки

формируется проводящее состояние канала. Однако, при достаточно низком сопротивлении Rвн источника входного сигнала Uвх время задержки пренебрежимо мало.

Как только канал сформирован, емкость Cси начинает разряжаться постоянным током Iр , определяемым небольшим сопротивлением проводящего канала транзистора, в течение времени tвкл . За это время выходное напряжение ключа падает до величины близкой к нулю.

При запирании транзистора (уменьшение Uвх до нуля) происходит зарядка емкости Cси через резистор R от напряжения источника питания Eв течение времени tвыкл . Это время, как правило, больше времени включения, так как сопротивление нагрузочного резистора R значительно больше сопротивления канала транзистора в проводящем состоянии.

В комплементарном ключе заряд и разряд нагрузочной емкости происходит в одинаковых условиях через открытый проводящий канал. Это объясняется симметрией схемы относительно входного напряжения и нагрузки. Соответственно, интервалы времени tвкл и tвыкл примерно одинаковы и почти на порядок меньше, чем у обычного ключа на МДП-транзисторах. Это преимущество сохраняется и при уменьшении напряжения питания.

3. Цифровые интегральные логические элементы

В процессе развития интегральной электроники выделилось несколько типов схем логических элементов, имеющих достаточно хорошие характеристики и удобных для реализации в интегральном исполнении, которые служат элементной базой современных цифровых микросхем.

Базовые элементы, независимо от их микросхемотехники и особенностей технологий изготовления, строятся в одном из базисов (как правило, в базисе И –НЕ или ИЛИ –НЕ ).

Базовые элементы выпускаются в виде отдельных микросхем, либо входят в состав функциональных узлов и блоков, реализованных в виде СИС, БИС, СБИС.

В процессе реализации базовые логические элементы строят из двух частей: входной логики, выполняющей операции И или ИЛИ , и выходного каскада, выполняющего операцию НЕ .

Входная логика может быть выполнена на диодах, биполярных и полевых транзисторах. В зависимости от этого различают:

· транзисторно-транзисторную логику (ТТЛ), (ТТЛШ),

· интегральную инжекционную логику (И2 Л),

· логику на МДП-транзисторах (МДП),

· МОП-транзисторная логика на комплементарных транзисторах (КМОП-логика).

В перечисленных группах логических элементов в качестве выходного каскада используется ключевая схема (инвертор).

Другая группа логических элементов основана на переключателях тока – эмиттерно-связанная логика (ЭСЛ-логика).

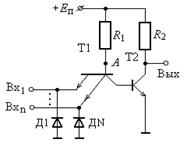

Транзисторно-транзисторная логика (ТТЛ)

Основой транзисторно-транзисторной логики является базовый элемент на основе многоэмиттерного транзистора Т1 (рис. 17), который легко реализуется в едином технологическом цикле с транзистором Т2. В ТТЛ-логике многоэмиттерный транзистор осуществляет в положительной логике операцию И , а на транзисторе Т2 собран инвертор. Таким образом, по данной схеме реализован базис И–НЕ .

Рис. 17. Базовый элемент ТТЛ

В случае подачи на все входы схемы высокого потенциала, все переходы эмиттер–база транзистора Т1 окажутся запертыми так как потенциал в точке Aпримерно равен входным сигналам. В то же время, переход база–коллектор будет открытым, поэтому по цепи Eп – R1 – база Т1 – коллектор Т1 – база Т2 – эмиттер Т2 – корпус течет ток Iб нас , который открывает транзистор Т2 и вводит его в насыщение. Потенциал на выходе схемы оказывается близким к нулю (на уровне ≈ 0,1 В). Сопротивление R1 подобрано таким, чтобы, за счет падения напряжения на нем от тока Iб нас транзистора Т2, потенциал в точке A был бы ниже, чем потенциал входов, и эмиттеры Т1 оставались бы запертыми.

При подаче низкого потенциала логического нуля хотя бы на один из входов открывается этот переход эмиттер–база транзистора Т1, появляется значительный ток Iэ

и потенциал в точке A, равный ![]() , приближается к нулевому. Разность потенциалов между базой и эмиттером Т2 также становится равной нулю, ток Iб

транзистора Т2 прекращается, и он закрывается (переходит в режим отсечки). В результате выходное напряжение приобретает значение, равное напряжению питания (логической единицы).

, приближается к нулевому. Разность потенциалов между базой и эмиттером Т2 также становится равной нулю, ток Iб

транзистора Т2 прекращается, и он закрывается (переходит в режим отсечки). В результате выходное напряжение приобретает значение, равное напряжению питания (логической единицы).

Входные диоды Д1, … , ДN предназначены для демпфирования (отсечки) отрицательных колебаний, которые могут присутствовать во входных сигналах за счет паразитных элементов предыдущих каскадов.

Существенным недостатком рассмотренной схемы элемента И–НЕ являются низкие нагрузочная способность и экономичность ее инвертора, поэтому в практических схемах используют более сложный инвертор.

В конце 70-х годов началось широкое применение серий элементов на транзисторах Шоттки с повышенным быстродействием за счет уменьшения задержки выключения ключей. По принципу действия базовый элемент ТТЛШ аналогичен ТТЛ-элементу.

Необходимо заметить, что схемам ТТЛ и ТТЛШ свойственен большой логический перепад напряжений, равный

![]() .

.

Интегральная инжекционная логика (И2 Л)

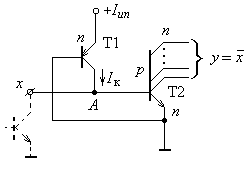

Схемы И2 Л не имеют аналогов в дискретных транзисторных схемах, т. е. характерны именно для интегрального исполнения. Основой И2 Л элементов является инвертор (рис. 18), составленный из двух транзисторов.

Рис. 18. Базовый элемент инжекционной логики

Транзистор Т1 является транзистором n-p-n типа, а транзистор Т2 – p-n-p типа, причем одна из областей n‑типа является как базой транзистора Т1, называемого инжектором (отсюда и название логики), так и эмиттером транзистора Т2, а база транзистора Т2 является коллектором инжектора. Функционально транзистор Т1 выполняет роль нагрузочного резистора, а Т2 – полупроводникового ключа.

Выходной транзистор – многоколлекторный, что обеспечивает развязку выходов друг от друга. Если ключевой транзистор предыдущей схемы открыт, то через него замыкается на корпус ток Iк транзистора Т1, заданный внешним источником тока, и не поступает в базу транзистора Т2, оставляя его закрытым.

Если же ключевой транзистор предыдущей схемы заперт, то ток Iк потечет в базу Т2 и вызовет его открывание. Таким образом рассматриваемый базовый элемент реализует операцию НЕ , принимая открытое состояние Т2 за нуль, а запертое – за единицу.

Соединив параллельно (рис. 19) два базовых элемента, можно получить реализацию базиса ИЛИ-НЕ .

Рис. 19. Реализация схемы ИЛИ–НЕ в логике И2 Л

В качестве источников тока питания Iип служат генераторы токов на p-n-p транзисторах, включенных по схеме с общей базой. Из-за отсутствия в схеме резисторов и общих для обоих транзисторов областей p и n‑типа схема очень технологична и в интегральном исполнении позволяет достичь плотности упаковки в 50 раз выше, чем при ТТЛ технологии.

При напряжении питания 1,5 В значение высокого потенциала порядка 0,7 В, а низкого – 0,05 В. Так как транзистор Т1 представляет высокоомную нагрузку, потребляемая элементом мощность может быть снижена до чрезвычайно низкой величины (раз в 100 меньше, чем у ТТЛ-элементов). Поэтому элементы И2 Л нашли широкое применение в БИС (серии КР582, 584).

В сериях ИС невысокой степени интеграции логика И2 Л не эффективна из-за низкого логического перепада, равного 0,65 В, и поэтому, низкой помехоустойчивости. Кроме того, по быстродействию, вследствие глубокого насыщения транзисторов инвертора, И2 Л-элементы уступают ТТЛШ-элементам.

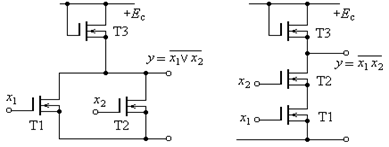

Логические элементы на МДП-транзисторах

В настоящее время в логических схемах используются МДП-транзисторы с диэлектриком SiO2 (МОП-транзисторы).

Анализ МОП-транзисторных логических элементов достаточно прост, т.к. из-за отсутствия входных токов их можно рассматривать отдельно от других элементов даже при работе в цепочке.

На рис. 20 показаны два варианта построения логических элементов на МОП-транзисторах с n‑каналами.

а б

а б

Рис. 20. Логические элементы на МОП-транзисторах: а) – элемент ИЛИ-НЕ , б) – элемент И-НЕ

Транзисторы Т3 выполняют роль нагрузки.

Логические уровни в обеих схемах не зависят от нагрузки и соответствуют выходным напряжениям открытого и закрытого ключа:

![]() .

.

Соответственно, логический перепад составляет:

![]() .

.

Напряжение питания Ec МОП-логики выбирают в 3…4 раза больше порогового напряжения Uo открывания транзисторов. Если Uo = 1,5 … 3В, то получаемый логический перепад в 5 … 10В намного превышает значения, свойственные схемам И2 Л, ЭСЛ и даже ТТЛ (при напряжении питания 4 … 5В). Поэтому МОП-логика обладает повышенной помехоустойчивостью.

Более высоким быстродействием и низким энергопотреблением характеризуется логика на комплементарных транзисторах вследствие причин, рассмотренных ранее. По принципу действия и схемотехнике КМОП-логика очень близка МОП-логике.

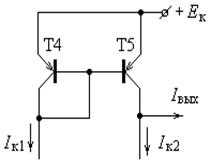

Эмиттерно-связанная логика (ЭСЛ)

В основе схемы ЭСЛ лежит переключатель тока, в одно из плеч которого включено параллельно несколько транзисторов. Эти транзисторы равноправны – отпирание любого из них (или всех вместе) приводит к изменению логического состояния переключателя. Поэтому ЭСЛ-элементы выполняют логическую функцию ИЛИ-НЕ .

Вследствие ненасыщенного режима работы транзисторов логический перепад в схеме не превышает 0,65В.

3.2 Параметры интегральныхлогических элементов

Независимо от принадлежности к той или иной серии, все логические элементы характеризуются определенным одним и тем же набором параметров, которые являются справочными данными. Значения же этих параметров обусловлены схемотехническим конструктивным и технологическим исполнением элементов.

Значения параметров, как правило, задаются с запасом и не исчерпывают физических возможностей микросхемы, однако превышать их не следует.

Оценивают микросхемы по следующим основным параметрам:

быстродействию, напряжению питания, потребляемой мощности, коэффициенту разветвления по выходу, коэффициенту объединения по входу, помехоустойчивости, энергии переключения, надежности, стойкости к климатическим и механическим воздействиям. Рассмотрим основные из них.

Уровни выходных напряжений

Техническими условиями для каждой серии логических элементов задаются наибольший и наименьший уровни выходных напряжений, соответствующих логическим единице и нулю при допустимых изменениях напряжения питания, нагрузки, температуры. Напряжение

U1 вых min соответствует минимальному уровню логической единицы на выходе (для ТТЛ U1 вых min = 2,4В), а напряжение U0 вых max – максимальному уровню логического нуля (для ТТЛ U0 вых max = 0,4В).

Статическая помехоустойчивость

Этот параметр определяет допустимое напряжение помех на входах микросхемы и оценивается для низкого и высокого уровней напряжения.

Статической помехоустойчивостью по низкому уровню считают разность

![]() ,

,

где U0 вых max – максимальное допустимое напряжение низкого уровня на выходе нагруженной микросхемы;

U0 вх max – максимальное допустимое напряжение низкого уровня на входе нагружающей микросхемы.

Помехоустойчивость по высокому уровню определяют так:

![]() ;

;

здесь U1 вых min – минимальное напряжение высокого уровня на выходе нагруженной микросхемы; U1 вх min – минимальное допустимое напряжение высокого уровня на нагружающем входе.

ТТЛ, например, логика еще будет нормально работать, если на ее входе напряжение логического нуля достигнет 0,8В, а напряжение логической единицы снизится до 2В. Таким образом, гарантированный запас помехоустойчивости в обоих состояниях составляет 0,4В. Реальный же запас помехоустойчивости гораздо больше и превышает 1В.

Коэффициент разветвления по выходу

Этот параметр Кр аз (нагрузочная способность) определяет максимальное число входов элементов данной серии, которым можно нагружать выходы микросхемы без нарушения ее нормального функционирования.

Коэффициент объединения по входу

Коб определяет число логических входов, которые имеет логический элемент.

Простейшие логические элементы выпускаются с 2, 3, 4 и 8 входами. Более сложные устройства содержат и другие входы: адресные, установочные, разрешающие, входы синхронизации и др.

Входные токи

Эти параметры определяют нагрузку, которую представляет рассматриваемая схема, на предшествующую схему или другой источник сигнала. Различают входные токи I0 вх и I1 вх при подаче логических нуля или единицы.

Средняя статическая потребляемая мощность

Определяется следующим образом:

,

,

где P0 пот и P1 пот – мощности, потребляемые интегральным логическим элементом в состоянии логического нуля и логической единицы.Это вытекает из того, что в сложных многоэлементных устройствах в среднем половина логических элементов находится в состоянии 1, а половина – в состоянии 0.

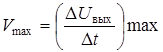

Быстродействие

Характеризуется максимальной частотой смены входных сигналов, при которой еще не нарушается нормальное функционирование устройства.

Инерционность полупроводниковых приборов и паразитные емкости служат причиной того, что каждое переключение сопровождается переходными процессами, отчего фронты импульсов растягиваются.

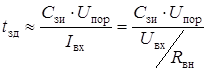

Для оценки временных свойств микросхем обычно пользуются задержкой распространения сигнала, которая представляет собой интервал времени между входным и выходным импульсами, измеренными на уровне 0,5. Задержки распространения сигнала при включении t1,0 зд.р. и при выключении t0,1 зд.р. не равны, поэтому пользуются усредненным параметром tзд.р. ср. = 0,5(t1,0 зд.р. + t0,1 зд.р. ).

Для последовательностных устройств (триггеры, счетчики и др.) вводятся некоторые дополнительные временные параметры, обусловленные принципом действия: разрешающее время, длительность входного импульса и др.

В общем случае анализ физических, технологических и схемотехнических особенностей интегральных логических элементов показывает, что можно создать различные их варианты, но их особенностью будут либо относительно высокое (высокое) быстродействие при низкой экономичности, либо высокая экономичность при относительно низком (низком) быстродействии. Обобщенные характеристики известных типов интегральных логических элементов приведены в таблице 3.

Таблица 3

| Тип логики | Pст. ср. , мВт |

tзд.р. ср. , нс |

Uпом , В |

Kоб | Kраз |

ТТЛ ТТЛШ |

1 – 20 | 5 – 20 2 – 10 |

0,8 – 1 0,5 – 0,8 |

2 – 8 | 10 – 30 10 – 40 |

| ЭСЛ | 20 – 50 | 0,5 – 2 | 0,2 – 0,3 | 2 – 8 | 1 – 20 |

| И2 Л | 0,01 – 0,1 | 10 – 100 | 0,02 – 0,05 | 1 | 3 – 5 |

МОП КМОП |

1 – 10 0,01 – 0,1 |

20 – 200 10 – 50 |

2 – 3 1 – 2 |

2 – 8 | 10 – 20 |

Как видно из таблицы, наиболее быстродействующими являются в настоящее время схемы ЭСЛ и ТТЛШ, наиболее экономичными – схемы И2 Л и КМОП.

4. МИКРОЭЛЕКТРОННЫЕ ФУНКЦИОНАЛЬНЫЕ ЦИФРОВЫЕ УЗЛЫ КОМБИНАЦИОННОГО ТИПА

Интегральные логические элементы являются основой для построения цифровых устройств, выполняющих более сложные операции и относящихся к классу комбинационных устройств.

Основные из них: дешифраторы и шифраторы; мультиплексоры и демультиплексоры; двоичные сумматоры; цифровые компараторы и мажоритарные элементы; преобразователи кодов и др.

СУММАТОРЫ

Сумматорами называются цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие – запоминающие результаты вычислений при снятии входных сигналов.

В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС.

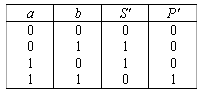

Сумматор по модулю два. Это устройство с двумя входами (а и b), на выходе у которого сигнал «1» появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. «0» и «1». Сумматор не обладает памятью, а его таблица истинности и логическое уравнение имеют вид:

![]()

![]()

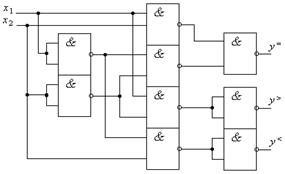

Название «по модулю два» этот сумматор получил потому, что yсоответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

![]()

aб

Рис. 21. Реализация сумматора по модулю два:

а – принципиальная схема; б – функциональная схема

Полусумматор. Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b. Так как при a= 1 и b= 1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого – сигнал переноса. Таблица истинности полусумматора и его логические уравнения имеют вид:

![]()

P' = ab

Реализация полусумматора в базисе И–НЕ представлена на рис. 22

а б

Рис. 22. Схема полусумматора:

а – реализация в базисе И–НЕ ; б – условное обозначение

Условное обозначение полусумматора на схемах – HS(halfsum– полусумма), а полного сумматора – SM.

Полный сумматор. Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c – сигнал переноса из предыдущего младшего разряда. Имеет два выхода S(сумма) и Р (перенос). Полный сумматор можно построить из двух полусумматоров (рис. 23), отсюда и название – полусумматор, используя следующие логические уравнения

![]()

![]()

Рис. 23. Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел.

В цифровой схемотехнике операцию вычитания обычно заменяют сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, поэтому вычитатели могут быть выполнены на основе сумматоров.

Дешифраторы, шифраторы, преобразователи кодов

Дешифратор. Комбинационное устройство, позволяющее преобразовать n-разрядный двоичный код в позиционный 2n -разрядный код. Имеет nвходов и 2n или меньше выходов. В зависимости от входного набора сигнал 1 появится только на одном определенном выходе, а на всех остальных выходах будут сигналы 0.

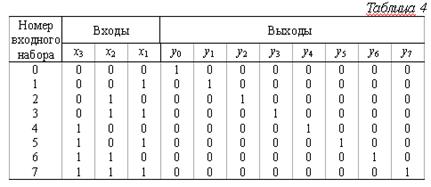

Таблица истинности полного дешифратора на три входа имеет вид (табл.4):

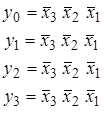

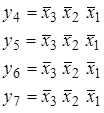

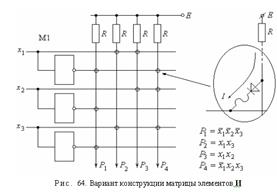

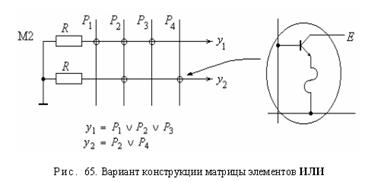

Логические функции выходов дешифратора:

По способу реализации дешифраторы могут быть линейные, прямоугольные и пирамидальные.

Более совершенными являются пирамидальные дешифраторы, относящиеся к многоступенчатым структурам и содержащие ряд логических элементов для выделения общих частей функций.

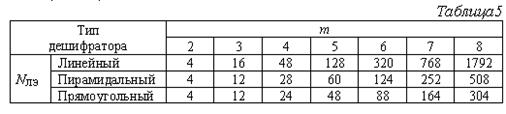

В ниже следующей таблице дана сравнительная оценка линейных, пирамидальных и прямоугольных дешифраторов по аппаратным затратам NЛЭ в пересчете на 2-входные ЛЭ для m-разрядного входного кода (табл. 5).

Как видно из таблицы 5, преимущества многоступенчатых дешифраторов заметно нарастают с увеличением m. В специализированных ИС тем не менее предпочтение часто отдают более простым линейным (одноступенчатым) дешифраторам, обладающим к тому же повышенным быстродействием.

Шифратор. Комбинационное устройство, преобразующее управляющий сигнал на одном из входов в соответствующий двоичный код.

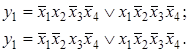

Для шифратора на четыре входа и два выхода, например, логические уравнения в ДНФ, полученные из таблицы, будут следующими:

![]()

Наибольшее применение шифраторы находят в цифровых устройствах ввода информации с пультов управления для преобразования десятичных чисел в двоичный код. При нажатии на клавишу на один их входов шифратора подается логическая единица (на остальные – логические нули), на выходе формируется соответствующий двоичный код.

Условное обозначение дешифратора и шифратора приведено на рис. 24:

а б

Рис. 24. Условное обозначение:

а – дешифратор; б – шифратор

Преобразователи кодов. Это устройства для автоматического изменения по заданному алгоритму соответствия между входным и выходным кодами без изменения их смыслового содержания.

По другому, преобразователь кода представляет собой устройство с mвходами и nвыходами, взаимно и однозначно преобразующее входные слова из некоторого алфавита {X1 , X2 , …, Xp } и выходные слова другого алфавита {Y1 , Y2 , …, Yu }.

Задача преобразования кодов возникает прежде всего в связи с необходимостью сведения цифровых устройств с разнообразными способами кодирования в единую систему.

Для преобразования параллельных двоичных кодов можно построить достаточно простые преобразователи на комбинационных логических схемах. Однако на практике это часто осуществляется алгоритмическим путем, используя запоминающие устройства.

Мультиплексоры, демультиплексоры

Демультиплексоры (распределители). Устройства, передающие сигнал, поступивший на его вход x, на один из Sвыходов в зависимости от управляющего сигнала (УС), заданного двоичным кодом.

Структура демультиплексора имеет вид (рис. 25):

Рис.25. Структура демультиплексора

Демультиплексоры по своей логике работы близки к дешифраторам. Если на вход xподать логическую единицу, то показанный на рис. 25 демультиплексор превращается в дешифратор. Поэтому некоторые промышленно выпускаемые дешифраторы могут выполнять функции демультиплексоров.

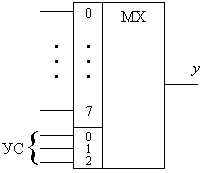

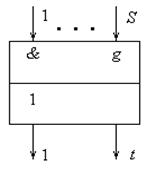

Мультиплексор. Устройство для коммутации информации, поступающей по нескольким входным каналам, на один выходной канал в зависимости от управляющего сигнала, заданного двоичным кодом.

Рис. 26. Условное обозначение мультиплексора

Если мультиплексор имеет n-разрядный управляющий сигнал, то количество коммутируемых входов – 2n (рис. 26).

Цифровые компараторы

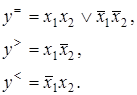

Компаратором называется устройство сравнения кодов чисел. В общем случае компаратор параллельных кодов двух m-разрядных двоичных чисел представляет собой комбинационную схему с 2mвходами и тремя выходами («равно», «больше», «меньше»). При поступлении на входы кодов двух сравниваемых чисел сигнал логической единицы появляется только на одном из выходов. В некоторых случаях компаратор может иметь менее трех выходов.

Одноразрядный компаратор имеет два входа на которые одновременно поступают одноразрядные двоичные числа x1 и x2 , и три выхода (=, >, <).

Из таблицы истинности логические уравнения компаратора при сравнении x1 с x2 получаются в виде

![]()

Реализация такого компаратора в базисе И–НЕ приводит к следующей схеме (рис. 27):

Многоразрядные компараторы обычно выполняют на базе одноразрядных. При этом используется принцип последовательного сравнения разрядов многоразрядных чисел, начиная с их старших разрядов, так как уже на этом этапе, если x1 m ¹ x2 m , задача может быть решена однозначно, и сравнение следующих за старшими разрядов не потребуется.

Рис. 27. Одноразрядный компаратор двоичных чисел

5. интегральные ТРИГГЕРЫ

Триггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое.

Можно выделить две основные области их применения: формирование импульсов и работу в качестве элементарных автоматов цифровых устройств.

Как формирователи, триггеры позволяют получать стандартные по амплитуде прямоугольные импульсы с малой длительностью фронта и среза, практически не зависящей от скорости изменения управляющего сигнала. В роли цифровых автоматов с двумя внутренними состояниями различные типы триггеров выполняют функции ячеек памяти, каскадов задержки, пересеченных ячеек и т. д.

Триггер, как элементарный конечный автомат, характеризуется следующими свойствами:

·число внутренних состояний – два (единица и нуль), что соответствует одной внутренней переменной, обозначаемой для триггеров буквой Q;

·число выходных переменных y – одно, значение переменной y совпадает со значением Q;

·число входных переменных xзависит от типа триггера.

Наряду с выходом Q, называемым прямым, триггер имеет и инверсный выход ![]() . Состояние триггера определяется значением его прямого выхода.

. Состояние триггера определяется значением его прямого выхода.

Все известные на сегодняшний день триггеры по функциональному признаку можно разделить на четыре основных типа:

·RS-триггеры – триггеры с двумя установочными входами;

·D-триггеры – триггеры задержки с одним входом;

·Т-триггеры с одним счетным входом;

·универсальные триггеры с несколькими входами.

Как и любые цифровые автоматы, триггеры могут быть асинхронными и синхронными.

Различают также триггеры со статическими и динамическими входами. Входы, управляемые потенциальными (уровнями напряжений), называются статическими (включая и сигнал синхронизации).

Причем, если триггер переключается сигналами логической единицы, то его называют триггером с прямым управлением, в противном случае – триггером с инверсным управлением.

Входы же управляемые перепадами потенциалов называют динамическими.

5.1 RS -триггер

Асинхронный RS -триггер

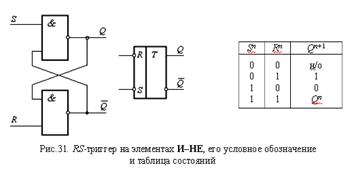

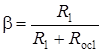

В простейшем исполнении триггер это симметричная структура из двух логических элементов ИЛИ–НЕ либо И–НЕ , охваченных перекрестной положительной обратной связью. Схема триггера на элементах ИЛИ–НЕ и его условное обозначение приведены на рис. 28.

Рис. 28. Асинхронный RS -триггер на элементах ИЛИ–НЕ :а – логическая структура; б – условное обозначение

Этот триггер (бистабильная ячейка) обладает двумя устойчивыми состояниями, которые обеспечиваются за счет связи выхода каждого элемента с одним из входов другого. Свободные входы служат для управления и называются информацион-ными или логическими. Одному из выходов присвоено наименование прямого, его обозначают буквой Q, а другому – наименование инверсного и обозначают ![]() .

.

Вход, по которому триггер устанавливается в единичное состояние (Q= 1, ![]() = 0), называют входом S(от английского Set – установка), а в нулевое (Q = 0,

= 0), называют входом S(от английского Set – установка), а в нулевое (Q = 0, ![]() = 1) – входом R (reset – возврат).

= 1) – входом R (reset – возврат).

Работа триггера характеризуется таблицей переходов состояний (табл. 6), из которой следует, что на двух наборах переменных его состояние не определено. Карта Карно для нахождения логической функции переходов RS-триггера приведена на рис. 29.

Таблица 6

| Такт tn | Такт tn+1 | ||

| Rn | Sn | Qn | Qn+1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 0 0 0 1 1 1 1 |

0 1 0 – 1 1 0 – |

Доопределив ее единицами на запрещенных наборах и применив правила минимизации получим

![]() .

.

Возможны следующие состояния триггера, в зависимости от комбинации входных сигналов:

·Rn , Rn = 0, сигнал на выходе может быть Qn+1 = 1 или Qn+1 = 0, что соответствует нейтральному состоянию (режим хранения информации);

·Sn = 1, Rn = 0, Qn+1 = 1 – установка триггера в единичное состояние;

·Sn = 0, Rn = 1, Qn+1 = 0 – установка в нулевое состояние;

·Sn = 1, Rn = 1 – состояние не определено. Если затем входная комбинация станет Sn = 0, Rn = 0, то триггер с равной вероятностью может установиться или в нулевое, или в единичное состояние, поэтому входная комбинация Sn = 1, Rn = 1 недопустима.

Минимизированная таблица состояний RS-триггера и его временная диаграмма имеют вид (рис. 30):

При синтезе устройств на триггерах возникает задача определения требуемых входных комбинаций для перехода триггера из одного (заданного) состояния Qn в другое (требуемое) Qn+1 .

Эту задачу удобно решать с помощью таблицы, называемой матрицей переходов.

Рассмотрим функцию переходов для всех возможных изменений выхода триггера Qn ® Qn+1 :

0 ® 0; 0 ® 1; 1 ® 0; 1 ® 1.

С учетом этого, получим систему уравнений

![]()

![]()

![]()

![]() .

.

Результаты анализа этих уравнений позволяют составить матрицу переходов RS-триггера (табл. 7), показывающую сочетания входных сигналов, которые обеспечивают требуемое состояние триггера при его переходе из такта nв такт (n+ 1). Если RS-триггер выполнить на элементах И–НЕ , то получим схему, приведенную на рис. 31.

Такой вариант триггера называют ![]() -триггером или RS-триггером с инверсным управлением.

-триггером или RS-триггером с инверсным управлением.

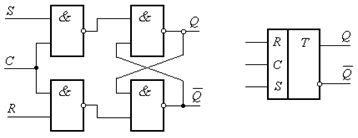

Синхронный RS -триггер . Известно, что из-за задержек переключения логических элементов могут возникнуть ложные состояния. Устранить это помогает временное стробирование. Временное стробирование обеспечивается синхронизирующими (тактовыми) импульсами, поэтому синхронный RS-триггер кроме информационных входов Rи Sимеется вход C, на который подается синхронизирующий сигнал (рис. 32).

Такой триггер функционирует как RS-триггер только при условии наличия синхронизирующих импульсов. В противном случае, т.е. при отсутствии синхронизирующих импульсов, состояние его сохраняется неизменным Qn+1 = Qn , какие бы сигналы ни подавались на информационные входы, причем возможна подача сочетания R=S=1 (или R=S=0 для триггера с инверсными входами).

Рис.32. Синхронный RS-триггер с прямыми статическими входами на элементах И-НЕ и его условное обозначение

Специфика синхронных триггеров со статическим управлением по входу синхронизации такова, что в течение времени действия тактового импульса смена сигналов на информационных входах вызывает новые срабатывания. Следовательно, синхронные триггеры со статическим управлением при активном состоянии тактового входа ведут себя подобно асинхронным. Во многих случаях это свойство является недостатком, так как может оказаться причиной сбоев в цифровых устройствах.

От этого свободны триггеры с динамическим и двух ступенчатым управлением. Триггеры с динамическим управлением в зависимости от схемы исполнения реагируют на перепад напряжения от нуля к единице, либо от единицы к нулю. Таким образом, сигналы, поступающие на динамический вход, воспринимаются только в те моменты времени, когда их состояние изменяется определенным образом.

На рис. 33. приведено условное обозначение синхронных RS-триггеров с динамическими входами синхронизации.

Двухступенчатые триггеры содержат первую ступень для промежуточной записи входной информации и вторую – для последующего запоминания и хранения. У двухступенчатых триггеров формирование нового состояния происходит за два такта, поэтому их иногда называют двухтактными.

Функциональные свойства всей триггерной системы определяются первой ступенью, вторая ступень обычно представляет собой синхронный RS-триггер со статическим управлением.

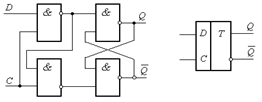

5.2 D -триггер

Функциональная особенность триггеров этого типа состоит в том, что сигнал на выходе Qв такте (n+1) равен значению сигнала на входе Dв предыдущем такте n. Другими словами, D-триггер задерживает на один такт информацию, существовавшую на входе D. Триггер принял свое название от первой буквы английского слова delay– задержка. Логическое уравнение D-триггера имеет вид:

![]() .

.

Асинхронный D-триггер не применяется, так как его выход просто повторяет входной сигнал после окончания переходного процесса, поэтому все реальные D-триггеры тактируемые и функционируют в соответствии с табл. 8. Смена состояний триггера происходит под действием тактового импульса (С=1), т. е. хранение информации в D-триггере обеспечивается цепями синхронизации. Управление по тактовому входу может быть статическим, динамическим, а также двухступенчатым.

Матрица переходов D-триггера приведена в (табл. 9)

Структурная логическая схема простейшего D-триггера со статическими входами и его условное обозначение представлены на рис.34.

а б

Рис.34. Пример D-триггера со статическим управлением уровнем С = 1 – а и его обозначение – б

5.3. T -триггер

Триггер Т -типа, или счетный триггер, имеет один информационный Т-вход. Смена его состояний происходит всякий раз, когда входной сигнал меняет свое значение в определенном направлении. В зависимости от того, какой перепад напряжения используется для управления (от нуля к единице или от единицы к нулю), различают Т-триггеры с прямым или инверсным динамическим управлением (![]() -триггер).

-триггер).

По способу ввода входной информации Т-триггеры могут быть асинхронными и синхронными.

Управление Т-триггера имеет вид

![]() .

.

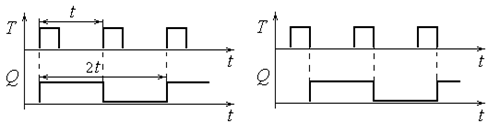

Порядок смены состояний Т и ![]() -триггеров приведен в табл. 10, а их временная диаграмма работы на рис. 35.

-триггеров приведен в табл. 10, а их временная диаграмма работы на рис. 35.

Особенностью Т-триггера явля-ется в два раза меньшая часто-та выходных сигналов по срав-нению с частотой сигналов на входе. Это позволяет использо-вать его в качестве делителя частоты последовательности импульсов на два, а также при создании двоичных счетчиков.

а б

Рис. 35. Таблица состояний Т-триггеров и временные диаграммы их работы: а – Т-триггера; б – ![]() -триггера

-триггера

Счетные триггеры как самостоятельные микроэлектронные изделия не выпускаются промышленно, так как их легко получить из других типов триггеров, например из D-триггеров (рис. 36).

Счетные триггеры со стати-ческим управлением во время действия входного импульса проявляют склонность к генера-ции, и практической реализации не нашли.

5.4 JK -триггер

Функциональная особенность JK-триггеров состоит в том, что при всех входных комбинациях, кроме одной ![]() , они действуют подобно RS-триггеру, причем вход Jиграет роль входа S, а K-вход соответствует R-входу. При входной комбинации

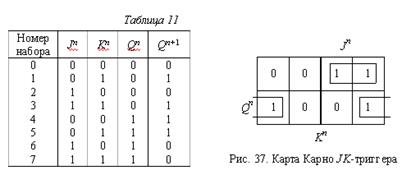

, они действуют подобно RS-триггеру, причем вход Jиграет роль входа S, а K-вход соответствует R-входу. При входной комбинации ![]() в каждом такте выходной сигнал меняет свое значение на противоположное. JK-триггеры не имеют неопределенных состояний. Таблица переходов состояний триггера имеет вид (табл. 11)

в каждом такте выходной сигнал меняет свое значение на противоположное. JK-триггеры не имеют неопределенных состояний. Таблица переходов состояний триггера имеет вид (табл. 11)

Используя карту Карно (рис. 37) найдем минимальную форму уравнения триггера.

![]() .

.

Для составления матрицы переходов JK-триггера подставим в полученное уравнение все возможные сочетания состояний триггера

0![]() 00=

00=![]() , при любом Kи J=0,

, при любом Kи J=0,

0![]() 11=

11=![]() , при любом Kи J=1.

, при любом Kи J=1.

1![]() 00=

00=![]() , при любом Jи K=1,

, при любом Jи K=1,

1![]() 11=

11=![]() , при любом Jи K=0.

, при любом Jи K=0.

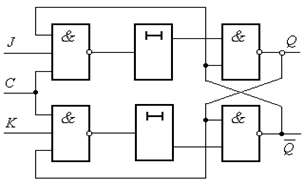

Откуда следует матрица переходов (табл. 12), которую используют при синтезе цифровых устройств на JK-триггерах. В схемном отношении JK-триггер отличается от триггеров RS-типа наличием обратных связей. Логическая структура простейшего JK-триггера показана на рис. 38.

Элементы временной задержки в данной схеме играют роль стабилизаторов состояний триггера, и непосредственно на его функциональные свойства не влияют.

В интегральной схемотехнике применяются только синхронные JK-триггеры в силу жестких требований к длительности входных сигналов для асинхронного варианта.

Рис. 38. Логическая структура JK-триггера

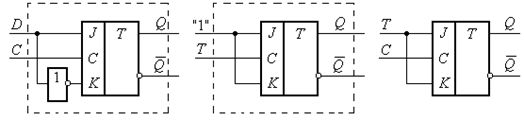

JK-триггеры относятся к универсальным устройствам. Их универсальность имеет двойственный характер. Во-первых, эти триггеры с равным успехом могут быть использованы в счетчиках, регистрах, делителях частоты и других электронных узлах, во-вторых, путем определенного соединения выводов они легко обращаются в триггеры других типов.

Если, например, принять J=Dи K=![]() , то уравнение JK-триггера примет вид:

, то уравнение JK-триггера примет вид:

![]() ,

,

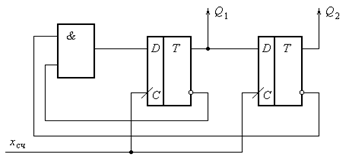

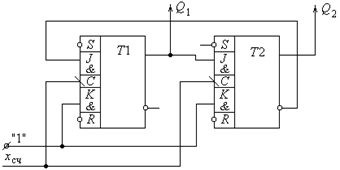

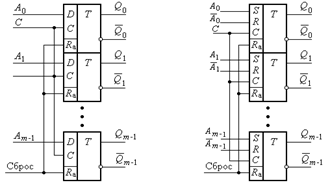

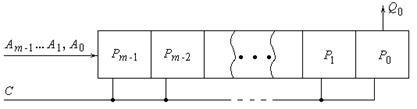

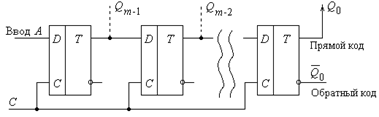

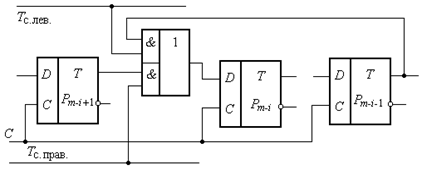

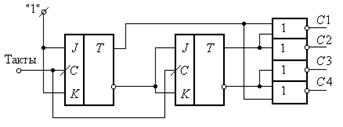

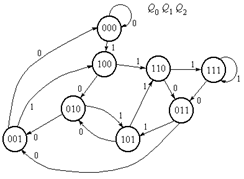

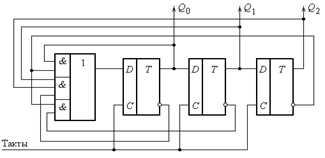

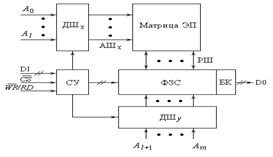

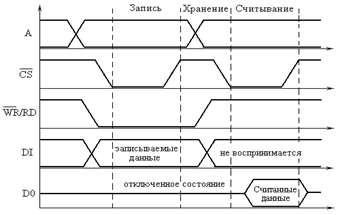

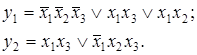

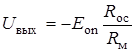

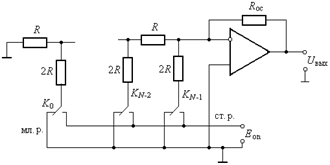

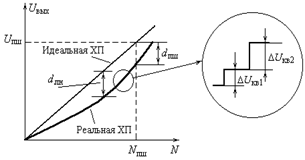

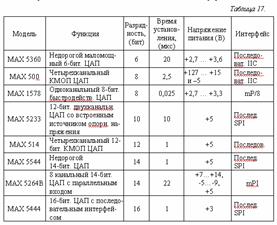

что соответствует логическому уравнению D-триггера.