| Скачать .docx |

Реферат: Модулі оперативної пам’яті SD-RAM, DDR, DDR2, DIMM

Міністерство освіти і науки України

Національний університет водного господарства і природокористування

Кафедра електротехніки і автоматики

Індивідуальне навчально-дослідне завдання

з курсу

Комп’ютерна техніка і організація обчислювальних робіт”

на тему:

“Організація роботи оперативної пам`яті DIMM DDR2 SDRAM”

Виконав:

студент ФПМіКІС

спеціальності АУТП

Полюхович Микола

Рівне-2008

Мікросхеми динамічної пам'яті є згрупованим масивом конденсаторів - матрицею, що складається з рядків (rows) і стовпців (columns). Для перетворення аналогової величини заряду, накопиченої в конденсаторах, використовуються спеціальні підсилювачі. Крім цього, передбачені спеціальні ланцюги для заряджання конденсаторів і для запису даних.

Щоб прочитати інформацію, записану в комірці, спочатку подається сигнал Row Access Strobe (RAS), виконуючи який ми потрапляємо на потрібний рядок. При цьому заряди всього рядка поступають на підсилювачі і через деякий час можуть бути зчитані. Така операція називається активацією рядка.

Далі, отримуючи команду Column Access Strobe (CAS), ми виходимо на шукану комірку рядка. Після цього при отриманні команди Read відбувається зчитування інформації, а при директиві Write - її запис. Поки рядок залишається активним, можливі зчитування або запис і інших елементів пам'яті. При читанні інформації з комірок у конденсаторів втрачається заряд, тому їх необхідно періодично підзаряджати. Ця операція відбувається після того, як закінчується час активності рядка. Після її закриття подальше зчитування даних неможливе без повторної активації.

Елемент пам'яті через свої фізичні можливості здатний зберігати тільки один біт інформації. Для зберігання 1 байта використовується 8 елементарних елементів пам'яті. При цьому вони адресуються однаково і організовані з використанням шини даних шириною в 8 ліній. Такі об'єднані комірки утворюють слово.

Для прискорення процесу зчитування даних з різних ділянок пам'яті використовується технологія з декількома масивами, або банками пам'яті. Їх можна уявити собі як книгу, що складається з деякого числа сторінок-матриць. Банки працюють абсолютно незалежно один від одного. Наприклад, дані можна прочитувати з пам'яті одного, обробляти і закладати в пам'ять іншого. При цьому будуть відсутні затримки на активацію і закриття рядків даних в масиві пам'яті, що спостерігалося б у разі одного банку. Подібна архітектура значно прискорює процес доступу до даних. Контролер пам'яті при зверненні використовує номер банку, номер рядка і номер колонки масиву пам'яті. Тобто, маючи номер банку, RAS і CAS, цей чіп знає точні координати потрібного йому елементу пам'яті.

Природно, що на кожну операцію зчитування даних з пам'яті потрібний час. Тут ми стикаємося з так званими таймінгами, або затримками, які характеризують швидкодію модуля і вимірюються в тактах або наносекундах.

Після видачі команди RAS для вибору потрібного рядка потрібний час на її активацію, який зазвичай складає 2-5 тактів. Дану затримку прийнято називати Ras-to-cas Delay (RCD). Після цього очікування контролер пам'яті ініціалізує команду вибору стовпця і після часу, рівного затримці CAS, прочитує дані. Цей параметр прийнято називати CAS Latency (CL), на практиці він зазвичай так само варіюється від 2 до 5 тактів. Після отримання інформації відбувається відновлення заряду на прочитаних комірках вибраного рядка, на що потрібний час, рівний RAS Precharge (RP). Ще один важливий параметр - це RAS Active to Precharge Delay (TRAS), який означає кількість тактів, протягом яких рядок повинен бути активним, перш ніж буде видана команда на заряджання.

Всі ці величини впливають в першу чергу на так звану латентність пам'яті, тобто на сумарний час очікування процесором передачі даних, що знаходяться в оперативній пам'яті. Латентність вимірюється в тактах або в наносекундах, як і таймінги.

Очевидно, що чим менша затримки, тим нижча і латентність, тим швидше відбувається робота з пам'яттю, тим більше загальна продуктивність комп`ютера. Проте надмірне зниження таймінгів може спричинити за собою нестабільність роботи системи.

Продуктивність залежить не тільки від латентності, оскільки часто здійснюється пакетна передача даних, при якій вплив затримок не так відчутно. Тут основну роль грає інший параметр, що характеризує кількість даних, які пам'ять здатна передавати (читати або записувати) за одиницю часу. Він називається пропускною здатністю пам'яті (ПЗП). Зрозуміло, що чим більше ПЗП, тим краще даний модуль. У виробників є два шляхи поліпшення цього параметра: збільшення розрядності шини і підвищення тактової частоти. Перший спричиняє за собою більше число провідних контактів, що значно ускладнює розводку друкарських плат і вимагає серйозних матеріальних вкладень. Другий шлях менш ресурсоємний, і саме з його допомогою виробники пам'яті добиваються кращих результатів. Дані про ПЗП різних типів модулів DDR2 приведені в таблиці:

| Тип пам'яті | DDR2-400 | DDR2-533 | DDR2-600 | DDR2-667 | DDR2-675 | DDR2-800 | DDR2-900 | DDR2-1000 |

| Специфікація пам'яті | PC3200 | PC4300 | PC4800 | PC5300 | PC5400 | PC6400 | PC7200 | PC8000 |

| Тактова частота, МГц | 200 | 267 | 300 | 333 | 338 | 400 | 450 | 500 |

| Ефективна частота, МГц | 400 | 533 | 600 | 667 | 675 | 800 | 900 | 1000 |

| ПЗП в одноканальному режимі, Гбайт/с | 3,2 | 4,3 | 4,8 | 5,3 | 5,4 | 6,4 | 7,2 | 8,0 |

| ПЗП в двоканальному режимі, Гбайт/с | 6,4 | 8,6 | 9,6 | 10,6 | 10,8 | 12,8 | 14,4 | 16,0 |

DDR - абревіатура, що говорить про подвійну швидкість передачі даних. Раніше широко застосовувалася пам'ять SDR (Single Data Rate), яка за один такт передає рівно одну порцію інформації. DDR встигає зробити удвічі більше, оскільки пересилає дані двічі - по обох фронтах тактового імпульсу. Прискорення передачі у пам'яті DDR2 відносно DDR пов'язане з підвищенням тактової частоти буферів вводу-виводу і існує в умовах мультиплексування. Тобто контролер-мультиплексор прочитує дані відразу з 4 банків пам'яті. Таким чином, в модулях DDR2 SDRAM в порівнянні з DDR SDRAM застосована технологія збільшення продуктивності за рахунок підвищення тактової частоти при збереженні робочих частот самих мікросхем і тієї ж розрядності шини даних.

Добиваючись прискорення за рахунок яких-небудь внутрішніх ресурсів, ми, як часто це відбувається, в чомусь програємо. Згаданий вище метод збільшення продуктивності стає причиною підвищення латентності. Це пояснюється, по-перше, наявністю схеми мультиплексування і, по-друге, невисокими тактовими частотами самих чіпів пам'яті.

Крім всього іншого, DDR2 SDRAM випускається в корпусах FBGA, які дозволяють поліпшити частотні характеристики, а також підвищити ступінь тепловіддачі. У конструкції модулів застосована схема On-die-termination. Подібні технології дозволяють також збільшити і об'єм модулів пам'яті.

Інформація про організацію, розмір і допустимі можливості пам'яті міститься в розташованому на модулі спеціальному чіпі - SPD (Serial Presence Detect). Вона зчитується BIOS для автоматичного завантаження оптимальних настройок ОЗУ. Тим самим, коли ви вперше заходите в BIOS Setup, то всі параметри, пов'язані з пам'яттю, які ви виявите, будуть узяті з SPD. Змінюючи їх в розумних межах, можна спробувати "розігнати" пам'ять шляхом збільшення частоти або зменшення таймінгів.

Найбільш пріоритетним напрямом розвитку технології оперативної пам'яті DDR SDRAM вже який рік підряд є подальше збільшення її пропускної спроможності (безпосередньо залежною від її тактової частоти) і зниження затримок. На другому місці по важливості, мабуть, розташовується зменшення її енергоспоживання і, нарешті, збільшення ємкості окремих компонентів (мікросхем) і модулів пам'яті в цілому. Мабуть, реалізація першого напряму вважається найбільш важливою, у зв'язку з чим відбувається практично безперервно, тоді як реалізація останніх з перерахованих вище завдань, як правило, вимагає певного еволюційного стрибка в технологічному розвитку (наприклад, переходу від технології DDR до технології DDR2). Дійсно, просте збільшення частоти шини пам'яті позначається на її енергоспоживанні явно не позитивним чином, тому для вирішення завдання зниження енергоспоживання потрібні інші підходи. Більш того, ситуація, як правило, ускладнюється тим, що рішення цієї задачі в певній мірі протирічить «генеральній лінії» розвитку технологій пам'яті, яка, нагадаємо, полягає в досягненні все більшої пропускної здатності (частоти) і все менших затримок. І справді, добре відомо, що перші варіанти пам'яті типу DDR2 відчутно програвали їх «рівночастотним» аналогам типу DDR по затримках. Проте, необмежене зростання частот (і зниження затримок) в рамках однієї і тієї ж технології пам'яті неможливе - воно обмежене цілком певними фізичними причинами (перш за все, тепловиділенням), тому «еволюційні стрибки» в розвитку технологій пам'яті все ж таки необхідні.

Так йшла справа при першому еволюційному стрибку в розвитку технологій пам'яті DDR SDRAM - переході від DDR до DDR2. Перші зразки DDR функціонували на частоті всього 100 Мгц (і мали рейтинг DDR-200), потім частота поступово збільшилася до 200 Мгц (DDR-400). Відбувалося одночасне зменшення затримок. Потім з'явилися і більш високочастотні модулі пам'яті DDR (аж до 300 Мгц, тобто DDR-600), проте офіційно вони так і не були прийняті стандартом JEDEC. Збільшення частоти модулів пам'яті, або зниження затримок вимагало підвищення напруги живлення із стандартного рівня 2.5 В до значень порядку 2.85 В, проблема надмірного тепловиділення вирішувалася, як правило, застосуванням звичайних тепловідводів.

Коли подальше збільшення тактових частот пам'яті DDR виявилося практично неможливим, на ринку оперативної пам'яті з'явилося нове, друге покоління пам'яті DDR SDRAM - пам'ять DDR2, яка поступово почала доводити свою конкурентоспроможність і поволі, але впевнено витісняти «старе» покоління пам'яті DDR. Первинні варіанти DDR2 були представлені частотами 200 Мгц (DDR2-400) і 266 Мгц (DDR2-533) - так би мовити, DDR2 почала свій розвиток там, де закінчила свій розвиток DDR. Більш того, первинний стандарт DDR2 передбачав набагато більш високочастотні варіанти, в порівнянні із звичною DDR - 333-мгц модулі типу DDR2-667 і 400-мгц варіант DDR2-800. При цьому мікросхеми DDR2 були засновані на новому технологічному процесі, що дозволяє використовувати напругу живлення всього 1.8 В (що було одним з чинників зниження їх енергоспоживання) і досягати вищих ємкостей компонентів і, отже, модулів пам'яті.

Завдяки чому вдалося досягти (спочатку - в теорії, а потім - і на практиці) великих тактових частот (а отже, і пропускної здатності) пам'яті DDR2 при одночасному зменшенні її енергоспоживання, в порівнянні з DDR? Чи були при цьому у DDR2 тільки одні переваги перед DDR, чи були і недоліки? Щоб відповісти на ці питання, дозволимо собі зробити короткий екскурс в теорію. Спершу, розглянемо гранично спрощену схему функціонування пам'яті типу DDR (мал. 1).

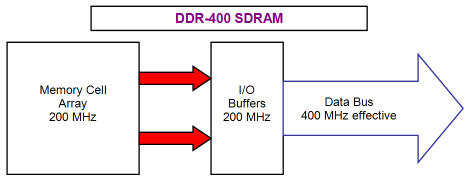

Мал. 1. Схематичне зображення передачі даних в мікросхемі пам'ятіDDR-400

Передача даних від мікросхем пам'яті модуля до контролера пам'яті по зовнішній шині даних здійснюється по обох напівперіодах синхросигнала (висхідному - «фронту», і низхідному - «зрізу»). У цьому і полягає суть технології «Double Data Rate», саме тому «ефективна» частота пам'яті DDR завжди є подвоєною (наприклад, DDR-400 при 200-мгц частоті зовнішньої шини даних). Отже, «ефективна» частота зовнішньої шини даних пам'яті DDR-400 складає 400 Мгц, тоді як її дійсна частота, або частота буферів введення-виводу, складає 200 Мгц. У пристроях пам'яті першого покоління DDR внутрішня частота функціонування мікросхем пам'яті прирівняна до дійсної частоти зовнішньої шини (частоті буферів вводу-виводу) і складає 200 Мгц для даної мікросхеми пам'яті DDR-400. При цьому абсолютно очевидно, що для того, щоб передавати по 1 біту даних за такт (по кожній лінії даних) по зовнішній шині з «ефективною» частотою 400 Мгц, за один такт внутрішньої 200-мгц шини даних необхідно передати 2 біта даних. Іншими словами, можна сказати, що за інших рівних умов внутрішня шина даних повинна бути удвічі ширше в порівнянні із зовнішньою шиною даних. Така схема доступу до даних називається схемою «2n-передвибірки» (2n-prefetch).

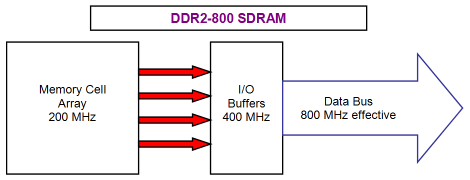

Мал. 2. Схематичне зображення передачі даних в мікросхемі пам'ятіDDR2-800

Найбільш природним чином вирішення проблеми досягнення вищих тактових частот при переході від DDR до DDR2 є зниження тактової частоти внутрішньої шини даних удвічі по відношенню до реальної тактової частоти зовнішньої шини даних (частоті буферів введення-виводу). Так, в даному прикладі мікросхем пам'яті DDR2-800 (мал. 2) частота буферів введення-виводу складає 400 Мгц, а «ефективна» частота зовнішньої шини даних - 800 Мгц (оскільки суть технології Double Data Rate залишається в силі - дані як і раніше передаються як по висхідному, так і по низхідному напівперіоді синхросигналу). При цьому частота внутрішньої шини даних складає всього 200 Мгц, тому для передачі 1 біта (по кожній лінії даних) за такт зовнішньої шини даних з ефективною частотою 800 Мгц на кожному такті 200-мгц внутрішньої шини даних потрібно передати вже 4 бітів даних. Іншими словами, внутрішня шина даних мікросхеми пам'яті DDR2 повинна бути в 4 рази ширше в порівнянні з її зовнішньою шиною. Така схема доступу до даним, реалізована в DDR2, називається схемою «4n-передвибірки» (4n-prefetch). Її переваги перед схемою 2n-prefetch, реалізованою в DDR, очевидні. З одного боку, для досягнення рівної пікової пропускної спроможності можна використовувати удвічі меншу внутрішню частоту мікросхем пам'яті (200 Мгц для DDR-400 і всього 100 Мгц для DDR2-400, що дозволяє значно понизити енергоспоживання). З іншого боку, при рівній внутрішній частоті функціонування мікросхем DDR і DDR2 (200 Мгц як для DDR-400, так і DDR2-800) останні характеризуватимуться удвічі більшою теоретичною пропускною спроможністю. Але очевидні і недоліки - функціонування мікросхем DDR2 на удвічі меншій частоті (в умовах рівності теоретичної пропускної спроможності пристроїв DDR і DDR2) і використання складнішої схеми перетворення «4-1» приводить до відчутного зростання затримок, що і спостерігалося на практиці в ході дослідження перших зразків модулів пам'яті DDR2.

Подальший розвиток технології пам'яті DDR2 з'явився істотно аналогічним розвитку її попереднього покоління, пам'яті DDR. А саме, були досягнуті частоти в 333 і 400 Мгц (тобто реалізовані офіційні стандарти DDR2-667 і DDR2-800). Були значно понижені затримки, навіть офіційно з'явилася нова версія стандарту JEDEC (Jesd79-2b), що допускає зниження схеми таймінгів від 4-4-4 до 3-3-3, - для DDR2-533, від 5-5-5 до 4-4-4 - для DDR2-667, від 6-6-6 до 5-5-5 і навіть 4-4-4 - для DDR2-800. Звичайно ж, услід з'явилися і «нестандартні» різновиди DDR2, що по своїй частоті виходять далеко за межі специфікації JEDEC - аж до 625 Мгц («DDR2-1250») при схемі таймінгів 5-5-5, або «стандартні» DDR2-800, але з екстремально низькими схемами таймінгів на зразок 3-3-3. Як і раніше, для досягнення таких рекордів було потрібно значне підняття живлячої напруги модулів із стандартного рівня 1.8 В до екстремально високих рівнів порядка 2.4 В (що зовсім трохи поступається стандартному значенню попереднього покоління пам'яті DDR - 2.5 В). Зрозуміло, це потребувало застосування складніших способів відведення тепла від мікросхем пам'яті - як оригінальних, патентованих фірмових конструкцій тепловідводів, так і застосування зовнішнього активного охолоджування.

Проте, як і у випадку з минулим поколінням пам'яті DDR, на сьогоднішній день межа технології пам'яті DDR2 (по частоті, затримках і значно збільшеному тепловиділенню внаслідок значного збільшення живлячої напруги) практично досягнута. Тому вже сьогодні цілком закономірно чекати черговий «еволюційний стрибок» технології пам'яті DDR SDRAM - перехід від пам'яті стандарту DDR2 до нового стандарту DDR3.

Мал. 3. Схематичне зображення передачі даних в мікросхемі пам'ятіDDR3-1600

Неважко здогадатися, що основний принцип, який лежить в основі переходу від DDR2 до DDR3, в точності повторює розглянуту вище ідею, закладену при переході від DDR до DDR2. А саме, DDR3 - це все та ж DDR SDRAM, тобто передача даних як і раніше здійснюється по обох напівперіодах синхросигнала на подвоєній «ефективній» частоті щодо власної частоти шини пам'яті. Тільки рейтинги продуктивності зросли в 2 рази, в порівнянні з DDR2 - типовими швидкісними категоріями пам'яті нового стандарту DDR3 будуть різновиди від DDR3-800 до DDR3-1600 (а можливо, і вище). Чергове збільшення теоретичної пропускної спроможності компонентів пам'яті в 2 рази знов пов'язане із зниженням їх внутрішньої частоти функціонування в стільки ж раз. Тому відтепер, для досягнення темпу передачі даних із швидкістю 1 біт/такт по кожній лінії зовнішньої шини даних з «ефективною» частотою в 1600 Мгц (як в прикладі, розглянутому на мал. 3 використовувані мікросхеми 200 Мгц повинні передавати по 8 біт даних за кожен такт. Тобто ширина внутрішньої шини даних мікросхем пам'яті опиниться вже в 8 разів більше в порівнянні з шириною їх зовнішньої шини. Очевидно, така схема передачі даних з розглянутим перетворенням типу «8-1» називатиметься схемою «8n-передвибірки» (8n-prefetch). Переваги при переході від DDR2 до DDR3 будуть тими ж, що і при переході, що відбувся раніше, від DDR до DDR2: з одного боку, це зниження енергоспоживання компонентів в умовах рівності їх пікової пропускної спроможності (DDR3-800 проти DDR2-800), з іншого боку - можливість подальшого нарощування тактової частоти і теоретичної пропускної спроможності при збереженні колишнього рівня «внутрішньої» частоти компонентів (DDR3-1600 проти DDR2-800). Тими ж будуть і недоліки - подальший розрив між «внутрішньою» і «зовнішньою» частотою шин компонентів пам'яті приводитиме до ще більших затримок. Відносне збільшення останніх, при переході від DDR2 до рівночастотної DDR3, буде приблизно таким же, як і при переході від DDR до рівночастотної DDR2.

Що ж, перейдемо до дещо детальнішого розгляду нового покоління мікросхем і модулів пам'яті DDR3, що прийшли на зміну DDR2.

Стандарт DDR3 на сьогоднішній день ще не прийнятий JEDEC, його ухвалення очікується ближче до середини поточного року (імовірно, він носитиме ім'я Jesd79-3). Тому представлена нижче інформація про мікросхеми і модулі пам'яті DDR3 поки що носить попередній характер.

Почнемо з мікросхем пам'яті DDR3, перші прототипи яких були оголошені ще в 2005 році. Доступні сьогодні зразки мікросхем DDR3 засновані на 90-нм технологічному процесі і характеризуються рівнем живлячої напруги 1.5 В, що само по собі вносить приблизно 30% внесок в зниження потужності, що розсіюється цими мікросхемами пам'яті в порівнянні з мікросхемами DDR2 (що мають стандартну напругу живлення 1.8 В). Повне зниження енергоспоживання в порівнянні з рівночастотної DDR2 досягає приблизно 40%, що особливо важливе для мобільних систем. Ємкості компонентів, передбачені попередніми специфікаціями JEDEC, варіюються від 512 Мбіт до 8 Гбіт, тоді як типові мікросхеми, що випускаються на сьогодні, мають ємкість від 1 до 4 Гбіт. Теоретична пропускна спроможність мікросхем DDR3 удвічі вище в порівнянні з DDR2 завдяки використанню розглянутої вище схеми 8n-prefetch (проти 4n-prefetch в DDR2). Кількість логічних банків в мікросхемах DDR3 також збільшена удвічі в порівнянні з типовим значенням для DDR2 (4 банки) і складає 8 банків, що теоретично дозволяє збільшити «паралелізм» при зверненні до даних по схемі чергування логічних банків і приховати затримки, пов'язані із зверненням до одного і того ж рядка пам'яті. Мікросхеми DDR3 монтуються в FBGA-упаковку, що володіє рядом покращень в порівнянні з DDR2, а саме:

•Великою кількістю контактів живлення і заземлення;

•Вдосконаленим розподілом живлячих і сигнальних контактів, що дозволяє досягти кращої якості електричного сигналу (необхідне для стійкішого функціонування при високих частотах);

•Повним заповненням масиву, що збільшує механічну міцність компоненту.

Перейдемо до розгляду модулів пам'яті DDR3. Як і модулі пам'яті DDR2, вони випускаються у вигляді 240-контактної друкарської плати (по 120 контактів з кожного боку модуля), проте не є електрично сумісними з останніми, і з цієї причини мають інше розташування «ключа» (див. мал. 5а).

Мал. 5а. Зовнішній вигляд типових модулів пам'яті DDR3 (зверху) і DDR2 (знизу)

Мал. 5б. Зовнішній вигляд типових роз'ємів на системній платі (комбо) для установки модулів пам'яті DDR3 (голубий/рожевий) і DDR2 (зелений/оранжевий)

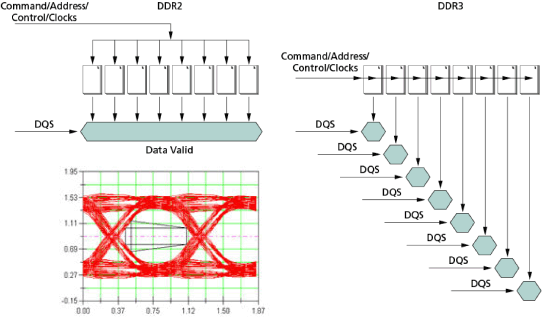

Відмінною особливістю дизайну схемотехніки модулів пам'яті DDR3 є застосування fly-by архітектури передачі адрес і команд, а також сигналів управління і тактової частоти окремих мікросхем модуля пам'яті. Схематично ця архітектура представлена на мал. 6. Вона дозволяє добитися збільшення якості передачі сигналів, що необхідне при функціонуванні компонентів при високих частотах, типових для пам'яті DDR3 і не потрібний для компонентів пам'яті стандарту DDR2.

Мал. 6. fly-by архітектура передачі сигналів в модулях пам'яті DDR3

Відмінність між способом передачі адрес і команд, сигналів управління і тактової частоти в модулях пам'яті DDR2 і DDR3 (на прикладі модулів, фізичний банк яких складений з 8 мікросхем розрядністю x8) представлено на мал. 7. У модулях пам'яті DDR2 подача адрес і команд здійснюється паралельно на всі мікросхеми модуля, у зв'язку з чим, наприклад, при зчитуванні даних, всі вісім 8-бітних елементів даних виявляться доступними в один і той же момент часу (після подачі відповідних команд і закінчення відповідних затримок) і контролер пам'яті зможе одночасно прочитати всі 64 біти даних. В той же час, в модулях пам'яті DDR3 внаслідок застосування fly-by архітектури подачі адрес і команд кожна з мікросхем модуля отримує команди і адреси з певним відставанням щодо попередньої мікросхеми, тому елементи даних, відповідні певній мікросхемі, також виявляться доступними з деяким відставанням щодо елементів даних, відповідних попередній мікросхемі в ряду, що становить фізичний банк модуля пам'яті. У зв'язку з цим, з метою мінімізації затримок, в модулях пам'яті DDR3, в порівнянні з модулями DDR2, реалізований декілька інший підхід до взаємодії контролера пам'яті з шиною даних модуля пам'яті. Він називається «регулюванням рівня зчитування/запису» (read/write leveling) і дозволяє контролеру пам'яті використовувати певний зсув за часом при прийомі/передачі даних, відповідне «запізнюванню» надходження адрес і команд (а отже, і даних) в певну мікросхему модуля. Цим досягається одночасність зчитування (запису) даних з мікросхем (у мікросхеми) модуля пам'яті.

Мал. 7. Регулювання рівня зчитування/запису (read/write leveling) в модулях пам'яті DDR3

На закінчення, розглянемо швидкісні характеристики передбачуваних специфікацій модулів пам'яті DDR3, які представлені в таблиці 2.

| Тип модулів | Рейтинг | Частота шини, МГц | Типова схема таймінгів | Теоретична пропускна спроможність, Гб/с |

|

| Одно-канальний режим | Дво-канальний режим | ||||

| DDR3-800 | PC3-6400 | 400 | 6-6-6-18 | 6.40 | 12.80 |

| DDR3-1066 | PC3-8500 | 533 | 7-7-7-21 | 8.53 | 17.07 |

| DDR3-1333 | PC3-10667 | 667 | 8-8-8-24 | 10.67 | 21.33 |

| DDR3-1600 | PC3-12800 | 800 | 9-9-9-27 | 12.80 | 25.60 |

| DDR3-1866 | PC3-14900 | 933 | 10-10-10-30 | 14.93 | 29.87 |

Табл. 2. Швидкісні характеристики модулів пам'яті DDR3

Рейтинг продуктивності модулів пам'яті DDR3 має значення виду «Pc3-x», де X означає пропускну спроможність модуля в одноканальному режимі, виражену в МБ/С. Оскільки модулі пам'яті DDR3 мають ту ж розрядність, що і модулі пам'яті DDR2 - 64 біта, чисельні значення рейтингів рівночастотних модулів пам'яті DDR2 і DDR3 співпадають (наприклад, Pc2-6400 для DDR2-800 і Pc3-6400 для DDR3-800).

Новинки

Компанія Samsung нещодавно повідомила, що почала пробні постачання 2-гігабітних мікросхем DDR-3, що випускаються по 50 нм технології. Крім збільшення щільності зберігання інформації, вони забезпечують на 40% нижче енергоспоживання в порівнянні з існуючими мікросхемами.

о теперішнього часу 2-гигабітная щільність досягалася розміщенням двох мікросхем пам'яті в одній упаковці. Тепер можна задовольнятися однією мікросхемою. На базі нових чіпів DDR-3 можна створювати модулі пам'яті об'ємом 4 Гб у виконанні DIMM і SO-DIMM, а також регістрові модулі пам'яті об'ємом до 8 Гб. Крім того, при використанні двочіпової компоновки об'єм такої пам'яті можна збільшити до 16 Гб на модуль.

Дані мікросхеми працюють на швидкостях до DDR3-1333 при напрузі 1.35-1.5 В. Масове виробництво цих мікросхем буде запущено до кінця поточного року. По оцінках аналітиків, до 2011 року мікросхеми пам'яті типу DDR-3 досягнуть частки ринку в 72%, причому кожна третя з них буде двогігабітною.

Наступним світовим досягненням з неприхованою гордістю поділилася з громадськістю прес-служба компанії Super Talent Technology Corporation. На цей раз виробник заявив про випуск першого в індустрії 4-гігабайтного двохканального набору пам'яті DDR3 PC3-14400, що поповнив популярну продуктову лінію ProjectX.

Згідно обнародуваної інформації, даний комплект складається з пари ретельно протестованих планок на базі високоякісних DRAM-чіпів від Micron, кожна з яких має схему організації 256Mx64, функціонує на частоті 1800 Мгц із затримками 8-8-8-24, характеризується напругою живлення 1,9 В і обладнана фірмовим алюмінієвим радіатором для підтримки оптимального температурного режиму. Крім того, наголошується, що продукт спеціально оптимізований для ефективного використання в материнських платах, заснованих на типовому наборі мікросхем NVIDIA nForce 790i Ultra SLIі. Продукт забезпечується довічною гарантією якості.

В асортименті копанії Apacer Technology з`явилися модулі пам'яті серії Aeolus - 240-контактні новинки типу DDR3-1800 і DDR3-1600, пропоновані в наборах з пари планок загальним об'ємом 2 Гб, кожна з яких обладнана, як затверджується, унікальною по дизайну системою активного охолоджування, запатентованої конструкції, що складається з особливого двошарового радіатора, зі встановленим над ним мініатюрним вентилятором. Як особливо підкреслюється в опублікованому офіційному прес-релізі, новинки орієнтовані в першу чергу на завзятих любителів сучасних 3D-игр, а також тих користувачів, хто вважає за краще піддавати свої комп'ютерні системи екстремальному розгону. При цьому рішення виготовлені за передовою технологією компанії Micron, мають схему організації 128Mx8, функціонують із затримками CL7-7-7-20 і характеризуються робочою напругою живлення 1,9 В (DDR3-1800) і 1,8 В (DDR3-1600). Крім того, наголошується, що на всі вироби розповсюджується довічна гарантія.

Німецька компанія Qimonda AG оголосила про поповнення продуктивної лінії оперативної пам'яті XTUNE DDR3-1600 новими модулями об'ємом 1 Гб, які поступлять в продаж під маркою Aeneon. Анонс супроводжується заявою прес-служби про підтримку недавно представленої платформи nForce 790i SLI . Наголошується, що комбінація оперативної пам'яті Qimonda і першої DDR3-сумісної системної логіки NVIDIA надає ентузіастам розгону і вимогливим любителям 3D-игр широких можливостей для досягнення найвищих результатів. Однієї з особливостей нової пам'яті Aeneon XTUNE DDR3-1600 є готовність до роботи при номінальній для стандарту DDR3 напрузі живлення 1,5 В, на відміну від більшості конкуруючих продуктів, розрахованих на 1,6-1,8 В. Розробники заявляють про здатність добре розганятись без підвищення напруги, що, безумовно, зменшує енергоспоживання і тепловиділення чіпів пам'яті при роботі в позаштатному режимі. Більш того, знижуються вимоги до охолодження і росте стабільність системи в цілому. Представлені модулі володіють підтримкою технології EPP 2 (Enhanced Performance Profile 2), призначеній значно спростити процес розгону і збільшити його ефективність. Нагадаємо, що профілі EPP є прописані в SPD-чіпи - додаткові параметри, які дозволяють без зайвих операцій з настройками BIOS добитися максимальної продуктивності підсистеми пам'яті. На думку розробників, повністю розкрити можливості EPP другого покоління допоможе нова платформа NVIDIA nForce 790i SLI. Оперативна пам'ять Aeneon XTUNE DDR3-1600 представлена в двохканальних комплектах загальним об'ємом 2 Гб (2 x 1 Гб). У виробничих умовах модулі ретельно тестуються на сумісність і стабільність на шині 1600 Мгц із затримками CL9 при напрузі живлення 1,5 В.

Про випуск нових високошвидкісних 240-контактних DIMM-модулів пам'яті CrucialBallistix Unbuffered Non-ECC DDR3-2000 (PC3-16000) для найвимогливіших геймерів і комп'ютерних ентузіастів на днях повідомила компанія Lexar Media .Як вказується в опублікованому прес-релізі, новинки відносяться до продуктів категорії NVIDIA SLI Ready, підтримують EPP 2.0. Спеціально призначені для ефективного використання в могутніх ігрових платформах на базі недавно офіційно представленого чіпсета NVIDIA nForce 790i Ultra SLI. При цьому кожна планка має схему організації 128Mx64, функціонують на частоті 2000 Мгц із затримками 9-9-9-28, характеризується робочою напругою живлення 1,9 В і обладнана фірмовим жовтим пасивним радіатором. Вироби вже зараз доступні для придбання.

В асортименті компанії Corsair, що спеціалізується на високопродуктивній оперативній пам'яті і продуктах з використанням флеш-пам'яті, з'явилися модулі пам'яті DDR3, що працюють на частоті 2 ГГц. Новинка призначена для ігрової платформи NVIDIA 790i Ultra SLI.Поява пам'яті DDR3 у асортименті компанії стала результатом тісної співпраці між NVIDIA і Corsair. Як затверджується, в ході спільної роботи було виявлений, що платформа NVIDIA 790i Ultra SLI показує особливі можливості розгону, зв'язані із застосуванням архітектури пам'яті DDR3. Всі модулі пам'яті Corsair, що одержали сертифікат SLI-Ready, підтримують технологію EPP2, що дозволяє автоматично встановити оптимальні тимчасові параметри у разі роботи спільно з 790i Ultra SLI. Компанія вже почала постачання двох наборів об'ємом по 2 ГБ сімейства DOMINATOR (TW3X2G2000 і TW3X2G1800) і одного набору такого ж об'єму сімейства XMS DHX (TW3X2G1600). У всіх новинках використовується технологія DHX, суть якої полягає в застосуванні чотиришарової конструкції радіатора, що дозволяє поліпшити відведення тепла, і, як наслідок, підвищити продуктивність і надійність пам'яті.

Компанія OCZ анонсувала модулі пам'яті OCZ DDR3 PC3-14400 Platinum 2 GB. Вони працюють на частоті 1,8 GHz. Для охолоджування набору використовуються теплорозсіювачі. Параметри таймінгів на сайті заявлені як 8-8-8-24. Компанія OCZ наділила ці модулі довічною гарантією. До речі, ще наголошується їх оптимізація для роботи з материнськими платами від ASUS.

Література:

1. http://www.3dnews.ru

2. http://www.hardwareportal.ru

3. http://www.wikipedia.org

4. http://intuit.ru

5. http://www.ixbt.com

6. http://testblock1.j043.mt.ru