| Скачать .docx |

Реферат: Параллельный интерфейс: LPT-порт

Порт параллельного интерфейса был введен в PC для подключения принтера —LP'T-порт (Line PrinTer — построчный принтер).

Адаптер параллельного интерфейса представляет собой набор регистров, расположенных в пространстве ввода/вывода. Регистры порта адресуются относительно базового адреса порта, стандартными значениями которого являются 386h, 378h и 278h. Порт имеет внешнюю 8-битную шину данных, 5-битную шину сигналов состояния и 4-битную шину управляющих сигналов.

BIOS поддерживает до четырех LPT-портов (LPT1-LPT4) своим сервисом — прерыванием INT 17h, обеспечивающим через них связь с принтерами по интерфейсу Centronics. Этим сервисом BIOS осуществляет вывод символа, инициализацию интерфейса и принтера, а также опрос состояния принтера.

Интерфейс Centronics

Понятие Centronics относится как к набору сигналов и протоколу взаимодействия, так и к 36-контактному разъему, устанавливаемому на принтерах. Назначение сигналов приведено в табл. 1.

Таблица 1.

Сигналы интерфейса Centronics

| Сигнал |

I/O* |

Контакт |

Назначение |

| Strobe |

I |

1 |

Строб данных. Данные фиксируются по низкому уровню сигнала |

| Data [0:7] |

I |

2-9 |

Линии данных. Data 0 (контакт 2) — младший бит |

| Actt |

0 |

10 |

Acknowledge — импульс подтверждения приема байта (запрос на прием следующего). Может использоваться для формирования запроса прерывания |

| Busy |

0 |

11 |

Занято. Прием данных возможен только при низком уровне сигнала |

| PaperEnd |

0 |

12 |

Высокий уровень сигнализирует о конце бумаги |

| Select |

0 |

13 |

Сигнализирует о включении принтера |

| Auto LF# |

I |

14 |

Автоматический перевод строки. |

| Еггогй |

0 |

32 |

Ошибка: конец бумаги, состояние OFF-Line или внутренняя ошибка принтера |

| Imt# |

I |

31 |

Инициализация |

| Slot In# |

I |

36 |

Выбор принтера (низким уровнем). При высоком уровне принтер не воспринимает остальные сигналы интерфейса |

| GND |

- |

19-30 33 |

Общий провод интерфейса |

| * I/O |

Задает |

Направление |

(вход/выход) применительно к принтеру. |

Интерфейс Centronics поддерживается большинством принтеров с параллельным интерфейсом, его отечественным аналогом является интерфейс ИРПР-М.

Традиционный LPT-порт

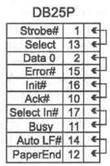

Традиционный порт SPP (Standard Parallel Port) является однонаправленным портом, на базе которого программно реализуется протокол обмена Centronics. Порт обеспечивает возможность вырабатывания запроса аппаратного прерывания по импульсу на входе АСК#. Сигналы порта выводятся на разъем DB-25S (розетка), установленный непосредственно на плате адаптера (или системной плате) или соединяемый с ней плоским шлейфом. Название и назначение сигналов разъема порта (табл. 2) соответствуют интерфейсу Centronics.

Таблица 2.

Разъем стандартного LPT-порта

| Контакт DB-25S |

Провод шлейфа |

Назначение |

||

| I/O* |

Reg.Bit** |

Сигнал |

||

| 1 |

1 |

0/1 |

CR: 0\ |

Strobe# |

| 2 |

3 |

0(1) |

DR:0 |

Data 0 |

| 3 |

5 |

0(1) |

DR: 1 |

Data 1 |

| 4 |

7 |

0(1) |

DR: 2 |

Data 2 |

| 5 |

9 |

0(1) |

DR:3 |

Data 3 |

| 6 |

11 |

0(1) |

DR: 4 |

Data 4 |

| 7 |

13 |

0(1) |

DR:5 |

Data 5 |

| 8 |

15 |

0(1) |

DR:6 |

Data 6 |

| 9 |

17 |

0(1) |

DR:7 |

Data 7 |

| 10 |

19 |

I |

SR: 6 |

Ack# |

| 11 |

21 |

I |

SR: 7\ |

Busy |

| 12 |

23 |

I |

SR: 5 |

PaperEnd |

| 13 |

25 |

I |

SR: 4 |

Select |

| 14 |

2 |

0/1 |

CR: 1\ |

Auto LF# |

| 15 |

4 |

I |

SR: 3 |

Error# |

| 16 |

6 |

0/1 |

CR: 2 |

Init# |

| 17 |

8 |

0/1 |

CR:3\ |

Select In# |

| 18-25 |

10, 12, 14, 16 |

18, 20, 22, 24, 26 |

- |

- |

* I/O задает направление передачи (вход/выход) сигнала порта; 0/I обозначает выходные линии, состояние которых считывается при чтении из соответствующих портов вывода.

** Символом «\» отмечены инвертированные сигналы (1 в регистре соответствует низкому уровню линии).

*** Вход Ack# соединен резистором (10 кОм) с питанием +5 В.

Стандартный порт имеет три 8-битных регистра, расположенных по соседним адресам в пространстве ввода/вывода, начиная с базового адреса порта (BASE).

Data Register (DR) — регистр данных, адрес= BASE. Данные, записанные в этот порт, выводятся на выходные линии интерфейса. Данные, считанные из этого регистра, в зависимости от схемотехники адаптера соответствуют либо ранее записанным данным, либо сигналам на тех же линиях.

Status Register (SR) — регистр состояния, представляющий собой 5-битный порт ввода сигналов состояния принтера (биты SR.4-SR.7), адрес= BASE+1. Бит SR.7 инвертируется — низкому уровню сигнала соответствует единичное значению бита в регистре, и наоборот.

Назначение бит регистра состояния (в скобках даны номера контактов разъема):

SR.7—Busy — инверсные отображения состояния линии Busy (11);

SR.6 —АСК (Acknowledge) — отображения состояния линии Ack# (10).

SR.5 —РЕ (Paper End) — отображения состояния линии Paper End (12).

SR.4—Select — отображения состояния линии Select (13). Единичное значение соответствует cигналу о включении принтера.

SR.3—Error — отображения состояния линии Error (15).

SR.2 — PIRQ — флаг прерывания по сигналу Ack# (только для порта PS/2). Бит обнуляется, если сигнал Ack# вызвал аппаратное прерывание. Единичное значение устанавливается по аппаратному сбросу и после чтения регистра состояния.

SR[1:0] — зарезервированы.

Control Register (CR) — регистр управления, адрес=ВА5Е+2. Как и регистр данных, этот 4-битный порт вывода допускает запись и чтение (биты 0-3), но его выходной буфер обычно имеет тип открытый коллектор. Это позволяет более корректно использовать линии данного регистра как входные при программировании их в высокий уровень. Биты О, 1, 3 инвертируются — единичному значению в регистре соответствует низкий уровень сигнала, и наоборот.

Назначение бит регистра управления:

CR[7:6] — зарезервированы.

CR.5 — Direction — бит управления направлением передачи (только для портов PS/2). Запись единицы переводит порт данных в режим ввода.

CR.4 —ACKINTEN (Ack Interrupt Enable) — единичное значение разрешает прерывание по спаду сигнала на линии Ackff — сигнал запроса следующего байта.

CR.3 — Select In — единичное значение бита соответствует низкому уровню на выходе Selecting (17) — сигналу, разрешающему работу принтера по интерфейсу Centronics.

CR.2 — Init — нулевое значение бита соответствует низкому уровню на выходе Imt# (16) — сигнал аппаратного сброса принтера.

CR.1 — Auto LF — единичное значение бита соответствует низкому уровню на выходе Auto LF# (14) — сигналу на автоматический перевод строки (LF — Line Feed) по приему байта возврата каретки (CR — Carriage Return).

CR.O —Strobe — единичное значение бита соответствует низкому уровню на выходе Strobeff (1) — сигналу стробирования выходных данных.

Запрос аппаратного прерывания (обычно IRQ7 или IRQ5) вырабатывается по отрицательному перепаду сигнала на выводе 10 разъема интерфейса (АСК#) при установке CR.4=1. Прерывание вырабатывается, когда принтер подтверждает прием предыдущего байта.

Процедура вывода байта по интерфейсу Centronics через стандартный порт включает следующие шаги (в скобках приведено требуемое количество шинных операций процессора):

Вывод байта в регистр данных (1 цикл IOWR#).

Ввод из регистра состояния и проверка готовности устройства (бит SR.7 — сигнал BUSY).

По получении готовности выводом в регистр управления устанавливается строб данных, а следующим выводом строб снимается (2 цикла lOWRff).

Стандартный порт сильно асимметричен — при наличии 12 линий (и бит), нормально работающих на вывод, на ввод работает только 5 линий состояния. Если необходима симметричная двунаправленная связь, на всех стандартных портах работоспособен режим полубайтного обмена — Nibble Mode. В этом режиме, называемым также и Hewlett Packard Bitronics, одновременно передаются 4 бита данных, пятая линия используется для квитирования.

Функции BIOS для LPT-порта

BIOS обеспечивает поддержку LPT-порта, необходимую для организации вывода по интерфейсу Centronics.

В процессе начального тестирования POST BIOS проверяет наличие параллельных портов по адресам ЗВСЬ, 378h и 278h и помещает базовые адреса обнаруженных портов в ячейки BIOS DATA AREA 0:0408h, 040Ah, 040СП, 040ЕП. Эти ячейки хранят адреса портов с логическими именами LPT1-LPT4. В ячейки 0:0478, 0479, 047А, 047В заносятся константы, задающие выдержку тайм-аута для этих портов.

Поиск портов обычно ведется по базовому адресу. Если считанный байт совпал с записанным, считается, что найден LPT-порт, и его адрес помещают в ячейку BIOS DATA AREA. Адрес порта LPT4 BIOS самостоятельно установить не может, поскольку в списке стандартных адресов поиска имеются только три вышеуказанных.

Обнаруженные порты инициализируются — записью в регистр управления формируется и снимается сигнал Initff, после чего записывается значение 00h, соответствующее исходному состоянию сигналов интерфейса.

Программное прерывание BIOS I NT 17h обеспечивает следующие функции поддержки LPT-порта:

00h — вывод символа из регистра AL по протоколу Centronics. Данные помещаются в выходной регистр и после готовности принтера формируется строб.

01h — инициализаия интерфейса и принтера.

02h — опрос состояния принтера.

При вызове INT 17h номер функции задается в регистре АН, номер порта — в регистре DX (0 — LPT1, 1 — LPT2...). При возврате после любой функции регистр АН содержит код состояния — биты регистра состояния SR[7:3] (биты 6 и 3 инвертированы) и флаг тайм-аута в бите 0. Флаг тайм-аута устанавливается при неудачной попытке вывода символа.

Расширения параллельного порта

Недостатки стандартного порта частично устраняют новые типы портов, появившихся в компьютерах семейства PS/2.

Двунаправленный порт 1 (Typel parallel port) — интерфейс, введенный с PS/2. Такой порт кроме стандартного режима может работать в режиме ввода или двунаправленном. Протокол обмена формируется программно, а для указания направления передачи в регистр управления порта введен специальный бит: при CR.5=0 буфер данных работает на вывод, при CR.5=1 — на ввод.

Порт с прямым доступом к памяти (Type 3 DMA parallel port) применялся в PS/2 моделей 57, 90, 95. Этот тип был введен для повышения пропускной способности и разгрузки процессора при выводе на принтер. Программе, работающей с данным портом, требовалось только задать блок данных в памяти, подлежащих выводу, и вывод по протоколу Centronics производился без участия процессора.

Физический и электрический интерфейс

Стандарт IEEE 1284 определяет физические характеристики приемников и передатчиков сигналов.

К передатчикам предъявляются следующие требования:

Уровни сигналов без нагрузки не должны выходить за пределы -0,5... +5,5 В.

Уровни сигналов при токе нагрузки 14 мА должны быть не ниже +2,4 В для высокого уровня (voh) и не выше +0,4 В для низкого уровня (vol) на постоянном токе.

Выходной импеданс ro, измеренный на разъеме, должен составлять 50(±)5 Ом на уровне voh-vol. Для обеспечения заданного импеданса в некоторых случаях используют последовательные резисторы в выходных цепях передатчика. Согласование импеданса передатчика и кабеля снижает уровень импульсных помех.

Скорость нарастания (спада) импульса должна находиться в пределах 0,05-0,4 В/нс.

Требования к приемникам:

Допустимые пиковые значения сигналов -2,0...+7,0.

Пороги срабатывания должны быть не выше 2,0 В (vih) для высокого уровня и не ниже 0,8 В (vil) для низкого.

Приемник должен иметь гистерезис в пределах 0,2-1,2 В.

Входной ток микросхемы не должен превышать 20 мкА.

Входная емкость не должна превышать 50 пФ.

Стандарт IEEE 1284 определяет три типа используемых разъемов. Типы Л (DB-25) и В (Centronics-36) используются в традиционных кабелях подключения принтера, тип С — новый малогабаритный 36-контактный разъем.

Интерфейсные кабели, традиционно используемые для подключения принтеров, обычно имеют от 18 до 25 проводников, в зависимости от числа проводников цепи GND.

Стандарт IEEE 1284 регламентирует и свойства кабелей:

Все сигнальные линии должны быть перевитыми с отдельными обратными (общими) проводами.

Каждая пара должна иметь импеданс 62(±)6 Ом в частотном диапазоне 4-16 МГц.

Уровень перекрестных помех между парами не должен превышать 10%.

Кабель должен иметь экран (фольгу), покрывающий не менее 85% внешней поверхности. На концах кабеля экран должен быть окольцован и соединен с контактом разъема.

Кабели, удовлетворяющие этим требованиям, маркируются надписью IЕЕЕ Std 1284-1994 Compliant». Они могут иметь длину до 10 метров.

Режимы передачи данных

Стандарт IEEE 1284 определяет пять режимов обмена, один из которых полностью соответствует традиционному стандартному программно-управляемому выводу по протоколу Centronics. Остальные режимы используются для расширения функциональных возможностей и повышения производительности интерфейса. Стандарт определяет способ согласования режима, по которому программное обеспечение может определить режим, доступный и хосту (в нашем случае это PC), и периферийному устройству.

Режимы нестандартных портов, реализующих протокол обмена Centronics аппаратно («Fast Centronics, «Parallel Port FIFO Mode»), могут и не являться режимами IEE1284, несмотря на наличие в них черт ЕРР и ЕСР.

При описании режимов обмена фигурируют следующие понятия:

Хост — компьютер, обладающий параллельным портом.

ПУ — периферийное устройство, подключаемое к этому порту (им может оказаться и другой компьютер). обозначениях сигналов Ptr обозначает передающее периферийное устройство.

Прямой канал — канал вывода данных от хоста в ПУ.

Обратный канал канал ввода данных в хост из ПУ.

Полубайтный режим ввода — Nibble Mode

Режим полубайтного обмена является наиболее общим решением задачи двунаправленного обмена данными, поскольку может работать на всех стандартных (традиционных) портах. Все эти порты имеют 5 линий ввода состояния, используя которые периферийное устройство может посылать в PC байт тетрадами (nibble — полубайт, 4 бита) за два приема. Назначение сигналов порта приведено в табл 4.

Таблица 4.

Сигналы LPT-порта в полубайтном режиме ввода

| Контакт |

Сигнал SPP |

I/O |

Использование сигнала при приеме данных в Nibble Mode |

|

| 14 |

AUTOFEED# |

0 |

HostBusy — сигнал квитирования. Низкий уровень означает готовность к приему тетрады, высокий подтверждает прием тетрады |

|

| 17 |

SELECTIN» |

0 |

Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

|

| 10 |

АСК# |

' |

PtrClk. Низкий уровень означает действительность тетрады, переход в высокий — ответ на сигнал HostBusy |

|

| 11 |

BUSY |

I |

Прием бита данных 3, затем бита 7 |

|

| 12 |

РЕ |

I |

Прием бита данных 2, затем бита 6 |

|

| 13 |

SELECT |

I |

Прием бита данных 1, затем бита 5 |

|

| 15 |

ERRORS |

I |

Прием бита данных 0, затем бита 4 |

|

Прием байта данных в полубайтном режиме состоит из следующих фаз:

1. Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

2. ПУ в ответ помещает тетраду на входные линии состояния.

3. ПУ сигнализирует о действительности тетрады установкой низкого уровня на линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой тетрады.

5. ПУ отвечает установкой высокого уровня на линии PtrCLk.

6. Шаги 1-5 повторяются для второй тетрады.

Полубайтный режим работает на всех портах со скоростью обмена не выше 50 Кбайт/с . Его применяют в тех случаях, когда прием данных от устройства производится в небольших объемах (например, для связи с принтерами).

Двунаправленный байтный режим Byte Mode

Данный режим обеспечивает прием данных с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита CR.5=1. Как и в стандартном и в полубайтном режиме, данный режим является программно-управляемым — все сигналы квитирования анализируются и устанавливаются программным драйвером. Назначение сигналов порта приведено в табл. 5.

Таблица 5.

Сигналы LPT-порта в байтном режиме ввода/вывода

| Контакт |

Сигнал SPP |

Имя в Byte Mode |

I/O |

Описание |

| 1 |

STROBES |

HostClk |

0 |

Импульс (низкого уровня) подтверждает прием байта в конце каждого цикла |

| 14 |

AUTOFEED# |

HostBusy |

0 |

Сигнал квитирования. Низкий уровень означает готовность хоста принять байт, высокий уровень устанавливается по приему байта |

| 17 |

SELECT-IN» |

1284Active |

0 |

Высокий уровень указывает на обмен в режиме IEEE 1284. (В режиме SPP уровень низкий) |

| 16 |

INIT# |

INIT# |

0 |

Не используется, установлен высокий уровень |

| 10 |

АСКй |

Ptrtik |

Устанавливается в низкий уровень для индикации действительности данных на линиях DATA[7:0]. В низкий уровень устанавливается в ответ на сигнал HostBusy |

|

| 11 |

BUSY |

PtrBusy |

I |

Состояние занятости прямого канала |

| 12 |

РЕ |

AckDataReq* |

I |

Устанавливается ПУ для указания на наличие обратного канала передачи* |

| 13 |

SELECT |

Xflag* |

I |

Флаг расширяемости* |

| 15 |

ERRORS |

DataAvau#* |

I |

Устанавливается ПУ для указания на наличие обратного канала передачи* |

| 2-9 |

DATA[7:0] |

DATA[7:0] |

I/0 |

Двунаправленный (прямой и обратный) канал данных |

Прием байта данных в байтном режиме состоит из следующих фаз:

1. Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии DATA[7:0].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk.

6. Хост подтверждает прием байта импульсом HostClk.

7. Шаги 1-6 повторяются для каждого следующего байта.

Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако работать он может только на двунаправленных портах, которые применяются в основном лишь на малораспространенных машинах PS/2.

Режим ЕРР

Протокол ЕРР (Enhanced Parallel Port — улучшенный параллельный порт) предназначен для повышения производительности обмена по параллельному порту. ЕРР был реализован в чипсете Intel 386SL (микросхема 82360) и используется как дополнительный протокол параллельного порта.

Протокол ЕРР обеспечивает четыре типа циклов обмена:

Цикл записи данных.

Цикл чтения данных.

Цикл записи адреса.

Цикл чтения адреса.

Адресные циклы могут быть использованы для передачи адресной, канальной и управляющей информации. Циклы обмена данными явно отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение сигналов порта ЕРР и их связь с сигналами SPP приведены в табл. 6.

Таблица 6.

Сигналы LPT-порта в режиме ввода/вывода ЕРР

| Контакт |

Сигнал SPP |

Имя в ЕРР |

I/O |

Описание |

| 1 |

STROBE» |

WRITE» |

0 |

Низкий уровень — признак цикла записи, высокий — чтения |

| 14 |

AUTOFEEDff |

DATASTB# |

0 |

Строб данных. Низкий уровень устанавливается в циклах передачи данных |

| 17 |

SELECTING |

ADDRSTB# |

0 |

Строб адреса. Низкий уровень устанавливается в адресных циклах |

| 16 |

INIT# |

RESETS |

0 |

Сброс ПУ (низким уровнем) |

| Контакт |

Сигнал SPP |

Имя в ЕРР |

I/O |

Описание |

| 10 |

АСК# |

INTR# |

I |

Прерывание от ПУ |

| 11 |

BUSY |

WAIT» |

I |

Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий — разрешает завершение цикла (снятие строба) |

| 2-9 |

D[8:0] |

AD[8:0] |

I/O |

Двунаправленная шина адреса/данных |

| 12 |

РЕ |

AckDataReq* |

I |

Используется по усмотрению разработчика периферии |

| 13 |

SELECT |

Xflag* |

I |

Используется по усмотрению разработчика периферии |

| 15 |

ERROR |

DataAvaiW* |

I |

Используется по усмотрению разработчика периферии |

ЕРР-порт имеет расширенный набор регистров (табл. 7), который занимает в пространстве ввода/вывода 5-8 смежных байт.

Таблица 7.

Регистры ЕРР-порта

| Имя регистра |

Смещение |

Режим |

R/W |

Описание |

| SPP Data Port |

+0 |

SPP/EPP |

W |

Регистр данных стандартного порта |

| SPP Status Port |

+1 |

SPP/EPP |

R |

Регистр состояния стандартного порта |

| SPP Control Port |

+2 |

SPP/EPP |

W |

Регистр управления стандартного порта |

| EPP Address Port |

+3 |

EPP |

R/W |

Регистр адреса ЕРР. Чтение или запись в него генерирует связанный цикл чтения или записи адреса ЕРР |

| EPP Data Port |

+4 |

EPP |

R/W |

Регистр данных ЕРР. Чтение (запись) генерирует связанный цикл чтения (записи) данных ЕРР |

| Not Defined |

+5...+7 |

EPP |

N/A |

В некоторых контроллерах могут использоваться для 16-32-битных операций ввода/вывода |

В отличие от программно-управляемых режимов, описанных выше, внешние сигналы ЕРР-порта (как информационные, так и сигналы квитирования) для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта.

Цикл записи данных состоит из следующих фаз:

1. Программа выполняет цикл записи (IOWR#) в порт 4 (ЕРР Data Port).

2. Адаптер устанавливает сигнал Writeff (низкий уровень), и данные помещаются на выходную шину LPT-порта.

3. При низком уровне WAIT# устанавливается строб данных.

4. Порт ждет подтверждения от ПУ (перевода WAIT# в высокий уровень).

5. Снимается строб данных — внешний ЕРР-цикл завершается.

6. Завершается процессорный цикл ввода/вывода.

7. ПУ устанавливает низкий уровень WAIT#, указывая на возможность начала следующего цикла.

Главной отличительной чертой ЕРР является выполнение внешней передачи во время одного процессорного цикла ввода/вывода. Это позволяет достигать высоких скоростей обмена (0,5-2 Мбайт/с). Периферийное устройство, подключенное к параллельному порту ЕРР, может работать на уровне производительности устройства, подключаемого через слот ISA. Периферийное устройство может регулировать длительность всех фаз обмена с помощью всего лишь одного сигнала WAIT#. Протокол автоматически подстраивается и под длину кабеля — вносимые задержки только приведут к удлинению цикла.

«ЗАВИСАНИЕ» процессора на шинном цикле обмена препятствует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс.

С программной точки зрения контроллер ЕРР-порта выглядит достаточно просто (см. табл.7). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно базового адреса порта, добавлены два регистра (ЕРР Address Port и ЕРР Data Port), чтение и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено, что обеспечивает совместимость ЕРР-порта с периферийными устройствами и программным обеспечением, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления CR биты 0, 1 и 3, соответствующие сигналам STROBES, AUTOFEEDS и SELECTING, должны иметь нулевые значения. В противном случае программное вмешательство может нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты (ЕРР Protect), при включении которых программная модификация этих бит блокируется.

Использование регистра данных ЕРР позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSB или REP OUTSB вместо традиционных циклов с интенсивными операциями ввода/вывода. Некоторые адаптеры допускают и 16/32-битное обращение к регистру данных ЕРР. Тогда 16- или 32-битное обращение по адресу регистра данных ЕРР приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Таким образом при обмене данными и обеспечивается производительность, достигающая 2 Мбайт/с, вполне достаточная и для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы БРР всегда выполняются только в однобайтном режиме обращения.

Важной чертой ЕРР является то, что обращение процессора к периферийному устройству осуществляется в реальном времени. Программный драйвер всегда способен наблюдать состояние и подавать команды в точно известные моменты времени. Циклы чтения и записи могут чередоваться в произвольном порядке или идти блоками. Такой тип обмена наиболее пригоден для регистро-ориентированной периферии или периферии, работающей в реальном времени — сетевых адаптеров, устройств сбора информации и управления, дисковых устройств и т. п.

Режим ЕСР

Протокол ЕСР (Extended Capability Port — порт с расширенными возможностями) был предложен фирмами Hewlett Packard и Microsoft как прогрессивный режим связи с периферией типа принтеров и сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизводительный двунаправленный обмен данными хоста с периферийными устройствами.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

••• Циклы записи и чтения данных. Командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передача канальных адресов и счетчика RLC (Run-Length Count).

В отличие от ЕРР вместе с протоколом ЕСР сразу появился и стандарт на программную (регистровую) модель реализации его адаптера, изложенный в документе «The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard» компании Microsoft. Этот документ определяет специфические свойства реализации протокола, не заданные стандартом IEEE 1284: компрессия данных хост-адаптером по методу RLE;

••• буферизация FIFO для прямого и обратного каналов: применение DMA и программного ввода/вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия до 64:1 при передаче растровых изображений.

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере.

Как и в других режимах 1284, протокол ЕСР переопределяет сигналы SPP (табл. 8).

Таблица 8.

Сигналы LPT-порта в режиме ввода/вывода ЕСР

| Контакт |

Сигнал SPP |

Имя в ЕСР |

I/O |

Описание |

| 1 |

STROBE» |

HortClk |

0 |

Используется в паре с PeriphAck для передачи в прямом направлении (вывод) |

| 14 |

AUTOFEED# |

HostAck |

0 |

Индицирует тип команда/данные при передаче в прямом направлении. Используется в паре с PeriphClk для передачи в обратном направлении |

| 17 |

SELECTING |

1284Active |

О |

Высокий уровень указывает на обмен в режиме IEEE 1284. (В режиме SPP уровень низкий) |

| 16 |

INIT# |

ReverseRequest# |

О |

Низкий уровень переключает канал на передачу в обратном направлении |

| 10 |

ACK# |

PeriphClk |

I |

Используется в паре с HostAck для передачи в обратном направлении |

| 11 |

BUSY |

PeriphAck |

1 |

Используется в паре с HostClk для передачи в обратном направлении. Индицирует тип команда/ данные при передаче в обратном направлении |

| 12 |

PE |

AckReverse# |

I |

Переводится в низкий уровень как подтверждение сигналу ReverseRequestff |

| 13 |

SELECT |

Xflag* |

I |

Флаг расширяемости Extensibility flag |

| 15 |

ERROR» |

PeriphRequest#* |

I |

Устанавливается ПУ для указания на доступность (наличие) обратного канала передачи* |

| 2-9 |

Data[0:7] |

Data[0:7] |

I/O |

Двунаправленный канал данных |

* Сигналы действуют в последовательности согласования (см. ниже).

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действительность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Поскольку передачи в ЕСР разделены FIFO-буферами, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно будет считать переданными. Данные считается переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уровень на линии ReverseRequestff. 2 ПУ разрешает смену направления установкой низкого уровня на линии Ack-Reverse#.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действительность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

6. ПУ устанавливает высокий уровень линии PeriphClk, и этот перепад может использоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAck для указания на готовность к приему следующего байта.

Согласование режимов IEEE 1284

Периферийные устройства в стандарте IEEE 1284 обычно не требуют от контроллера реализации всех режимов, предусмотренных стандартом. Для определения режимов и методов управления конкретным устройством стандарт предусматривает последовательность согласования (negotiation sequence) для установки требуемого режима интерфейса.

Во время фазы согласования контроллер выставляет на линии данных байт расширяемости (Extensibility byte), запрашивая подтверждение на перевод интерфейса в требуемый режим или прием идентификатора периферийного устройства (табл. 11). Идентификатор передается контроллеру в запрошенном режиме (любой режим обратного канала, кроме ЕРР). ПУ использует сигнал Xflag (Select в терминах SPP) для подтверждения запрошенного режима обратного канала, кроме полубайтного. Полубайтный режим поддерживается всеми устройствами IEEE 1284. Бит Extensibility Link request заложен для механизма определения дополнительных режимов в будущих расширениях стандарта.

Таблица. 11.

Значение бит байта расширяемости

| Бит |

Описание |

Допустимые комбинации бит [7:0] |

| 7 |

Request Extensibility Link — запрос для будущих расширений |

1000 0000 |

| 6 |

Запрос режима ЕРР |

0100 0000 |

| 5 |

Запрос режима ЕСР с RLE |

ООН 0000 |

| 4 |

Запрос режима ЕСР Mode без RLE |

0001 0000 |

| 3 |

Резерв |

0000 1000 |

| 2 |

Запрос идентификатора устройства с ответом в режиме: |

|

| Nibble Mode (полубайтный) |

0000 0100 |

|

| Byte Mode (байтный) |

0000 0101 |

|

| ЕСР без RLE |

0001 0100 |

|

| ЕСР с RLE |

0011 0100 |

|

| 1 |

Резерв |

0000 0010 |

| 0 |

Запрос Byte Mode |

0000 0001 |

| None |

Запрос Nibble Mode |

0000 0000 |

Последовательность согласования состоит из следующих шагов:

1. Хост выводит байт расширяемости на линии данных.

2. Хост устанавливает высокий уровень сигнала Selecting и низкий — Auto-Feedft, что означает начало последовательности согласования.

3. ПУ 1284 ответит установкой низкого уровня сигнала Ackff и высокого — Errorft, РЕ и Select.

4. Хост устанавливает низкий уровень сигнала Strobeff для записи байта расширяемости в ПУ.

5. Хост устанавливает высокий уровень сигналов Strobeff и AutoFeedff.

6. ПУ отвечает установкой в низкий уровень сигналов РЕ и Errorff, если оно имеет обратный канал передачи данных. Если запрошенный режим поддерживается устройством, на линии Select устанавливается высокий уровень, если не поддерживается — низкий.

7. ПУ устанавливает высокий уровень на линии Ack# для указания на завершение последовательности согласования, после чего контроллер устанавливает требуемый (и разрешенный) режим работы.

Развитие стандарта IEEE 1284

Кроме основного стандарта IEEE 1284, который уже принят, в настоящее время в стадии проработки находятся новые стандарты, не отменяющие его, а определяющие дополнительные возможности. К ним относятся:

IEEE P1284.1 «Standard for Information Technology for Transport Independent Printer/Scanner Interface (TIP/SI)». Этот стандарт разрабатывается для управления и обслуживания сканеров и принтеров на основе протокола NPAP (Network Printing Alliance Protocol).

IEEE P1284.2 «Standard for Test, Measurement and Conformance to IEEE Std. 1284» — стандарт для тестирования портов, кабелей и устройств на совместимость с IEEE 1284.

IEEE P1284.3 «Standard for Interface and Protocol Extensions to IEEE Std-1284 Compliant Peripheral and Host Adapter Ports» — стандарт на драйверы и использование устройств прикладным программным обеспечением.

IEEE P1284.4 «Standard for Data Delivery and Logical Channels for IEEE Std. 1284 Interfaces». Этот стандарт направлен на реализацию пакетного протокола достоверной передачи данных через параллельный порт. Исходной точкой является протокол MLC (Multiple Logical Channels) фирмы Hewlett-Packard.

Конфигурирование LPT-портов

Управление параллельным портом разделяется на два этапа — предварительное конфигурирование (Setup) аппаратных средств порта и текущее (оперативное) переключение режимов работы прикладным или системным ПО. Оперативное переключение возможно только в пределах режимов, разрешенных при конфигурировании. Таким образом обеспечивается возможность согласования аппаратуры и программного обеспечения и блокирования ложных переключении, вызванных некорректными действиями программы.

Способ и возможности конфигурирования LPT-портов зависят от его исполнения и местоположения. Порт, расположенный на плате расширения (обычно на мультикарте), устанавливаемой в слот ISA или ISA+VLB, обычно конфигурируется джамперами на самой плате. Порт, расположенный на системной плате, обычно конфигурируется через BIOS Setup.

Конфигурированию подлежат следующие параметры:

Базовый адрес, который может иметь значение 3BCh, 378h и 278h. При инициализации BIOS проверяет наличие портов по адресам именно в этом порядке и, соответственно, присваивает обнаруженным портам логические имена LPT1, LPT2, LPT3. Адрес 3BCh имеет адаптер порта, расположенный на плате MDA или HGC. Большинство портов по умолчанию конфигурируется на адрес 378h и может переключаться на 278h.

Используемая линия запроса прерывания: для LPT1 обычно используется IRQ7, для LPT2 — IRQ5.

Использование канала DMA для режимов ЕСР и Fast Centronics — разрешение и номер канала DMA.

Использование параллельных портов

Наиболее распространенным применением LPT-порта является, естественно, подключение принтера. Практически все принтеры могут работать с портом в режиме SPP, но применение расширенных режимов дает дополнительные преимущества:

Двунаправленный режим (Bi-Di) дает дополнительные возможности для сообщения состояния и параметров принтера. Скоростные режимы (Fast Centronics) существенно повышают производительность практически любого принтера (особенно лазерного), но могут потребовать более качественного кабеля.

Режим ЕСР потенциально самый эффективный, и он имеет системную поддержку во всех вариантах Windows. Из распространенных семейств ЕСР поддерживают принтеры HP DeskJet моделей BXX, LaserJet начиная с 4-го, современные модели фирмы Lexmark требуют применения кабеля по частотным свойствам соответствующего IEEE 1284.

Простейший вариант кабеля подключения принтера — 18-проводный кабель с неперевитыми проводами с успехом может использоваться для работы порта в режиме SPP.

Идеальным вариантом являются кабели, в которых все сигнальные линии перевиты с общими проводами и заключены в общий экран — то, что требует IEEE 1248. Такие кабели гарантированно работают на скоростях до 2 Мбайт/с, и допускается их длина до 10 метров.

В табл. 12 приводится распайка кабеля подключения принтера с разъемом XI типа A (DB-25P) со стороны PC и Х2 типа В (Centronics-36) или типа С (миниатюрный) со стороны принтера.

Таблица 12. Кабель подключения принтера

| XI, разъем PC типа А |

Сигнал |

X2, |

разъем PRN типа В X2, разъем PRN типа С |

|

| 1 |

-Strobe# |

1 |

15 |

|

| 2 |

Data 0 |

2 |

6 |

|

| 3 |

Datal |

3 |

7 |

|

| 4 |

Data г |

4 |

8 |

|

| 5 |

Data3 |

5 |

9 |

|

| 6 |

Data 4 |

6 |

10 |

|

| 7 |

Data 5 |

7 |

11 |

|

| 8 |

Data 6 |

8 |

12 |

|

| 9 |

Data 7 |

9 |

13 |

|

| 10 |

AckS |

10 |

3 |

|

| 11 |

Busy |

11 |

1 |

|

| 12 |

PaperEnd |

12 |

5 |

|

| 13 |

Select |

13 |

2 |

|

| 14 |

Auto LF« |

14 |

17 |

|

| 15 |

Error» |

32 |

4 |

|

| 16 |

Imt# |

31 |

14 |

|

| 17 |

Sict In# |

36 |

16 |

|

| 18 |

GND(l) |

19 |

33 |

|

| 19 |

GND(2 3) |

20 21 |

24 25 |

|

| 20 |

GND(4 5) |

22 23 |

26 27 |

|

| 21 |

GND(6 7) |

24 25 |

28 29 |

|

| 22 |

GND(8 9) |

26 27 |

30 31 |

|

| 23 |

GND(11 15) |

29 |

19 22 |

|

| 24 |

GND(10 12 13) |

28 |

20 21 23 |

|

| 25 |

GND(14 16 17) |

30 |

32 34 35 |

|

Для связи двух компьютеров по параллельному интерфейсу применяются различные варианты кабелей, зависящие от режимов используемых портов. Самый простой способ (и самый медленный обмен) обеспечивает режим полубайтного обмена Nibble Mode, работающий на всех (исправных) портах. Для этого режима в кабеле достаточно иметь 10 сигнальных и один общий провод.

Высокоскоростная связь двух компьютеров может выполняться и в режиме ЕСР (режим ЕРР для этих целей неудобен, поскольку он требует синхронизации шинных циклов ввода/вывода двух компьютеров). В табл. 13 приведена распайка кабеля для этого режима. В ней в качестве вспомогательной информации приведены имена сигналов, которые аппаратно генерируются адаптерами портов. Этот же кабель может использоваться и для связи в режиме Byte Mode (при наличии двунаправленных портов). Связь компьютеров с помощью такого кабеля поддерживается Windows 95.

Таблица 13.

Кабель связи PC-PC в режиме ЕСР и Byte Mode

| Разъем XI |

Разъем Х2 |

||

| Контакт |

Имя в ЕСР |

Имя в ЕСР |

Контакт |

| 1 |

HostClk |

PeriphClk |

10 |

| 14 |

HostAck |

PeriphAck |

11 |

| 17 |

1284Active |

+PeriphRequest# |

15 |

| 16 |

Reverse Request^ |

AckReverse# |

12 |

| 10 |

PeriphClk |

HostClk |

1 |

| 11 |

PeriphAck |

HostAck |

14 |

| 12 |

AckReverse# |

ReverseRequest# |

16 |

| 13 |

Xflag |

- |

- |

| 15 |

PeriphRequestf» |

+284Active |

17 |

| 2-9 |

Data[0:7] |

Data [0:7] |

2-9 |

Подключение сканера к LPT-порту эффективно, только если порт обеспечивает хотя бы двунаправленный режим (Bi-Di), поскольку в основном здесь используется ввод. Но лучше использовать порт ECP, если этот режим поддерживается сканером.

Подключение внешних накопителей (lomega Zip Drive, CD-ROM), адаптеров ЛВС и других симметричных устройств ввода/вывода имеет общую специфику. Большинство таких устройств способно работать в любом из режимов порта (обычно исключая ECP), что обеспечивает их неограниченное применение на любых компьютерах.

Неисправности и тестирование параллельных портов

Тестирование параллельных портов целесообразно начинать с проверки их наличия в системе. Список адресов установленных портов обычно появляется в таблице заставки, выводимой BIOS на экран перед загрузкой ОС. Кроме этой таблицы, список можно посмотреть и с помощью тестовых программ или прямо в BIOS DATA AREA с помощью любого отладчика.

Если BIOS обнаруживает меньше портов, чем установлено физически, скорее всего, каким-либо двум портам присвоен один адрес. Программное тестирование порта без диагностической заглушки (Loop Back) не покажет ошибок, поскольку при этом читаются данные выходных регистров, а они у всех конфликтующих (по отдельности исправных портов) совпадут. Именно такое тестирование и производит BIOS при проверке на наличие портов. Разбираться с такой ситуацией имеет смысл последовательно устанавливая порты и наблюдая за адресами, появляющимися в списке.

Если физически установлен только один порт и его не обнаруживает BIOS, то либо он отключен при конфигурировании, либо вышел из строя скорее всего из-за нарушений правил подключения.

Тестирование портов с помощью диагностических программ позволяет проверить их выходные регистры, а при использовании специальных заглушек — и входные линии. Поскольку количество выходных линий порта (12) и входных (5) различно, то полная проверка порта с помощью пассивной заглушки принципиально невозможна. Разные программы тестирования требуют применения специально на них ориентированных заглушек (рис. 1),

Рис. 1. Схема заглушки для тестирования LPT-порта программой Checkit

Большинство неприятностей при работе с LPT-портами доставляют разъемы и кабели. Для проверки порта, кабеля и принтера можно воспользоваться специальными тестами из популярных диагностических программ (Checkit, PCCheck и т. п.), а можно вывести на принтер какой-либо символьный файл.

Если вывод файла с точки зрения DOS проходит (копирование файла на устройство с именем LPTn или PRN проходит быстро и успешно), а принтер (исправный) не напечатал ни одного символа — скорее всего, это обрыв (неконтакт в разъеме) цепи STROBES.

Если принтер по своему индикатору находится в состоянии On Line, a появляется сообщение о его неготовности (Not Ready Error), то причину следует искать в линии Busy.

Если принтер искажает информацию при печати, возможен обрыв (или замыкание) линий данных. В этом случае удобно воспользоваться файлом, содержащим последовательность кодов всех печатных символов (его можно создать с помощью простой программы, написанной даже на языке Basic, — ее текст приведен ниже).

10 OPEN "bincod.chr" FOR OUTPUT AS #1

20 FORJ=2T015

30 FOR 1=0 ТО 15

40 PRINT#1, CHR$(16*J+I);

50 NEXT I 60 PRINT#1,

70 NEXTJ

80 CLOSE #1

90 END

Файл BINCOD.CHR, созданный данной программой, представляет собой таблицу всех печатных символов (управляющие коды пропущены), расположенных по 16 символов в строке. Если файл печатается с повтором некоторых символов или их групп, по периодичности повтора можно легко вычислить оборванный провод данных интерфейса. Этот же файл удобно использовать для проверки аппаратной руссификации принтера.

Если принтер, подключенный к порту, в стандартном режиме (SPP) печатает нормально, а при переходе на ЕСР начинаются сбои, следует проверить кабель — соответствует ли он требованиям IEEE 1284. Кабели с неперевитыми проводами нормально работают на скоростях 50-100 Кбайт/с, но при скорости 1-2 Мбайт/с, обеспечиваемой ЕСР, они могут не работать, особенно при длине более 2 метров.

Если при установке драйвера РпР-принтера появилось сообщение о необходимости применения «двунаправленного кабеля», проверьте наличие связи контакта 17 разъема DB-25 с контактом 36 разъема Centronics.

Аппаратные прерывания от LPT-порта используются далеко не всегда. Неисправности, связанные с цепью прерывания от порта, проявляются не часто. Однако по-настоящему многозадачные ОС (например, сервер NetWare) стараются работать с портом именно по прерываниям. Тестировать линию прерывания можно, только подключив к порту периферийное устройство или специальную заглушку.

Параллельный порт и РпР

Большинство современных периферийных устройств, подключаемых к LPT-порту, поддерживает стандарт 1284 и функции РпР. Для поддержки этих функций компьютером с аппаратной точки зрения достаточно иметь контроллер интерфейса, поддерживающий стандарт 1284. Для работы РпР подключенное устройство должно сообщить операционной системе все необходимые сведения о себе (идентификаторы производителя, модели и набор поддерживаемых команд). Более развернутая информация об устройстве может содержать идентификатор класса, подробное описание и идентификатор устройства, с которым обеспечивается совместимость.