| Скачать .docx |

Реферат: Блок-схема вычитание чисел в форме плавающая точка, сдвиг вправо на один, два разряда

Московский Государственный Институт Радиотехники, Электроники, Автоматики

(Технический Университет)

Кафедра вычислительной техники

курсовой проект по теме

ПРОЕКТИРОВАНИЕ ВЫЧИСЛИТЕЛЬНОГО УСТРОЙСТВА

(на основе курса “Прикладная теория цифровых автоматов”)

Студент Лещинский И.

Вариант 16

Группа АВ-7-92

Преподаватель Антик М.И.

Москва

1995

СОДЕРЖАНИЕ

Задание 3

Интерфейс разрабатываемого устройства 3

Математические обоснования используемых алгоритмов 4

Примеры выполнения задач 5

Алгоритм работы вычислительного устройства 6

Микропрограмма в содержательном виде 7

Особенности работы некоторых узлов устройства 8

Описание сигналов управляющего автомата 9

Таблица заполнения управляющей памяти 10

Задание

Разработать вычислительное устройство, состоящее из двух взаимосвязанных частей: операционного и управляющего автоматов и выполняющее следующие операции с контролем:

1. Нахождение минимального в группе чисел (5)

2. Перевод правильной двоичной дроби в десятичную (3)

Контроль осуществляется разбиением данных на группы чисел по два двоичных разряда с последующим их суммированием по модулю три.

Числа 24-разрядные.

Суммарное число входных и выходных контактов - 30.

В задании используется управляющий автомат с естественной адресацией.

Ограничения:

1. В операционном автомате можно использовать не более двух сумматоров;

2. Управляющий автомат должен проектироваться с использованием ПЗУ.

Интерфейс разрабатываемого устройства

Исходя из задания, целесообразно использовать следующий интерфейс вычислителя.

Входные сигналы:

1. Сигнал SLCT - управляет выбором задачи; “0” - нахождение минимального в группе чисел, “1” - перевод правильной двоичной дроби в десятичную.

2. Сигнал ![]() -

обозначает готовность операнда; “0” - операнд готов, “1” - операнд не готов (используется в обеих задачах).

-

обозначает готовность операнда; “0” - операнд готов, “1” - операнд не готов (используется в обеих задачах).

3. Сигнал S/S - указывает вычислительному устройству на продолжение/конец последовательности чисел; “0”- последовательность не закончена, “1” - последовательность закончена (используется в первой задаче).

Выходные сигналы:

1. Сигнал ![]() - указывает на готовность вычислителя выполнять задачу; “0” - вычислитель готов, "1” - вычислитель не готов.

- указывает на готовность вычислителя выполнять задачу; “0” - вычислитель готов, "1” - вычислитель не готов.

2. Сигнал ![]() - указывает внешнему устройству на готовность ответа; “0”- ответ готов,”1”- ответ не готов.

- указывает внешнему устройству на готовность ответа; “0”- ответ готов,”1”- ответ не готов.

3. Сигнал ![]() - указывает внешнему устройству на наличие/отсутствие ошибки; “0” - ошибка есть, “1” - ошибки нет. Этот сигнал действует только при условии, что сигнал

- указывает внешнему устройству на наличие/отсутствие ошибки; “0” - ошибка есть, “1” - ошибки нет. Этот сигнал действует только при условии, что сигнал ![]() установлен в “0”. В остальных случаях

установлен в “0”. В остальных случаях ![]() установлен в “1”.

установлен в “1”.

Для передачи данных и результатов используется 24-разрядная двунаправленная шина данных. Установленный в “0” сигнал ![]() означает прием операнда, а установленный в “0” сигнал

означает прием операнда, а установленный в “0” сигнал ![]() выдачу результата. Оба эти сигнала не могут быть одновременно установлены в “0”.

выдачу результата. Оба эти сигнала не могут быть одновременно установлены в “0”.

Математические обоснования используемых алгоритмов

Рассмотрим принцип выполнения автоматом задач, указанных в задании.

1. Нахождение минимального числа из последовательно поступающих чисел.

Для определения минимального числа из двух чисел A и B необходимо вычислить разность A-B и по ее знаку сделать вывод о том, какое число является меньшим. Для этого A и B представляются в модифицированном дополнительном коде, причем устройство, передающее вычислителю эти операнды, представляет их в дополнительном коде, а далее, в операционном автомате у A знаковый разряд расширяется влево, разряды B инвертируются, полученный новый знаковый разряд расширяется влево, и к B добавляется “1”. Затем к полученному таким образом числу добавляется A ,и результат представляет собой разность A-B . Старший разряд говорит о знаке разности - “1” - разность отрицательная, следовательно A<B , “0” - разность положительная, то есть A>B . Равенство разности нулю говорит о равенстве A и B , при этом минимальным числом считается любое из них.

Значение второго после знакового разряда говорит о выходе разности за разрядную сетку операционного автомата, однако справедливость знака разности по-прежнему имеет место.

Таким образом, можно определить минимальное из двух целых чисел (положительных или отрицательных).

Далее операционный автомат ожидает поступление следующего числа и сравнивает его с уже имеющимся и т.д. пока не будет получен сигнал о завершении последовательности.

2. Перевод правильной двоичной дроби в десятичную

Здесь будем предполагать, что поступающее в операционный автомат число A представляет собой 24 разряда некоторой правильной двоичной дроби.

Под десятичной дробью будем понимать совокупность двоично-десятичных цифр в коде 8-4-2-1. Тогда для перевода необходимо проделать следующие действия:

1. Умножить число A на двоичное число 1010 (десятичное 10).

2. Запомнить старшие 4 разряда результата

3. Взять дробную часть результата и умножить ее на двоичное 1010

4. Повторить пункты 2-4 еще 23 раза.

23 раза повторять пункты 2-4, вообще говоря, необязательно. При 24-разрядной шине данных повторять данные операции можно лишь 6 раз (4X6=24). Однако для выполнения контроля данных по модулю 3 необходимо получить десятичную дробь со 100% точностью.

Примеры выполнения задач

Рассмотрим по одному примеру на выполнение каждой из задач.

1. Пусть вычислительное устройство принимает последовательность чисел, из которых необходимо найти минимальное.

1110’0010’1101’1110’1010’0001 (-1909087) число A

0001’0110’1111’0110’1010’1101 (1504941) число B

1010’1100’1110’0111’0011’1000 (-5445832) число C

Инвертируя B и расширяя знаковый разряд у A и B , операционный автомат вычисляет сумму:

1’1110’0010’1101’1110’1010’0001

1’1110’1001’0000’1001’0101’0010

0’0000’0000’0000’0000’0000’0001

1’1’1100’1011’1110’0111’1111’0100 = -3414028

Самая левая единица отбрасывается, следующая за ней единица говорит об отрицательности результата, что действительно верно. A<B и следующее число C будет сравниваться с числом A .

1’1110’0010’1101’1110’1010’0001

0’0101’0011’0001’1000’1100’0111

0’0000’0000’0000’0000’0000’0001

1’0’0011’0101’1111’0111’0110’1001 = 3536745

Как видим, результат получился положительным, следовательно A>C и следующее число будет сравниваться с C .

2. Пусть необходимо перевести в десятичное число двоичную дробь:0.1110’0010’1101’1110’1010’0001 (0.886209...). Отметим, что соответствующая десятичная дробь конечна.

Умножая на двоичное 1010 получим 1000.1101’1100’1011’0010’0100’1010, следовательно первая двоично-десятичная цира 1000 (8). Далее умножаем дробную часть на 1010. Получим 1000.1001’1110’1111’0110’1110’0100, следовательно вторая двоично-десятичная цифра - тоже 8. Еще раз умножим дробную часть полученного числа на 1010. Результат - 0110.0011’0101’1010’0100’1110’1000, и третья двоично-десятичная цира - 6 и т.д. Опреационный автомат будет вычислять результат, пока дробная часть множимого не станет нулевой. Первые 24 разряда полученного числа будут выданы на шину данных. Все 24X4=96 разрядов нужны для контроля данных по модулю три, однако запоминать 72 “лишних” разряда нет необходимости, так как узел, отвечающий за контроль, содержит сумматор с памятью.

Алгоритм работы вычислительного устройства.

Алгоритм состоит из двух основных ветвей. Левая - соответстветствует решению задачи о нахождении минимального числа, правая - задаче перевода двоичной дроби в десятичную. В данный алгоритм не входит описание поведения некоторых сигналов, о котрых будет сказано далее.

В алгоритме используются обозначения:

d1 d0 :=d1 d0 (X) - вычисление двух контрольных разрядов регистра X по модулю три. В регистре X находится исходный операнд;

d1 ’d0 ’:=d1 ’d0 ’(Y) - вычисление двух контрольных разрядов регистра Y по модулю три. В регистре Y находится промежуточный или конечный результат.

(d1 ’d0 ’)* - предыдущее значение контрольных разрядов результата.

d1 , d1 ’ - старший разряд, d0 , d0 ' - младший разряд двоичного числа от 0 до 2

В задаче нахождения минимума нулевой разряд A и B - младший, разряд № 23- старший. В задаче перевода дробей нулевой разряд старший, разряд № 3 (у A1 ) и разряд № 23 (у A2 и B ) - младший.

Микропрограмма в содержательном виде

Здесь действуют те же обозначения, что и в алгоритме.

g1 <<GO (SLCT; m1, m9)>>

m1 {![]() :=0;

:=0; ![]() :=1}

:=1}

g2 <<GO ( ![]() ; m2, g3)>>

; m2, g3)>>

g3 <<GO (S/S; g2, j1)>>

j1 <<GO (0; m8)>>

m2 {![]() :=1; A2[0-23]:=X[0-23]}

:=1; A2[0-23]:=X[0-23]}

m3 {d1d0:=d1d0(A2)}

m4 {![]() :=0}

:=0}

g4 <GO (![]() ; m5, g5)>>

; m5, g5)>>

g5 <<GO (S/S; m4, m20)>>

m20 {d1’d0’:=d1’d0’(A2)}

m8 {Y[0-23]:=A2[0-23]; ![]() :=0}

:=0}

j4 <<GO (0; g1)>>

m5 {![]() :=1; B[0-23]:=X[0-23]; (p,S)=A2[0-23]-B[0-23]}

:=1; B[0-23]:=X[0-23]; (p,S)=A2[0-23]-B[0-23]}

g6 <<GO (z; g5, g7)>>

g7 <<GO (p; m6, g5)>>

m6 {A2[0-23]:=B[0-23]}

m7 {d1d0:=d1d0(A2)}

j3 <<GO (0; g5)>>

m9 {![]() :=1; d1’d0’:=0,0; i:=0;

:=1; d1’d0’:=0,0; i:=0; ![]() :=0}

:=0}

g8 <<GO ( ![]() ; m10, g1)>>

; m10, g1)>>

m10 {![]() :=1; A1[0-3]:=0,0,0,0; A2[0-23]:=X[0-23]}

:=1; A1[0-3]:=0,0,0,0; A2[0-23]:=X[0-23]}

m11 {d1d0:=d1d0(A2)}

m12 {A1[3],A2[0-23]:=A2[0-23],0}

m13 {B[0-23]:=A1[3],A2[0-22]}

m14 {A1[2-3],A2[0-23]:=A1[3],A2[0-23],0}

m15 {A1[1-3],A2[0-23]:=A1[2-3],A2[0-23],0}

m16 {A1[0-3],A2[0-23]:=A1[1-3],A2[0-23]+0,0,B[0-23],0}

m17 {d1’d0’:=d1’d0’+(d1’d0’)* ; Y[4iј(4i+3)]:=A1[0-3]}

g9 <<GO (z1; m19, m18)>>

m18 {A1[0-3]:=0; i:=i+1}

j5 <<GO (0; m12)>>

m19 {![]() :=0}

:=0}

j6 <<GO (0; g1)

.....................................

j0 <<GO (0; g1)>>

Особенности работы некоторых узлов устройства

Так как разрабатываемое устройство представляется лишь на функциональном уровне необходимо указать особенности функционирования его некоторых узлов.

1. Для коммутации информационных данных будем использовать многоразрядные мультиплексоры шины. От обычных одноразрядных мультиплексоров они отличаются тем, что по определенному слову на адресных входах они коммутируют сразу несколько информационных сигналов с одного из многоразрядных входов на многоразрядный выход соответственно. По существу они представляют собой несколько обычных одинаковых одноразрядных мультиплексоров, адресные линии которых соответственно соединены. Мультиплексор MUX3 снабжен Z-входом, единичный уровень на котором вводит его в Z-состояние. Это необходимо для организации двунаправленной шины данных.

2. Для хранения данных целесообразно использовать многоразрядные регистры хранения. В задаче перевода дробей удобно хранение совместить с арифметическим сдвигом влево на один разряд. Для хранения данных используются регистры RGA1, RGA2, RGB, RG1-RG6. Регистры RGA1 и RGA2 снабжены также сдвиговым входом M и последовательным входом SI . По сигналу “0” на входе M данные в регистре последовательно сдвигаются влево от входа SI к старшим разрядам. Значение старшего разряда теряется.

3. В обеих задачах необходимо использовать операции суммирования. С этой целью в состав операционного автомата входят два многоразрядных сумматора.

Сумматор SM1 используется в задаче перевода дробей и способен выполнять сложение двух 27-разрядных операндов. Результатом сложения является 28-разрядное число. В условном обозначении сумматора SM1 разряды A0, B0, S0 - старшие, а разряды A26, B26, S27 - младшие.

Сумматор SM2 представляет собой устройство, выполняющее сложение двух 25-разрядных операндов и одноразрядного входа переноса cr . Результатом является также 25-разрядное число. Старший разряд при этом отбрасывается.

4. Шинный инвертор Ix24 служит для инвертирования 24 разрядной шины B .

5. В состав управляющего автомата входит инкрементор, выполненый на базе сумматора SM3. Младшие разряды входов и выхода имеют индекс 0.

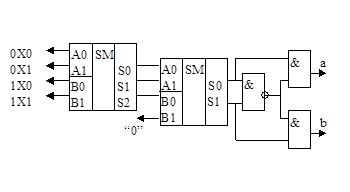

6. В схеме контроля данных по модулю три используется специальный сумматор SM4. Он суммирует 12 двухразрядных двоичных чисел по модулю три. Приведем принципиальную схему его фрагмента.

Здесь суммируются только два двоичных числа по модулю три. Подавая результат и следующее число на аналогичную схему получим сумматор трех двоичных двухразрядных чисел по модулю три и т.д.

Описание сигналов управляющего автомата

Для управления работой операционного автомата и схемы контроля данных по модулю три используется 17 управляющих сигналов, вырабатываемых с помощью управляющего автомата с естественной адресацией.

Сигналы A0-A2 обеспечивают коммутацию данных и промежуточных результатов, направляя их в регистры хранения.

Сигнал A3 - управляет коммутацией ответа; “0” - ответ задачи перевода дробей, “1”- ответ задачи о нахождении минимального числа.

Сигнал A4 - управляет коммутацией между операндами и схемой контроля.

Сигнал А5 - управляет сбросом контрольных разрядов d1 ’d0 ’.

Сигналы ![]() ,

, ![]() ,

, ![]() - “0” на этих линиях означает разрешение модификации регистров RGA1, RGA2, RGB. “1” запрещает модификацию.

- “0” на этих линиях означает разрешение модификации регистров RGA1, RGA2, RGB. “1” запрещает модификацию.

Сигнал ![]() - “0” разрешает модификацию выходных регистров RG1-RG6.

- “0” разрешает модификацию выходных регистров RG1-RG6.

Сигнал ![]() - “0” разрешает запоминание разрядов d1

d0

, “1” запрещает их модификацию

- “0” разрешает запоминание разрядов d1

d0

, “1” запрещает их модификацию

Сигнал ![]() - “0” разрешает запоминание разрядов d1

’d0

’, “1” запрещает их модификацию.

- “0” разрешает запоминание разрядов d1

’d0

’, “1” запрещает их модификацию.

Сигнал SANSWR

- “1” устанавливает линию ![]() в “0”, “0” устанавливает эту линию в “1”

в “0”, “0” устанавливает эту линию в “1”

Сигнал SRDY

- “1” устанавливет линию ![]() в “0”, “0” устанавливает эту линию в “1”

в “0”, “0” устанавливает эту линию в “1”

Сигнал ![]() - устанавливается в “0” для сброса счетстчика CT.

- устанавливается в “0” для сброса счетстчика CT.

Сигнал ![]() - устанавливается в “0” для разрешения сдвига в регистрах. Действителен при условии, что регистрам разрешена модификация.

- устанавливается в “0” для разрешения сдвига в регистрах. Действителен при условии, что регистрам разрешена модификация.

Сигнал INC - “1” разрешает увеличение значения счетчика CT на 1 при каждом тактовом импульсе.

Совокупность перечисленных сигналов представляет собой микрокоманду, исполнение которой проходит в три этапа.

1. Подготовка адреса микрокоманды. Это может быть адрес следующей микрокоманды или адрес некоторой другой микрокоманды, если имел место переход (условный или безусловный).

2. Подготовка самой микрокоманды. Микрокоманда запоминается в регистре микрокоманд RG10.

3. Исполнение микрокоманды. Сигналы управления передаются в операционный автомат и воздействуют на изменение его памяти и вычисление предикатов.

Выполняя один из этих этапов для любой микрокоманды, управляющий автомат одновременно выполняет предыдущий этап для следующей микрокоманды. Таким образом, операционный автомат никогда не “простаивает”, за исключением тех случаев, когда происходит условный или безусловный переход. На время перехода регистру микрокоманд запрещается модификация, а операционному автомату прекращается подача синхронизирующих импульсов, что способствует сохранению значений предиката и успешному выполнению перехода. После подготовки новой микрокоманды в RG10 синхронизация восстанавливается.

Таблица заполнения управляющей памяти

Для кодирования адреса понадобится 6 разрядов.

| адрес | метка | k | e A1 |

H2 A0 |

H1 A2 |

H0 A3 |

C5 A4 |

C4 A5 |

C3

|

C2

|

C1

|

C0

|

SANSWR | SRDY | INC | ||||

| 000000 | g1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | |||||||

| 000001 | m1 | 0 | 0 | 1 | |||||||||||||||

| 000010 | g2 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | |||||||

| 000011 | g3 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | |||||||

| 000100 | j1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | |||||||

| 000101 | m2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | |||||||||||

| 000110 | m3 | 0 | 0 | 1 | 0 | 0 | 0 | ||||||||||||

| 000111 | m4 | 0 | 1 | 1 | 0 | 1 | |||||||||||||

| 001000 | g4 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | |||||||

| 001001 | g5 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | |||||||

| 001010 | m20 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | |||||||||||

| 001011 | m8 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | |||||||||

| 001100 | j4 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| 001101 | m5 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | ||||||||||

| 001110 | g6 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | |||||||

| 001111 | g7 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | |||||||

| 010000 | m6 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | ||||||||||

| 010001 | m7 | 0 | 0 | 1 | 0 | 0 | 0 | ||||||||||||

| 010010 | j3 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | |||||||

| 010011 | m9 | 0 | 0 | 0 | 0 | 1 | 0 |

| адрес | метка | k | e A1 |

H2 A0 |

H1 A2 |

H0 A3 |

C5 A4 |

C4 A5 |

C3

|

C2

|

C1

|

C0

|

SANSWR | SRDY | INC | ||||

| 010100 | g8 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| 010101 | m10 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | ||||||

| 010110 | m11 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | ||||||||

| 010111 | m12 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | |||||||

| 011000 | m13 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | |||||

| 011001 | m14 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | ||||||

| 011010 | m15 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | ||||||

| 011011 | m16 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | |||

| 011100 | m17 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | ||||||

| 011101 | g9 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |||||||

| 011110 | m18 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | ||||||

| 011111 | j5 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | |||||||

| 100000 | m19 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | |||||||||||

| 100001 | j6 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| ............. | ........ | ||||||||||||||||||

| 111111 | j0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

По последнему адресу в ПЗУ записана команда безусловного перехода на нулевой адрес. Это сделано с целью организации сброса устройства по сигналу ![]() .

.