| Похожие рефераты | Скачать .docx |

Реферат: Исследование двоичных счетчиков

Министерство общего и профессионального образования Российской Федерации

Уральский государственный технический университет

ИССЛЕДОВАНИЕ ДВОИЧНЫХ СЧЕТЧИКОВ

Екатеринбург 2009

Исследование двоичных счетчиков

1. ТЕОРЕТИЧЕСКАЯ ЧАСТЬ

Счетчики

Счетчиком называют устройство, сигналы, на входе которого в определенном коде отображают число импульсов, поступивших на счетный вход. Триггер Т-типа может служить примером простейшего счетчика. Такой счетчик считает до двух. Счетчик, образованный цепочкой из m-триггеров, сможет посчитать в двоичном коде 2m импульсов. Каждый из триггеров цепочки называют разрядом счетчика. Число m определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число Ксч =2m называют коэффициентом (модулем) счета.

Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свое состояние, т. е. Счетчик запоминает число сосчитанных импульсов.

Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом.

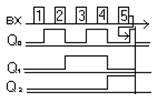

После каждого цикла счета на выходах последнего триггера возникают перепады напряжения. Это свойство определяет второе назначение счетчиков: Деление числа входных импульсов. Если входные сигналы периодичны и следуют с частотой fвх , то частота выходных импульсов будет fвых =fвх /Ксч

У счетчиков в режиме деления используется выходной сигнал только последнего триггера, промежуточные состояния остальных триггеров не учитываются. Всякий счетчик может быть использован как делитель частоты. Поэтому подобное устройство часто называют счетчиком-делителем. Такие делители имеют целочисленный коэффициент деления. Элементная база современной микроэлектроники позволяет строить делители и с дробным коэффициентом деления.

Символом счетчиком на схемах служат буквы СТ (от англ. counter – счетчик). Если требуется, после символа проставляют число, характеризующее модуль счета, например СТ2 .

Основные эксплуатационные показатели: емкость и быстродействие.. Емкость счетчика, численно равная коэффициенту счета, характеризует число импульсов, доступное счету за один цикл.

Быстродействие счетчика определяется разрешающей способностью tразр.сч и временем установки кода счетчика. Под разрешающей способностью подразумевают минимальное время между двумя входными сигналами, в течение которого еще не возникают сбои в работе счетчика.

Обратная величина fmax =1/tразр. сч называется максимальной частотой счета. Время установки кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое устойчивое состояние. Временные свойства зависят от временных характеристик триггеров и способа их соединения между собой.

Классификация счетчиков.

Цифровые счетчики классифицируются следующим образом:

По коэффициенту счета: двоичные(бинарные); двоично-десятичные (декадные) или с другим основанием счета; с произвольным постоянным модулем; с переменным модулем.

По направлению счета: суммирующие; вычитающие; реверсивные.

По способу организации внутренних связей: с последовательным переносом; с параллельным переносом; с комбинированным переносом; кольцевые.

Для двоичного счетчика с Ксч =2m , зная номера триггеров и состояния выходов Q, можно определить записанное в счетчик двоичное число

М=Qm * 2m-1 +Qm-1 *2m-2 +…+Q1 *20 ,

где m-номер триггера, 2m-1 – вес m-ного разряда.

Введением дополнительных логических связей – обратных и прямых – двоичные счетчики могут быть обращены в недвоичные, для которых Ксч ¹2m . Наибольшее распространение получили десятичные (декадные) счетчики, работающие с привычным Ксч =10. Десятичный счет осуществляется в двоично-десятичном коде (двоичный по коду счета, десятичный – по числу состояний).

Десятичные счетчики организуются из четырехразрядных двоичных счетчиков. Избыточные шесть состояний исключаются введением дополнительных связей.

Возможны 2 варианта построения схем: а) счет циклически идет от 0000 до 1001 и б) исходным состоянием служит 01102 =610 и счет происходит до 11112 =1510 . Первый вариант применяют чаще.

В суммирующем счетчике каждый входной импульс увеличивает число, записанное в счетчик, на 1. Как следует из таблицы, перенос информации из одного разряда в другой, более высокий, имеет место, когда происходит смена состояния с 1 на 0.

Вычитающий счетчик действует обратным образом: двоичное число, хранящееся в счетчике, с каждым поступающим импульсом уменьшается на 1. Переполнение вычитающего счетчика происходит после достижения им нулевого состояния. Перенос из младшего разряда в старший здесь имеет место при смене состояния младшего разряда с 0 на 1.

| N состояния |

Состояние суммирующего счетчика |

N состояния |

Состояние вычитающего счетчика |

||||

| Q3 |

Q2 |

Q |

Q3 |

Q2 |

Q1 |

||

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1¯ |

7 |

1 |

1 |

1 |

| 2 |

0 |

1¬ |

0 |

6 |

1 |

1 |

0 |

| 3 |

0 |

1 |

1 |

5 |

1 |

0¬ |

1¯ |

| 4 |

1¬ |

0¯ |

0 |

4 |

1 |

0 |

0 |

| 5 |

1 |

0 |

1 |

3 |

0¬ |

1¯ |

1 |

| 6 |

1 |

1 |

0 |

2 |

0 |

1 |

0 |

| 7 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Эти счетчики имеют дополнительные входы для задания направления счета. Режим работы определяется управляющими сигналами на этих входах. Имеются счетчики и с отдельными входами для суммирования и вычитания.

Когда счетчик используется в качестве делителя, направление счета не играет роли.

Счетчики с последовательным переносом – цепочка триггеров, в которой импульсы, подлежащие счету, поступают на вход 1 триггера, а сигнал переноса передается последовательно от одного разряда к другому. В этих счетчиках используются асинхронные Т-триггеры с прямым либо с инверсным управлением, а также JK- и D-триггеры в счетном режиме. Главное достоинство счетчиков с последовательным переносом – простота схемы. Увеличение разрядности (наращивание) осуществляется подключением нужного числа триггеров к выходу последнего триггера. Поскольку входные сигналы поступают на вход только первого триггера, такой счетчик мало нагружает предшествующий каскад.

Основной недостаток счетчиков с последовательным переносом – сравнительно низкое быстродействие, поскольку триггеры здесь срабатывают последовательно, один за другим. Другой недостаток, обусловленный этой же причиной, состоит в том, что из-за накопления временных сдвигов в разрядах на выходах дешифраторов таких счетчиков могут появляться кратковременные ложные импульсы, особенно заметные на высоких частотах.

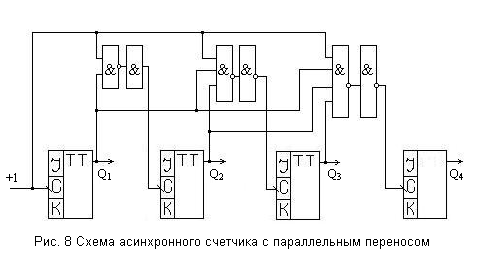

Счетчики с параллельным переносом состоят из синхронных триггеров. Счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующим только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, и задержка переключения всего счетчика равна задержке переключения для одного триггера. Счетчики с параллельным переносом широко применяются в быстродействующих устройствах.

Счетчики – делители, оформленные как самостоятельные изделия, имеются в составе многих серий микросхем. Номенклатуру счетчиков отличает большое разнообразие. Многие из них обладают универсальными свойствами и позволяют управлять коэффициентом и направлением счета, вводить до начала цикла исходное число, прекращать счет по команде, наращивать число разрядов и т. п.

Счетчики с коэффициентом счета Ксч =2m представляют собой последовательную цепочку из m триггеров.

С помощью дополнительного логического элемента можно изменять Ксч (деления) в пределах 2m-1 <Kсч <2m , для чего входы ЛЭ подключаются к выходам определенных триггеров, а его выход – ко входам R принудительной установки триггеров в нулевое состояние, а иногда и ко входам S – установки в "1".

Работу такого счетчика рассмотрим на примере счетчика с Ксч =5. Для получения такого Kсч достаточно 3-х триггеров. Из таблицы состояний видно, что после 5-го импульса счетчик будет иметь состояние 101. Чтобы организовать обратную связь и исключить лишние импульсы путем сброса счетчика в исходное состояние. Подадим на 3-х входовый элемент И-НЕ три высокие уровня со всех трех триггеров.

Только в этом случае ячейка совпадения единиц И-НЕ даст "0" на выходе, который и сбросит триггер в исходное состояние.

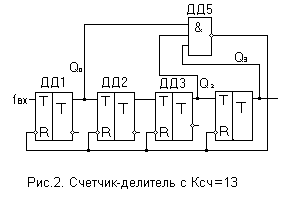

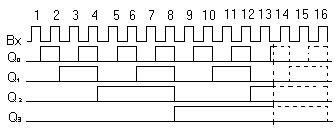

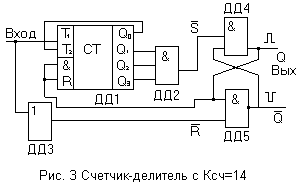

Другой пример счетчика с Ксч =13. Первый триггер срабатывает от каждого входного импульса, т.е. 1=20 ; второй – от каждого 2-го импульса (2=21 ); третий – от четвертых импульсов (4=22 ); а четвертый триггер – от каждого восьмого импульса (8=23 ). Коэффициенту счета Ксч =13=8+4+1=1*23 +1* 22 +0*21 +1* 20 соответствуют, следовательно, состояния Q3 =Q2 =Q0 =1. За цикл счета ДД5 сработает только 1 раз. Выходной сигнал ("0") с ДД5 подается на R-входы всех триггеров, в том числе и на 2-й триггер. Сделано это для того, чтобы исключить ложное срабатывание ДД2 после перехода ДД1 в нулевое состояние, т.к. этот перепад после 13-го импульса подобен полезному сигналу. Проектирование счетчика сводится к определению числа триггеров, виду логического элемента, организации связей между триггерами и ЛЭ.

Счет |

Q3 |

Q2 |

Q1 |

Q0 |

Счет |

Q3 |

Q2 |

Q1 |

Q0 |

| 0 |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

| 1 |

0 |

0 |

0 |

1 |

9 |

1 |

0 |

0 |

1 |

| 2 |

0 |

0 |

1 |

0 |

10 |

1 |

0 |

1 |

0 |

| 3 |

0 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

| 4 |

0 |

1 |

0 |

0 |

12 |

1 |

1 |

0 |

0 |

| 5 |

0 |

1 |

0 |

1 |

13 |

1 |

1 |

0 |

1 |

| 6 |

0 |

1 |

1 |

0 |

14 |

1 |

1 |

1 |

0 |

| 7 |

0 |

1 |

1 |

1 |

15 |

1 |

1 |

1 |

1 |

Рассмотренные счетчики имеют коэффициент счета Ксч = 5 и Ксч = 13 т.е. выходной сигнал счетчика будет после 5-го или 13-го импульса (выходным сигналом является перепад с "1" на "0") – переход с "1" на "0" сигнала Q2 .

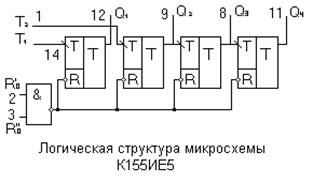

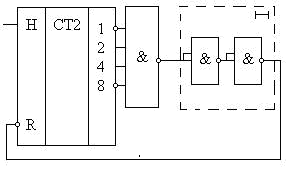

Если нужен не переход, а импульс, то его можно получить с помощью схем формирования импульсов или других схем. Одну из таких схем рассмотрим далее на базе К155ИЕ5, логическая схема которого представлена на рисунке:

| R¢0 |

R²0 |

Режим |

| 0 |

0 |

Счет |

| 0 |

1 |

|

| 1 |

0 |

|

| 1 |

1 |

Прекращение счета Q1 =Q2 =Q3 =Q4 =0 |

Когда счетчик используется в качестве делителя частоты, то, немного усложнив схему, можно получить на выходе кратковременные импульсы вместо обычного перепада напряжения.

Схема формирования кратковременного импульса на выходе МС К155ИЕ5 (Кдел =14) представлена на рисунке.

Установка нуля счетчика происходит в этом случае через триггер ДД4, ДД5. С приходом следующего входного импульса триггер возвращается в исходное состояние.

Реверсивный счетчик.

Импульсы, поступающие для счета, попадают на вход 1-го триггера, а выходят с него по двум каналам: при прямом счете с прямого выхода, а при обратном – с инверсного. Для того, чтобы управлять путями движения, служат элементу И-НЕ. Такие ячейки ставятся после каждого триггера. Управляющим сигналом для прямого и обратного счета являются логические нули.

Так, если на входах элементов ДД4.1 и ДД4.4 нули, то они заблокированы, а логические единицы на их выходах никакого влияния на работу элементов ДД4.2 и ДД5.1 не оказывают.

Аналогично с шиной +1. Происходит движение импульса при прямом счете. Пусть на шине –1 высокий потенциал – логическая "1", а на +1 – логический "0", исходное состояние счетчика 000. Первый импульс срезом переводит младший разряд в "1" (т.е. на выходе 8 ДД1 будет "1"). На выходе ДД4.1 появится "0", а на выходе ДД4.2 – высокий потенциал. На входе ДД2 высокий потенциал изменения состояния ДД2 не вызовет, т.е. после 1-го импульса счетчик будет в состоянии 001. Следующим импульсом ДД1 перебросится в "0", ДД4.1- в "1", ДД4.2 – в "0" и ДД2 – в "1", ДД4.4 – в "0", ДД5.1 – в "1", т.е. счетчик будет в состоянии 010 и т.д.

Аналогично при вычитании: на шине –1 – логический "0", на шине +1 – логическая "1", на выходах ДД4.1 и ДД4.4 – логическая "1", исходное состояние счетчика 111. Импульсы проходят по нижним ячейкам.

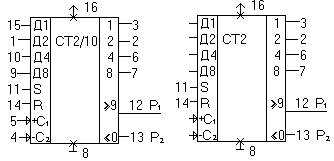

Среди большого многообразия МС счетчиков можно выделить 155ИЕ6 и 155ИЕ7 – двоично-десятичный и двоичный четырех разрядные реверсные счетчики.

Входы С1 и С2 для подачи счетных импульсов, R – для установки в "0", S – для предварительной записи информации (S="0") установленной триггерами по спадам Р1 на С1 след МС при прямом счете (при переходе из 9 в 0), "перенос" Р2 – при обратном счете ( при переходе из 0 в 9), выход "займа".

Кольцевой счетчик.

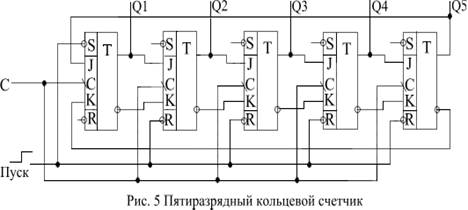

Кольцевой счетчик представляет собой регистр, у которого информационный вход триггеров D-типа (или оба входа JK- или RS-триггеров в случае их применения) соединен с выходом (или с обоими выходами) последней ступени, образуя замкнутое кольцо.

Если в один из разрядов регистра ввести логическую единицу или ноль, то эта единица или ноль с каждым тактовым импульсом будет переходить от триггера к триггеру с циклом, равным числу триггеров. Поскольку состояние всех триггеров регистра, за исключением одного, одинаково, активное состояние этого разряда однозначно характеризует число входных тактовых импульсов с учетом, естественно, числа циклов.

На рис. 5 показана логическая структура пятиразрядного кольцевого счетчика.

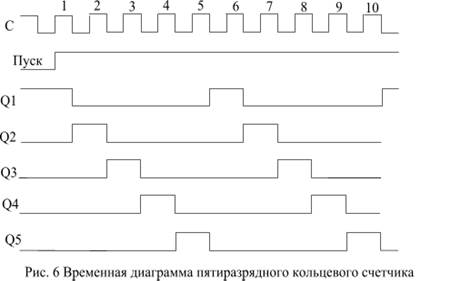

На рис. 6 показана его временная диаграмма.

Кроме RS (JK)-триггеров в таких схемах применяют также и D-триггеры. В последнем случае инверсные выходы триггеров не используются. До начала работы наряду с вводом логической 1 в первый разряд остальные триггеры устанавливаются в ноль, поскольку состояние, которое они примут в момент включения питания, непредсказуемо.

В отличие от двоичных счетчиков преобразование последовательности импульсов в требуемый код (например, восьмеричный или десятичный) здесь обеспечивается без помощи дешифратора, что является преимуществом кольцевых счетчиков. Каждый из выходов приходит в активное состояние с частотой fвых =fвх /m, где m-число триггеров, т.е. коэффициент счета кольцевого счетчика численно равен числу триггеров. Поскольку кольцевые счетчики не содержат внешних логических элементов, они обладают большим быстродействием.

Кольцевым счетчикам свойственно два недостатка.

Первый – повышенный расход триггеров и соответственно большие экономические и энергетические затраты. Так, например, для кольцевого счетчика с коэффициентом счета 16 потребуется 16 триггеров, в то время как для двоичного счетчика достаточно четырех.

Второй – вероятность сбоев. Если под действием помех произойдет ошибочный переброс отдельных триггеров, то такое состояние, раз возникнув, само не исправится. Этот недостаток устраняют введением корректирующей логической цепи, следящей за состоянием триггеров. При появлении ложных сигналов на вход подаются импульсы, исправляющие положение в новом цикле.

2. ЦЕЛЬ РАБОТЫ

2.1 Изучение работы двоичных счетчиков, экспериментальное исследование графа переходов счетчика

2.2 Исследование быстродействия счетчиков и способов его повышения

|

3. ДОМАШНЕЕ ЗАДАНИЕ

3.1 Ознакомиться с заданием на проведение эксперимента

3.2 Изучить по литературе и по теоретической части двоичные счетчики

3.3 Изобразить в тетради для отчетов схемы изучаемых счетчиков

(рис. 1, 2, 3,4,5,7,8,9,10) и развернутую принципиальную схему счетчика, соответствующую рис. 11.

3.4 Продумайте методику исследования времени перехода десятичного счетчика из состояния 1001 в состояние 0000.

4. ЗАДАНИЕ НА ПРОВЕДЕНИЕ ЭКСПЕРИМЕНТА

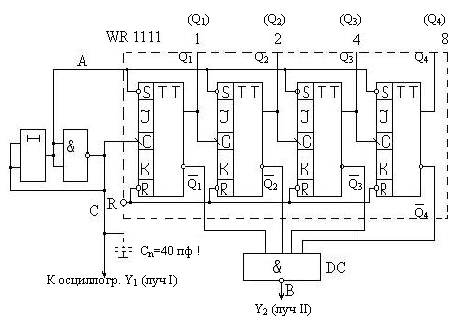

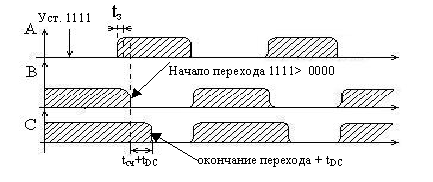

4.1 Собрать двоичный асинхронный счетчик с последовательным переносом (рис. 7). Экспериментально исследовать граф перехода счетчика. Определить время перехода счетчика из состояния 1111 в состояние 0000.

Для этого используется схема, показанная на рис. 7. Последовательность импульсов с выхода А рециркуляционного генератора подается на шину установки счетчика в состояние 1111. Эта установка является инверсной (в соответствии со свойствами триггера 155ТВ1) и производится уровнем «0» (рис. 7, б).

При наличии сигнала установки ( А = 0 ) все триггеры счетчика заблокированы и не реагируют на счетные импульсы шины С.

Для нормальной работы счетчика необходимо убрать сигнал установки 1111, т. е. сделать А = 1.

Тогда, через некоторое время tз , обусловленное инерционностью триггеров, счетчик восстановит свою работоспособность. Поэтому сигнал запуска счетчика С снимается с инверсного входа рециркуляционного генератора, что обеспечивает задержку запускающего перепада 1 – 0 относительно момента снятия сигнала установки А (момент начала «разблокирования» счетчика). Величина этой задержки tз зависит от емкости, подключенной к шине С (величина емкости должна быть не менее 40 пФ – в работе используется входная емкость осциллографа). При этом под воздействием перепада 1 – 0 на шине С счетчик начинает совершать переход в состояние 0000.

Момент окончания перехода регистрируется по изменению сигнала на выходе дешифратора DC (c инверсным входом) состояния 0000, выполненного на схеме «И-НЕ».

Инерционность дешифратора будет увеличивать регистрируемое время перехода на величину Δt.

Регистрация времени осуществляется с помощью двухлучевого осциллографа. Последовательно отсоединяя сигналы от входов схемы дешифратора, определить зависимость времени переходов от числа разрядов счетчика.

Рис. 7: а) схема асинхронного счетчика с последовательным переносом (обведена пунктиром) и схема для исследования времени перехода. б) эпюры напряжений A, B, C рисунка а)

Рис. 11 схема одного из вариантов десятичного счетчика

4.2 Собрать счетчик с параллельным переносом (рис. 8) и провести исследования, такие же как в предыдущем пункте.

4.3 Собрать синхронный двоичный счетчик (рис. 9) и провести исследования, такие же как в п.4.1

4.4 Собрать двухразрядный реверсивный счетчик (рис. 10). Исследовать граф переходов. Определить время перехода из состояния 1001 в состояние 0000.

5. Требования к отчету

Отчет должен содержать выполненное домашнее задание, графы переходов исследуемых счетчиков, принципиальные схемы счетчиков, результаты эксперимента и выводы.

6. Контрольные вопросы

1. Какие типы двоичных счетчиков Вы знаете?

2. Чем определяется быстродействие счетчика?

3. Какие способы повышения быстродействия счетчиков Вы знаете?

4. Что такое граф перехода?

5. Что такое функция перехода?

7. список литературы

1. Е.А. Зельдин. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л. ЭАИ. 1986, 280 с.

2. В.Л. Шило. Популярные цифровые микросхемы. Справочник. М. РиС. 1987, 352 с.

3. Й. Янсен. Курс цифровой электроники. М. Мир. 1987, в 4-х томах

4. В.А. Прянишников. Электроника. Курс лекций. СП6 [A1] ,: «Корона принт» 1998, 400 с

[A1] Последняя буква (или цифра) не разборчива

Похожие рефераты:

Билеты на государственный аттестационный экзамен по специальности Информационные Системы

Разработка схемы блока арифметико-логического устройства для умножения двух двоичных чисел

Автоматизация измерений, контроля и испытаний

Основы анализа и синтеза комбинационных логических устройств

Методы позиционирования и сжатия звука

Техническая диагностика средств вычислительной техники